# IMPROVED SIC SCHOTTKY BARRIER DIODES USING REFRACTORY METAL BORIDES

By

Rani S. Kummari

Submitted in Partial Fulfillment of the Requirements

for the Degree of

Master of Science in Engineering

in the

**Electrical Engineering**

Program

YOUNGSTOWN STATE UNIVERSITY

December 2009

# Improved SiC Schottky Barrier Diodes Using Refractory Metal Borides

## Rani S Kummari

| I hereby release this thesis to the public. I understand that this thesis will be ma      | ıde |

|-------------------------------------------------------------------------------------------|-----|

| available from the Ohio LINK ETD Center and the Maag library Circulation Desk             | for |

| public access. I also authorize the University or other individuals to make copies of the | his |

| thesis as needed for scholarly research.                                                  |     |

|                                                                                           |     |

| Rani S Kummari, Student  Approvals:  Dr. Tom N Oder, Thesis Advisor  Dr. Jalal Jalali, Committee Member  Dr. Philip C. Munro, Committee Member  Date | Signature | :                                                                   |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------|------|

| Dr. Jalal Jalali, Committee Member Date                                                                                                              |           | Rani S Kummari, Student                                             | Date |

| Dr. Jalal Jalali, Committee Member Date                                                                                                              | Approval  | s:                                                                  |      |

|                                                                                                                                                      |           | Dr. Tom N Oder, Thesis Advisor                                      | Date |

| Dr. Philip C. Munro, Committee Member Date                                                                                                           |           | Dr. Jalal Jalali, Committee Member                                  | Date |

|                                                                                                                                                      |           | Dr. Philip C. Munro, Committee Member                               | Date |

| Peter J. Kasvinsky, Dean of School of Graduate Studies & Research Date                                                                               |           | Deter I. Verringler, Deep of School of Conducts Studies 9, December | Dota |

#### **ABSTRACT**

This research demonstrates how the deposition temperature of Schottky contacts on 4H-SiC affects the electrical and thermal properties of a Schottky diode. Several refractory metal borides are investigated for the contacts which are deposited at room temperature (20 °C) and high temperature (600 °C). The electrical properties of the diodes are characterized by using current-voltage (I-V) and capacitance-voltage (C-V) measurements. Thermal properties are investigated by using rapid thermal processor (RTP). Schottky contacts which are deposited at 600 °C produced better Schottky diodes with smaller ideality factors (from 1.05 to 1.10), barrier heights from 0.94 to 1.15 eV, smaller resistances, and smaller current density in reverse bias conditions when compared to the contacts deposited at room temperature. These values remained stable after annealing in RTP at 600° C for 20 minutes. The improved electrical properties and thermal stability of the diodes with contacts deposited at 600 °C are related to the removal of O<sub>2</sub> from the boride/SiC interface, as revealed by the Rutherford backscattering spectroscopy (RBS) analysis. These results indicate improved electrical and thermal properties of boride/SiC Schottky contacts, making them attractive for high temperature applications.

#### ACKNOWLEDGEMENT

I have worked with many people while writing this thesis who have contributed in many different ways, and it is my pleasure to express my gratitude and thank all of them.

First, I would like to convey my gratitude to my supervisor and advisor Dr. Tom N. Oder for his guidance from the very inception of my research. His constant support has encouraged me throughout the process. Most of all, his passion for the science and his in-depth knowledge have inspired me as a student. I am confident that I will benefit from his guidance for a long time to come. I am indebted to him more than he knows.

I gratefully thank Dr. Jalal Jalali for his supervision and encouragement throughout the construction of this thesis. I thank him for his valuable comments.

I gratefully acknowledge Dr. Philip C. Munro for his valuable advice, supervision, generous donation of time in reading this thesis, and his provision of critical comments on my work.

My parents, sisters and brother deserve a special mention for their support, encouragement and prayers.

Many thanks to my friends Looja, Lin and Tony Solic, who supported, encouraged and helped me whenever I needed.

Finally, I thank each and every person that contributed to the success of this thesis.

## TABLE OF CONTENTS

| ABSTRACT                                                       | iii  |

|----------------------------------------------------------------|------|

| ACKNOWLEDGEMENT                                                | iv   |

| TABLE OF CONTENTS                                              | v    |

| TABLE OF FIGURES                                               | viii |

| LIST OF TABLES                                                 | xi   |

| LIST OF SYMBOLS:                                               | xii  |

| CHAPTER ONE                                                    | 1    |

| INTRODUCTION                                                   | 1    |

| 1.1 History of SiC and Refractory Metal Borides                | 2    |

| 1.2 Theory and Operation of a Schottky Diode                   | 6    |

| 1.2.1 Current-Voltage (I-V) Characterization                   | 10   |

| 1.2.2 The On-Resistance (R <sub>on</sub> )                     | 14   |

| 1.2.3 The Current-Voltage-Temperature (I-V-T) Characterization | 14   |

| 1.2.4 The Capacitance-Voltage Characterization                 | 15   |

| CHAPTER TWO                                                    | 18   |

| SCHOTTKY DIODE FABRICATION                                     | 18   |

| 2.1 Preparing SiC Substrate and Ohmic Contacts                 | 18   |

| 2.2 The Schottky Contacts                                      | 20   |

| 2.3 Patterning the Schottky Contact                            | 21   |

| CHAPTER THREE                                                           | 25      |

|-------------------------------------------------------------------------|---------|

| EFFECT OF DEPOSITION TEMPERATURE USING I-V MEASUREMENTS                 | 25      |

| 3.1 Previous Work with ZrB <sub>2</sub>                                 | 25      |

| 3.2 I-V Characterization                                                | 28      |

| 3.3 Measurement and Analysis of the Contacts in Reverse Bias            | 33      |

| 3.4 Determination of the Specific on-Resistance                         | 34      |

| 3.5 Results from I-V-T Measurements                                     | 35      |

| CHAPTER FOUR                                                            | 41      |

| EFFECT OF DEPOSITION TEMPERATURE USING C-V CHARACTERIZATION             | ON. 41  |

| 4.1 Testing Method for C-V Characterization                             | 44      |

| 4.2 Sheet Resistance Measurements                                       | 47      |

| CHAPTER FIVE                                                            | 50      |

| DICUSSION ON THE RESULTS                                                | 50      |

| CHAPTER SIX                                                             | 54      |

| CONCLUSION AND RECOMMENDATION FOR FUTURE WORK                           | 54      |

| 6.1 Conclusion on Temperature Deposition                                | 54      |

| 6.2 Recommendation for Future Studies                                   | 55      |

| APPENDICES                                                              | 56      |

| Appendix 1: Calculation of Ideality Factor and Barrier Height for the C | ontacts |

| Deposited at Room Temperature using I-V Method                          | 56      |

|   | Appendix 2: Calculation of Ideality Factor and Barrier Height for the Contacts         |

|---|----------------------------------------------------------------------------------------|

|   | Deposited at High Temperature using I-V Method                                         |

|   | Appendix 3: Calculation of the Barrier Height and Doping Concentration for the         |

|   | Contacts Deposited at Room Temperature using C-V Method                                |

|   | Appendix 4: Calculation of the Barrier Height and Doping Concentration for the         |

|   | Contacts Deposited at High Temperature using C-V Method                                |

|   | Appendix 5: Calculation of the Current Density for the Contacts Deposited at Room      |

|   | Temperature. 62                                                                        |

|   | Appendix 6: Calculation of the Current Density for the Contacts Deposited at High      |

|   | Temperature. 62                                                                        |

|   | Appendix 7: Calculation of the Series Resistance after Annealing at 600 °C for the     |

|   | Contacts Deposited Room Temperature                                                    |

|   | Appendix 8: Calculation of the Series Resistance for the Contacts Deposited 600 °C. 64 |

| R | EFERENCES65                                                                            |

### **TABLE OF FIGURES**

| Fig. 1. Energy band gap of M-S before contact                                                      |

|----------------------------------------------------------------------------------------------------|

| Fig. 2. Energy band gap of M-S after contact and before thermal equilibrium 8                      |

| Fig. 3. Energy band diagram of an M-S contact in thermal equilibrium                               |

| Fig. 5. Schottky contact depletion Region                                                          |

| Fig. 6. Silicon carbide with an ohmic contact on the back side                                     |

| Fig. 7. (a) Plasma sputter deposition chamber and (b) the sputter targets                          |

| Fig. 8. Plasma deposition process                                                                  |

| Fig. 9. (a) UV mask liner and (b) spin coater                                                      |

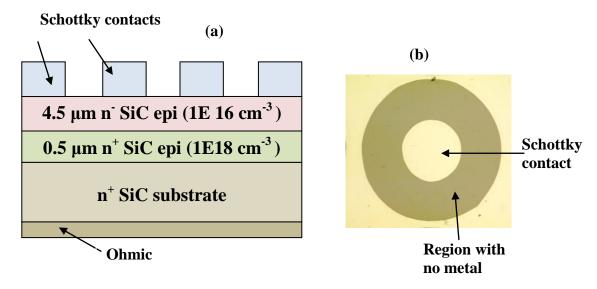

| Fig. 10. (a) Final Schottky diode structure and (b) Top view showing the Schottky contact          |

|                                                                                                    |

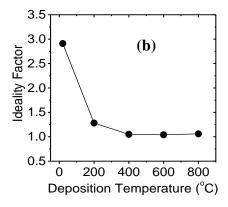

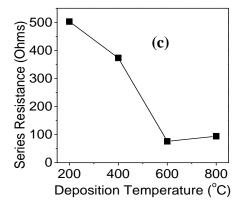

| Fig. 11. Results from Schottky diodes made with ZrB <sub>2</sub> contacts deposited at different   |

| temperatures showing variation of (a) the barrier height, (b) the ideality factor and (c) the      |

| series resistance                                                                                  |

| Fig. 12. Rutherford backscattering spectra of ZrB <sub>2</sub> films deposited on SiC at different |

| temperatures. The inset shows an expanded view of the spectra showing the decrease of              |

| the O <sub>2</sub> peak with deposition temperature. 27                                            |

| Fig. 13. (a) Keithley source meter (b) samples on a copper plate                                   |

| Fig. 14. Current- voltage data for the borides deposited at 20 °C and 600 °C. (a) shows the        |

| plot with both I and V on linear scales and (b) shows the plot with I on a log scale while         |

| V is on a linear scale                                                                             |

| Fig. 15. Semilog I-V plot from diodes made with WB Schottky contacts deposited at 20               |

| °C before annealing and after annealing at 600 °C/20 min in N <sub>2</sub>                         |

| Fig. 16. Current- voltage plot of diodes with the WB deposited at 600 °C before (as                         |

|-------------------------------------------------------------------------------------------------------------|

| deposited) and after annealing at 600 °C for 20 min in N <sub>2</sub>                                       |

| Fig. 17. Values of the ideality factor for the refractory metal borides                                     |

| Fig. 18. Values of the Schottky barrier heights for the refractory metal borides                            |

| Fig. 19. I-V plots of W <sub>2</sub> B contact diodes deposited at 20 °C and 600 °C                         |

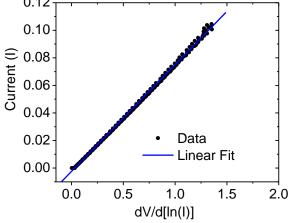

| Fig. 20 A plot of current I versus dV/d[ln(I)] of a W <sub>2</sub> B contact deposited at 600 °C 34         |

| Fig. 21. Current density versus voltage plots in 25 °C increments                                           |

| Fig. 22. I-V at measuring temperatures 25 °C and 250 °C                                                     |

| Fig. 23. (a) Richardson and (b) modified Richardson plot                                                    |

| Fig. 24. Temperature versus ideality plot using IVT measurements                                            |

| Fig. 25. Temperature versus barrier height plot using IVT measurements                                      |

| Fig. 26. Schottky diode with bias                                                                           |

| Fig. 27. (a) 1/C <sup>2</sup> versus V and (b) C versus V                                                   |

| Fig. 28. 1/C <sup>2</sup> -V plots of diodes with W <sub>2</sub> B contact deposited at 20 °C and 600 °C 43 |

| Fig. 29. (a) Agilent precision LCR meter (b) samples on copper substrate (c) samples or                     |

| isolated container                                                                                          |

| Fig. 30. C-V Plot for W <sub>2</sub> B/SiC deposited at 600 °C                                              |

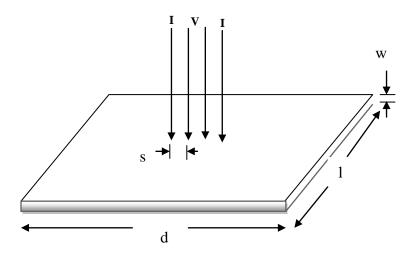

| Fig. 31. Four point-point probe measurement setup                                                           |

| Fig. 32. Microscopic view of the four-point probes                                                          |

| Fig. 33. Set up of four-probes on the film                                                                  |

| Fig. 34. Current-Voltage plots for diodes with the contacts deposited at 20 °C and 600 °C                   |

| showing (a) the linear I-V plots and (b) the linear portions of the semilog I-V plots 50                    |

| Fig. 35. Current-Voltage plots for WB diodes with the contacts deposited at 600             | °C |

|---------------------------------------------------------------------------------------------|----|

| showing no change even following annealing in $N_2$ at 600 $^{\circ}\text{C/20}$ min        | 50 |

| Fig. 36. W <sub>2</sub> B <sub>5</sub> contact deposited at 20 °C                           | 56 |

| Fig. 37. W <sub>2</sub> B <sub>5</sub> contact deposited at 600 °C                          | 57 |

| Fig. 38. W <sub>2</sub> B contacts after annealing where the contact was deposited at 20 °C | 63 |

| Fig. 39. W <sub>2</sub> B contact deposited at 600 °C                                       | 64 |

## LIST OF TABLES

| Table 1. Comparison of SiC with Si [6-12]                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------|

| Table 2. Some properties of the borides                                                                                         |

| Table 3. Richardson Constants obtained for CrB <sub>2</sub> /SiC contacts                                                       |

| Table 4. Schottky contacts deposited at 20 $^{\circ}\text{C}$ (a) measured from 25 $^{\circ}\text{C}$ to 250 $^{\circ}\text{C}$ |

| (b)measured back from 250 °C to 25 °C                                                                                           |

| Table 5. Schottky contacts deposited at 600 $^{\circ}$ C (a) measured from 25 $^{\circ}$ C to 250 $^{\circ}$ C 40               |

| Table 6. Sheet resistance of the film deposited at 20 °C and 600 °C                                                             |

| Table 7. Summary of the results. (Values outside the bracket are for diodes with as-                                            |

| deposited boride contacts and those inside the brackets are obtained after the diodes were                                      |

| annealed inN2 using RTP at 600 °C/20 min).                                                                                      |

#### LIST OF SYMBOLS:

A Area of the diode

A\* Richardson constant (cm<sup>-2</sup>K<sup>-2</sup>)

E<sub>v</sub> Valence band energy level (eV)

E<sub>C</sub> Energy level of the conduction band (eV)

E<sub>F</sub> Fermi level Energy (eV)

$E_{F, M}$  Fermi level of the metal (eV)

E<sub>G</sub> Band gap energy (eV)

E<sub>i</sub> Intrinsic energy level (eV)

E<sub>vacuum</sub> Energy of the free electron (eV)

I<sub>0</sub> Saturation current (A)

I<sub>F</sub> Forward current (A)

J Current density (A-cm<sup>-2</sup>)

k Boltzmann constant (J/K)

K<sub>s</sub> Dielectric constant

n Ideality factor

N<sub>A</sub> Acceptor doping concentration (holes/cm<sup>3</sup>)

N<sub>D</sub> Donor doping concentration (electrons/cm<sup>3</sup>)

q Electron charge (Coulombs)

$R_{on}$  On resistance (Ω-cm2)

$R_s$  Sheet resistance  $(\Omega)$

T Temperature in Kelvin (K)

V<sub>a</sub> Applied bias voltage (V)

$V_{bi}$  Built- in potential (eV)

W Width of the depletion region (cm)

$\varepsilon_0$  Permittivity of the material (F/m)

$\chi \qquad \qquad \text{Electron affinity (eV)}$

$\Phi_{B}$  Schottky Barrier Height (eV)

$\Phi_{m}$  Metal work function (eV)

$\Phi_s$  Semiconductor work function (eV)

#### **CHAPTER ONE**

#### INTRODUCTION

In today's technology everyone is interested in high power and high temperature devices. The development and improvement of hybrid vehicles, electric vehicles and fuel cell hybrid vehicles is a major effort by the automotive industries to meet the challenge for reduction in fuel consumption and emission of greenhouse gases. Key performances for the next generation are high breakdown voltage, low on-resistance, high current operation and high temperature operation up to 300 °C [1, 2]. Schottky diodes are discrete devices with special functions in high power electronics and other integrated circuitry; they are basic building blocks for many transistors such as IGBJTs, MOSFETs etc. Due to their high frequency behavior, Schottky barrier diodes (as opposed to pn-junction diodes) are being extensively used in different applications such as high frequency switches, gas sensors, mixers, microwave circuits and UV detectors [3, 4].

This research demonstrates how the deposition temperature of Schottky contacts improves SiC Schottky barrier diodes for high power and high temperature applications. Schottky contacts are deposited at room temperature (20 °C) and high temperature (600 °C). Several refractory metal borides are investigated for the Schottky contacts. The diodes are characterized by using current-voltage (I-V) and capacitance-voltage (C-V) measurements.

Background information of SiC and refractory metal borides is provided. Theory and operation of Schottky diodes, and fabrication technique, and wet etching process are

discussed. The effect of deposition temperature on the fabrication process and analysis of these diodes are provided.

#### 1.1 History of SiC and Refractory Metal Borides

#### SiC:

Silicon carbide (SiC) was first mentioned by Jons Jacob Berzelius in 1824, and its formation was confirmed by Eugene and Alfred Cowes in 1885 [5]. It does not occur naturally on earth, although it occurs in meteorites. In 1955, Lely introduced a new method of growing this material in the laboratory, and the current method used is a modification of this, now referred to as the modified Lely technique. This breakthrough led to the formation in 1987, of Cree, Inc, the first commercial supplier of SiC. SiC is part of a family of materials which exhibit a one-dimensional polymorphism called polytypism. The difference among the polytypes is in the arrangement of layers of Si and C. In SiC, Si and C are bonded tetrahedrally. Over 200 polytypes of SiC are known to exist. The polytypes are divided into three basic crystallographic categories; cubic (C), hexagonal (H), and rhombohedral (R) [6]. Some of the common polytypes includes 3C, 2H, 4H, 6H, 8H, 9R, 10H, 14H, 15R, 19R, 20H, 21H, and 24R. With the exception of 2H and 3C, all of the polytypes form one-dimensional super lattice structures.

Cubic SiC only one possible polytype, and is referred as 3C-SiC or β-SiC. In 3C-SiC, each SiC bi-layer can be oriented into only three possible positions with respect to the lattice while the tetrahedral bonding is maintained. If these three layers are denoted by A, B, and C and the stacking sequence is ABCABC..., then the crystallographic structure is cubic zinc blende. If the stacking of the bi-layers is ABAB..., then the

symmetry is hexagonal and referred to as 2H-SiC. All of the other SiC polytypes are a mixture of the zinc blende (cubic) and wurtzite (hexagonal). 4H-SiC consists of an equal number of cubic and hexagonal bonds. 6H-SiC is composed of two-thirds cubic bonds and one-third hexagonal bonds [6].

SiC is a wide gap semiconductor and this property of SiC yields electronic devices of superior power. Silicon carbide was one of the earliest semiconductors discovered and has strong bonds of silicon and carbon which makes the silicon carbide strong and hard.

Silicon carbide is not attacked by any acids up to 800°C. SiC based devices have higher breakdown voltages than the Si based devices—up to 5 to 30 times higher than the Si based devices. SiC devices are thinner and they have low on-resistance compared to the Si based devices. SiC is extremely radiation hard, meaning radiation does not degrade the electronic properties of SiC to a great extent.

In high temperatures (above 150 °C) operation, Si devices stops working due to the increased leakage current, but SiC can withstand high temperature [4]. One reason for 4H-SiC to withstand high temperature is because it has a higher band gap. The band gap of the 4H-SiC is 3.2 eV, and it can withstand up to 1200 °C. Relative conductance, breakdown field, and thermal conductivity of the 4H-SiC are greater than the Si which is shown in Table 1. Because of all the properties shown in Table 1, SiC is ideal for developing electronic circuits for high power, high temperature and high frequency applications. Under these circumstances, conventional semiconductors such as silicon (Si) and gallium arsenide (GaAs) are unable to function efficiently [7]. From the Baliga's figure of merit (relative Z<sub>B</sub>) 4H-SiC is 2500 times better than the conventional Si

semiconductor for high power and high temperature applications, which is shown in Table 1 (highlighted rows). In Table 1, 4H-SiC properties are highlighted to compare with the other semiconductors.

Table 1. Comparison of SiC with Si [6-12]

| Property                                                               | Si   | GaAs | 6H-  | 4H-  | GaN  |

|------------------------------------------------------------------------|------|------|------|------|------|

|                                                                        |      |      | SiC  | SiC  |      |

| Band gap (eV)                                                          | 1.1  | 1.4  | 3    | 3.2  | 3.4  |

| Max. Temp. (°C)                                                        | 300  | 460  | 1000 | 1200 | 600  |

| Electron Mobility (300K, cm <sup>2</sup> /V-s)                         | 1500 | 8500 | 370  | 800  | 900  |

| Hole Mobility (300K, cm <sup>2</sup> /V-s)                             | 450  | 400  | 101  | 115  | 50   |

| Relative Conductance (λ)                                               | 1    | 7.8  | 15   | 90   | 650  |

| Breakdown field (E <sub>b</sub> , 10 <sup>6</sup> V/cm)                | 0.3  | 0.4  | 3.2  | 3    | 3.3  |

| Thermal Conductivity (σ, W/cm-°C)                                      | 1.5  | 0.5  | 4.9  | 3.7  | 1.3  |

| Sat. electron drift velocity (v <sub>s</sub> , 10 <sup>7</sup> cm/sec) | 1    | 1    | 2    | 2    | 2.5  |

| Dielectric Constant (K)                                                | 11.9 | 13.1 | 10.3 | 10.3 | 9    |

| Relative $Z_J \sim (E_b v_s)^2$ (pwr/freq)                             | 1    | 7    | 250  | 200  | 750  |

| Relative $Z_K \sim \sigma(v_s/K)^{1/2}$ (speed)                        | 1    | 0.5  | 5    | 5    | 2    |

| Relative $Z_B \sim \sigma \lambda E_b$ (pwr/high temp)                 | 1    | 2.6  | 400  | 2500 | 6200 |

Consequently, a great deal of research effort has recently focused on wideband gap semiconductor materials, leading to the development of new electronic device structures with remarkable performance. One such device is the Schottky barrier diode (SBD), which if based on SiC would have faster switching speed, large blocking voltage, and function more reliably at higher temperatures, making it very attractive for high power applications. Due to their attractive high frequency behavior, Schottky barrier diodes are being extensively used in different applications such as mixers and detectors, and are actually the most progressed SiC power devices already commercially available. Schottky barrier diodes, along with several other key microelectronic devices such as photo detectors, sensors, and hetero-junction field effect transistors, employ a Schottky

contact where its thermal stability becomes a very important factor at a high input power level. However, the SiC Schottky diodes currently on the market are available up to 1200 V/20 A and are rated for operations only up to 175 °C. Contacts that remain stable up to a target temperature of 500 °C would ensure reliability especially in high temperature applications such as the propulsion systems where engine case temperatures can reach 600 °C [7].

In this research, I worked with 4H-SiC which has a higher band gap compared to the 6H-SiC as shown in Table 1. 4H-SiC was purchased from Cree, Inc., (http://www.cree.com) and it consisted of a low resistive n-type substrate with two n-type epilayers. The epilayers were grown 8° off to the basal (0001) plane of the substrate. The heavily doped n<sup>+</sup> epilayer was first grown on top of the substrate, followed by growth of the lightly doped n<sup>-</sup> epilayer.

#### **Refractory Metal Borides and Their Properties:**

Boron reacts with many metals in the periodic table to from a wide variety of metal boride compounds. The strong covalent bonding of most borides is responsible for their high melting points and hardness. Most borides are excellent electric conductors with low electrical resistance values [13]. The borides of the high-melting point metals of the fourth, fifth, and sixth periodic groups have properties that render them potentially valuable in very high-temperature structural applications. The high melting metal borides and carbides are about the only refractories suited for use at temperatures around 2500 °C and above because of their nonvolatility. The refractory metal borides W<sub>2</sub>B<sub>5</sub>, W<sub>2</sub>B, WB, TiB<sub>2</sub>, HfB<sub>2</sub>, CrB<sub>2</sub> and ZrB<sub>2</sub> are found to be stable in the presence of carbon [14].

The borides are of no value where an electrically insulating refractory is required because of their conductivity. However, they can be heated inductively or by self-resistance. They make excellent radiation shields because of their high reflectivity and low volatility. The high temperature hardness of the borides is such that they are suitable for high temperature use under abrasive conditions. Because of the three-dimensional boron frameworks, boron-boron bonding results in a lattice of high stability through which the valence electrons, and at high temperatures the metal atoms themselves, can diffuse readily. Such compounds have desirable thermionic emission properties [14].

Refractory metal borides have properties such as very high hardness, very high melting points, and excellent chemical resistance yet very low electrical resistance, making them very attractive as contact metallization for high temperature device applications with the SiC materials. Table 2 shows some properties of the metal borides.

Table 2. Some properties of the borides

| Boride           | Lattice<br>Const. (°A) | Melting Point (°C) | Thermal Expansion Coeff. (x10 <sup>-6</sup> K <sup>-1</sup> ) | Elec. Res. $(\mu\Omega\text{-cm})$ |

|------------------|------------------------|--------------------|---------------------------------------------------------------|------------------------------------|

| $ZrB_2$          | 3.17                   | 3220               | 5.9                                                           | 4.6 (Zr = 42)                      |

| CrB <sub>2</sub> | 2.97                   | 2200               | 10.5                                                          | 21                                 |

| $TiB_2$          | 3.03                   | 2600               | 4.6                                                           | 28 (Ti = 40)                       |

| $W_2B_5$         | 3                      | 2860               | 7.8                                                           | 19                                 |

| $HfB_2$          | 3.14                   | 3250               | 5.5                                                           | 11 (Hf = 30)                       |

|                  |                        |                    |                                                               |                                    |

#### 1.2 Theory and Operation of a Schottky Diode

The Schottky diode is named after Walter H. Schottky who played a major role in developing the Schottky effect in Schottky diodes. The Schottky diode is a semiconductor diode which has a very low turn-on voltage, approximately 0.15 to 0.45 V

compared to p-n junction diodes. Forward current in a Schottky diode is due to majority carrier injection from the semiconductor to the metal. Reverse current is also due to majority carriers that overcome the Schottky barrier and this is very dependent on temperature. The Schottky diode has fast switching action, and switching speed is controlled by thermalization of hot injected doping carriers of semiconductors across the junction. The switching speed of a Schottky diode will occur in few picoseconds [15].

The semiconductor material used in the research was 4H-SiC with n-type doping. The Schottky diode has two different metal contacts on a semiconductor, a Schottky (rectifying) contact and an ohmic contact. Metal to semiconductor contacts are important since they are present in every semiconductor device. A metal to semiconductor contact can behave as a Schottky barrier or as an ohmic contact depending upon the characteristics of the interface. A metal can be characterized by a work function  $(\Phi_m)$ , the minimum energy required to move an electron from the metal to the vacuum level.

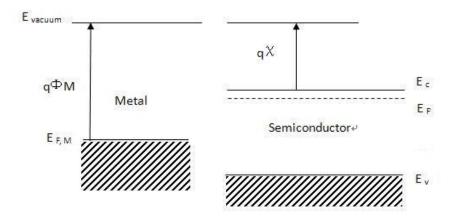

The barrier between the metal and semiconductor can be identified on an energy band diagram. In an energy band diagram, metal and semiconductor are aligned using the same vacuum level as shown in Fig. 1 and Fig. 2. When the metal and semiconductor are brought together there will be a barrier established between the metal and semiconductor interface. This barrier height  $\Phi_B$  is the energy required to free up an electron from metal  $(\Phi_m)$  minus the energy required to remove the electron from n-type semiconductor material (called electron affinity,  $\chi$ ) which is given by Eq. 1.1 [15].

$$\Phi_{\rm B} = \Phi_{\rm m} - \chi \tag{1.1}$$

Barrier height is measured in the eV and the electron affinity for 4H-SiC is 4.17 eV.

Fig. 1. Energy band gap of M-S before contact

Fig. 2. Energy band gap of M-S after contact and before thermal equilibrium

Whenever metal and semiconductor align together, only a small number of electrons have the energy to get over the barrier and cross to the metal. When a bias voltage is applied to the junction, it can have two effects: it can make the barrier appear lower from the semiconductor side, or it can make it appear higher. The bias does not change the barrier from the metal side. When the barrier is large, the electrons need more

energy to cross the barrier and the contact has rectifying behavior also called Schottky contact. When the barrier is small, electrons can move freely from the semiconductor to the metal and the contact is called ohmic contact. The ohmic behavior is indicated by a linear current-voltage characteristic.

Experimental barrier height often differs from the calculated barrier height due to the chemical reactions between the metal and the semiconductor. The cleaning procedure used and the ideal metal-semiconductor theory assumes both the materials are pure, and that there is no interaction between the two materials and no unwanted interfacial layer [15].

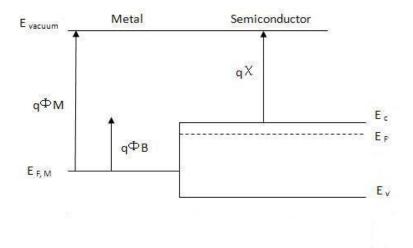

Electrons in the n-type semiconductor can lower energy by traversing the junction. As electrons leave the semiconductor, a positive charge stays behind due to the ionized donor atoms. Electrons flow into the metal until equilibrium is reached between the diffusion of electrons from the semiconductor into the metal and the drift of electrons caused by the field created by ionized impurity atoms. This equilibrium is called thermal equilibrium and it is characterized by a constant Fermi level throughout the structure as shown in Fig. 3. Under thermal equilibrium with no external voltage applied, there is a region in the semiconductor close to the junction which is depleted of mobile carriers; this is called depletion region [15]. The built-in potential, the applied voltage, and the doping concentration play a large role in the width of the depletion region.

Fig. 3. Energy band diagram of an M-S contact in thermal equilibrium

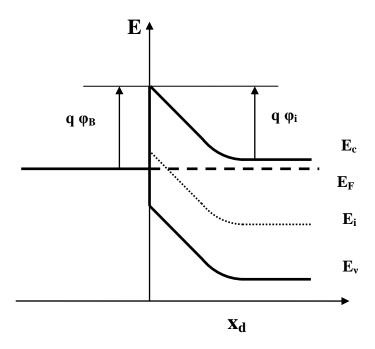

When a forward-bias voltage  $V_a$  is applied to the Schottky barrier, the contact potential will be reduced by  $qV_a$ . As a result, electrons in the semiconductor conduction band diffuse across the depletion region to the metal. This gives rise to a forward current. Conversely, a reverse bias increases the barrier and the electron flow from semiconductor to metal is negligible [16].

#### 1.2.1 Current-Voltage (I-V) Characterization

Current flows in a Schottky barrier diode because charge transfers from the semiconductor to the metal or vice versa. The four basic mechanisms by which carrier transportation can occur are:

1) Thermionic emission over the energy barrier

- 2) Tunneling through the barrier

- 3) Carrier recombination or generation in the depletion region

- 4) Carrier recombination in the natural region of the semiconductor

Thermionic emission is the dominant mechanism in Schottky barrier junctions. The thermionic emission is derived from the assumption that the barrier height ( $\phi_B$ ) is much larger than kT. Thermal equilibrium established at the junction determines emission and the existence of a net current flow. At the junction, there are two currents, one flow from the metal to the semiconductor and the other flows from the semiconductor to the metal. The current flow depends on the barrier height. In thermionic emission theory, the effect of drift and diffusion in the depletion region is assumed to be negligible [8, 17]. Therefore, the standard thermionic emission relation for electron transport from the metal to the semiconductor with low doping concentration is given by Eq. 1.2a:

$$I_{F} = I_{O} \exp \left( \frac{q(V_{a} - IR_{S})}{nkT} \right) \left[ 1 - \exp \left( \frac{-q(V_{a} - IR_{S})}{kT} \right) \right]$$

(1.2a)

$I_0$  is the reverse saturation current which is dependent on the barrier  $\varphi_B$  for electron injection from the metal into the semiconductor and is given by

$$I_{O} = AA * T^{2} exp\left(\frac{-q\Phi_{B}}{kT}\right)$$

(1.2b)

where  $I_F$  is the forward current, A = area of the Schottky contact,  $\varphi_B$  = Zero bias Schottky barrier height,  $A^*$  = Richardson constant,  $R_S$  = series resistance, k = Boltzmann constant and n = ideality factor.

The barrier is unaffected by the applied bias voltage. Under negligible series resistance and high bias  $(3kT/q << V_a << IR_S)$ , the forward current simplifies to Eq. 1.3

$$I_{F} = I_{O} exp\left(\frac{qV_{a}}{nkT}\right)$$

(1.3)

From the forward bias current equation Schottky diodes behave as rectifiers with easy current flow in the forward direction and little current in the reverse direction. Fig. 4 shows the energy band diagram of the metal semiconductor junction under forward and reverse biased conditions.

Fig. 4. Energy band diagram of (a) forward biased (b) reverse biased M-S junction

The depletion width is also dependent on the high doping density. High doping concentration makes a thin depletion width and promotes more tunneling. The depletion width is given by Eq. 1. 4.

$$W = \sqrt{\frac{2\varepsilon(V_{bi} - V_a)}{N_D}} \tag{1.4}$$

Where W= Width of the depletion region

$V_{bi} = Built-in potential.$

$V_a$  = Applied voltage.

$N_D$  = Doping concentration.

$\varepsilon = permittivity$

Taking natural logs of both sides of Eqn. (1.3) gives

$$Ln(I_F) = Ln(I_O) + \frac{q}{nkT} V_a$$

(1.5)

From eq. (1.2b), we get

$$\operatorname{Ln}(I_{O}) = \operatorname{Ln}(AA * T^{2}) - \frac{q}{kT} \Phi_{B}$$

(1.6)

From the Eq. 1.4, the plot of  $ln(I_F)$  versus the applied voltage  $V_a$  gives a straight line whose slope is q/nkT and intercept is  $ln(I_0)$ . From this current-voltage (I-V) characterization, the ideality factor (n) can be determined from the slope and the barrier height  $(\varphi_B)$  can be determined from the intercept and by using Eq. 1.5.

#### 1.2.2 The On-Resistance (R<sub>on</sub>)

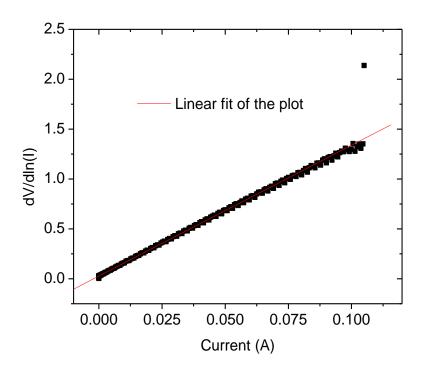

The specific on-resistance  $(R_{on})$  of the diode is an important parameter for high efficiency power devices. In this study, on-resistance was obtained by first determining the series resistance  $R_s$  of the diode for the non-linear region of the  $ln(I_F)$  versus  $V_a$  plot.

For V >> 3kT/q, Eq. (1.2a) simplifies to

$$I = AA * T^{2} exp \left(\frac{-q\Phi_{B}}{kT}\right) exp \left[\frac{q(V - IR_{S})}{nkT}\right]$$

(1.7)

where now  $I_F$  is represented by I and  $V_a$  is represented by V. Eq. (1.6) can be rearranged to give

$$I = \frac{1}{R_s} \left[ \frac{dV}{d \ln Q} - \left( \frac{kT}{q} \right) \left( \frac{n}{R_s} \right) \right]$$

(1.8)

By plotting current (I) against dV/d[ln(I)], the series resistance is obtained from the reciprocal of the slope of the linear section of the graph or from the intercept. The on-resistance ( $R_{on}$ ) is determined by multiplying series resistance with the area of the diode.

#### 1.2.3 The Current-Voltage-Temperature (I-V-T) Characterization

In this research, the current-voltage-temperature (I-V-T) measurements were performed to find out the barrier height, the Richardson constant (A\*), and the characteristic energy ( $E_{oo}$ ) from which the dominant mechanism for the current conduction can be deduced. I-V measurements were performed in the dark at different temperatures ranging from 25 °C to 250 °C in steps of 25 °C. The sample was glued to a heated stage whose temperature was monitored by a thermocouple and the I-V

measurements were performed using the Keithley Sourcemeter. From Eq. (1.2b), the saturation current  $(I_o)$  is expressed as

$$I_{O} = AA * T^{2} exp \left( \frac{-q\Phi_{B}}{kT} \right)$$

which can be rearranged to give

$$\operatorname{Ln}\left(\frac{\operatorname{Io}}{\operatorname{AT}^{2}}\right) = \operatorname{Ln} \, \mathbf{A} * \left[ -\left(\frac{\operatorname{q}\Phi_{B}}{\operatorname{kT}}\right) \right] \tag{1.9}$$

From this, a plot of  $\ln(I_s/A_eT^2)$  versus 1/kT referred to as a Richardson plot, can be done and the slope gives  $-q\Phi_B$  from which the barrier height  $\Phi_B$  can be determined. The y-intercept gives the  $\ln(A^*)$  from which the Richardson's constant,  $A^*$ , can be determined. In another version, a plot of  $\ln(I_o/AT^2)$  versus 1/nkT, called the modified Richardson plot, can be performed to give values that are independent of the ideality factor.

#### 1.2.4 The Capacitance-Voltage Characterization

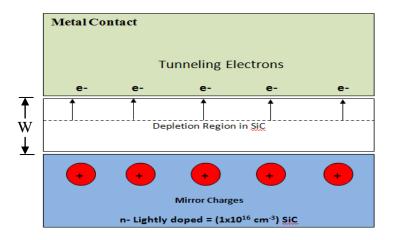

The depletion region created when the semiconductor is sandwiched between the ohmic and Schottky contacts is analogous to a parallel plate capacitor. The electrons in the n-type material tunnels into the metal and have a mirrored electric positive charge in the semiconductor which is shown in Fig. 5 [16].

Fig. 4. Schottky contact depletion Region

The capacitance of the Schottky diode is given by Eq. 1.10,

$$C(V) = \frac{\varepsilon A}{W(V)} = A\sqrt{\frac{\varepsilon N_D}{2(V_{bi} - V_a)}}$$

(1.10)

where W is the width of the depletion region,  $V_{bi}$  is the built-in potential, and A is the area of the diode. Both the built-in voltage  $(V_{bi})$  and doping density  $(N_D)$  can be found from  $1/C^2$  versus V plot [15].

The C-V measurement is performed by gluing the sample on a copper plate with the Schottky contact facing up. The copper plate, electrically connected to the ohmic contact is wired to the low bias side, while the Schottky contact is connected through a pin-shaped probe to the high bias side of the capacitance meter used. In this work, we used the Agilent Precision LCR meter. C-V values were obtained by superimposing a small alternative voltage of 10 mV at 1 MHz on the reverse dc bias and the resulting data was analyzed using the relation

$$\left(\frac{A}{C}\right)^{2} = \frac{2\left[V_{bi} - \frac{kT}{q}\right]}{qk_{s}\varepsilon_{0}N_{D}} + \frac{2V}{qk_{s}\varepsilon_{0}N_{D}}$$

(1.11)

where A= Area of the Schottky contact,  $V_{bi}=$  built-in potential,  $k_s=$  semiconductor dielectric constant,  $N_D=$  doping concentration of the semiconductor, k= Boltzmann constant, T= temperature in Kelvin and  $\epsilon_0=$  permittivity of free space.

By plotting  $(A/C)^2$  versus the reverse bias voltage V, a straight line is obtained whose slope is  $2/q\epsilon_0N_D$ . From the value of the slope, the semiconductor doping concentration  $N_D$ , can be computed. The intercept on the V-axis is numerically equal to  $V_i = -V_{bi} + kT/q$ , and from this value, the built-in potential  $V_{bi}$  is obtained. Then the Schottky barrier height is computed using the relation

$$\Phi_{\rm B} = {\rm Vi} + \left(\frac{kT}{\rm q}\right) \left[1 + \ln\left(\frac{N_o}{N_D}\right)\right] \tag{1.12}$$

where the value  $N_o = 1.69 \times 10^{19}$  cm<sup>-3</sup> was used for the effective density of state for 4H-SiC [7].

#### **CHAPTER TWO**

#### SCHOTTKY DIODE FABRICATION

#### 2.1 Preparing SiC Substrate and Ohmic Contacts

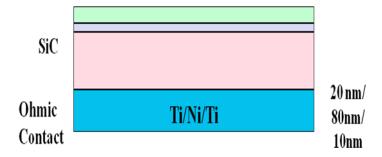

A Schottky diode consists of both ohmic and Schottky contacts. An ohmic contact was deposited on the heavily doped backside of the n-type 4H-SiC substrate and a Schottky contact was deposited on the lightly doped n-type 4H-SiC epilayer on the front side. The n-type 4H- SiC used consisted of a 400-um thick substrate with a resistivity of  $0.019 \Omega$ -cm which contained two n-type epilayers grown  $8^{\circ}$  off the basal (0001) plane. The first epilayer was 0.5  $\mu$ m thick with N<sub>D</sub> ~ 1 ×10<sup>18</sup> cm<sup>-3</sup> and the second epilayer was 4.6  $\mu m$  thick with  $N_D \sim 1 \times 10^{16}$  cm<sup>-3</sup>. The SiC wafer was diced into  $5 \times 5$  mm<sup>2</sup>. A sacrificial layer of SiO<sub>2</sub> of 30 nm thickness was grown at 1150 °C on the SiC surface to help improve the surface morphology. These were cleaned using the standard RCA (Radio Corporation of America) cleaning process, which was boiling in acetone (3 min), boiling in isopropyl alcohol (3 min), and rinsing with de-ionized water. The samples were then kept in diluted hydrofluoric acid (1HF: 10H<sub>2</sub>O) for three minutes to strip the sacrificial layer, rinsed with de-ionized water and dried. The samples were mounted in the vacuum chamber with the thickness monitor attached. The samples were placed 10 cm away from the sputter target. The vacuum chamber was pumped down to a base pressure of 8.4×10<sup>-7</sup> Torr. After reaching this pressure, argon gas was allowed in the chamber with its flow controlled by a mass flow controller. The Ar gas flow rate was maintained at 15 SCCM (standard cubic centimeters per minute) and the pressure of the

chamber during deposition was held at 2 mTorr. Metals used for the ohmic contact were Titanium (Ti) and Nickel Gallide (Ni<sub>0.9</sub>Ga<sub>0.1</sub>), that is reported to form low resistance ohmic contact on n-type 4H-SiC [18]. The ohmic contact was deposited on the heavily doped substrate (backside). The heavy doping decreases the junction barrier height and makes the thickness of the depletion width extremely narrow, and promotes the probability of electron tunneling from the semiconductor to the metal. The titanium was sputtered at a current of 0.1 A to a thickness of 20 nm, followed by nickel gallide sputtered at a current of 0.05 A to a thickness of 80 nm thickness, and finally, another titanium layer sputtered to a thickness of 10 nm. Thickness of the ohmic contact metals was monitored by the thickness monitor, which was calibrated for each metal. One minute of pre sputtering time was allowed before depositing each metal to clean the surface oxides from the target. Fig. 6 shows the SiC with an ohmic contact on the backside.

Fig. 5. Silicon carbide with an ohmic contact on the back side

After depositing the ohmic contact the samples were taken out of the vacuum chamber and cleaned in boiled acetone, alcohol, and rinsed with de-ionized water. The

samples were annealed using rapid thermal processor (RTP) in pure nitrogen ( $N_2$ ) at 950  $^{\circ}$ C for 2 min. Pure  $N_2$  limits oxidation of the contact during annealing. By annealing, the metal will interact with the semiconductor and form a contact with very low electric resistance.

#### 2.2 The Schottky Contacts

Schottky contacts are formed when the metal work function is greater than the n-type semiconductor work function. If the metal work function is greater than the n-type semiconductor work function, then a potential barrier will be established between the metal and the semiconductor. This potential barrier makes the electrons flow from the semiconductor to the metal and blocks the electrons that flow from the metal to the semiconductor. Breakdown voltage occurs when electrons flow from the metal to the semiconductor. Schottky contacts are always deposited on the lightly doped side of the n-type 4H-SiC.

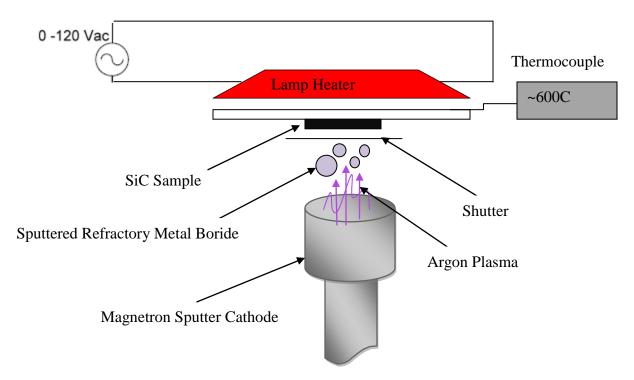

The samples were cleaned again in boiled acetone and alcohol, rinsed with deionized water and dried. The samples were attached to a heater (two 500-W halogen lamps) and a thermo couple used for monitoring the temperature of the sample. The heating temperature was controlled by an external voltage controller. The vacuum chamber was then pumped down to a base pressure of  $8.8 \times 10^{-7}$  Torr and the refractory metal borides used as Schottky contact were deposited. The samples were preheated at 600 °C for about an hour enable thermal desorption that helps make the surface of the sample cleaner through evaporating away unwanted contaminants such as water vapor or dust on the sample surface. The Schottky contacts were deposited at a base pressure of 2 mTorr by allowing argon gas to flow at a rate of 15 SCCM. The metal borides which

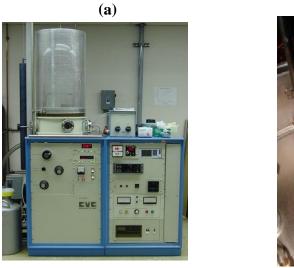

were deposited were W<sub>2</sub>B<sub>5</sub>, W<sub>2</sub>B, WB, TiB<sub>2</sub>, HfB<sub>2</sub>, and CrB<sub>2</sub>. All these metals were sputtered at room and high temperature (600 °C) on different samples for an hour with a current of 0.05 A. The choice of these deposition temperatures is explained in Chapter 3 section 1. The temperature was increased slowly with a power stat and monitored with the thermo couple. After reaching the desired temperature (600 °C), metal was pre sputtered for two minutes and sputtered for an hour to make the Schottky contact. Note that the Schottky contact metals are deposited on the whole sample (called blanket deposition). Fig. 7 and Fig. 8 show the high vacuum chamber, the sputter targets, and the plasma sputter deposition process.

Fig. 6. (a) Plasma sputter deposition chamber and (b) the sputter targets

#### 2.3 Patterning the Schottky Contact

To make individual Schottky diodes, the blanket deposited Schottky contact metal requires patterning where unwanted metal is removed in appropriate acidic etchants. To accomplish this, the samples were cleaned again in boiled acetone and alcohol, rinsed with de-ionized water and dried. A photolithographic process was carried by uniformly

spreading a positive photoresist (AZ5214) using a spin coater on the sample surface. The spin coater was operated at 5000 rpm for 30 sec to spread the photo resist uniformly into a thin layer on the sample surface. The samples were then placed on a hot plate at 110 °C for one minute to bake the photoresist and evaporate the resist solvent. The samples were exposed to UV light through photo mask for 3 minutes in the mask liner. The photo mask image transferred to the samples after being exposed to UV light.

Fig. 7. Plasma deposition process

These samples were developed using the AZ 400K developer for 45 sec and quickly rinsed in water for 40 sec. The developer which used was diluted with water, that is, 1 part AZ400K to 4 parts H<sub>2</sub>O. In the positive photolithography process exposure to UV light breaks the chemical bonds in the material so that the exposed region dissolves in the developer and the unexposed region remains. The pattern on the sample is the same as the pattern on the mask. Fig. 9 shows the UV mask liner and the spin coater.

Fig. 8. (a) UV mask liner and (b) spin coater

After completing the positive photolithography the samples were baked at 120 °C on a hot plate for 2 minutes to harden the photo resist, a critical step needed when acid etching is to be performed. The ohmic contact was protected by mounting the backside of the sample to a Si wafer before dipping the samples in the acid. The acidic solution used to etch most of the refractory metal borides was three parts hydrochloric acid to one part nitric acid (1HCl: 3HNO<sub>3</sub>). The samples were placed in the acid solution for 1 minute, dipped in water, and observed under the microscope and this was repeated to ensure that all the unwanted metal was removed. If left too long in the acid solution, it was found that all the Schottky contact got etched away. The contacts deposited at room temperature required about 5 min dip in the acid solution while the boride Schottky contacts deposited at 600 °C required about 3 min acid dipping. The chemical for etching HfB<sub>2</sub> was one part

hydrofluoric acid to one part nitric acid (HF:  $HNO_3$ ), which was different from the ones used for the other refractory metal borides. All the samples needed to be rinsed thoroughly in water after being removed from the acid. In chemical etching, the metal covered by the photo resist is protected and metal not covered by the photo resist is etched away. Finally, photo resist was removed by soaking the sample in acetone for 10 minutes, rinsing in alcohol and water and dried. After the lift-off process, the samples were left with many Schottky diodes that had an ohmic contact on the backside and a Schottky contact on the front side. The defined circular Schottky contact had diameters of approximately 150  $\mu$ m, 170  $\mu$ m, 180  $\mu$ m, 190  $\mu$ m, and 200  $\mu$ m. The final structure and top view of the diode is shown in Fig. 10.

Fig. 9. (a) Final Schottky diode structure and (b) Top view showing the Schottky contact

### **CHAPTER THREE**

# EFFECT OF DEPOSITION TEMPERATURE USING I-V MEASUREMENTS

# 3.1 Previous Work with ZrB<sub>2</sub>

The refractory metal boride Schottky contacts used in this work were deposited at two different temperatures: 20 °C (room temperature) and 600 °C (high temperature). The choice of the 600 °C used was based on previous results performed on ZrB<sub>2</sub> contact and reported by Oder et al. [19]. ZrB<sub>2</sub> was deposited as a Schottky contact on n-type 4H-SiC at different temperatures of 20 °C, 200 °C, 400 °C, 600 °C and 800 °C and the resulting Schottky barrier diodes were characterized.

Fig. 10. Results from Schottky diodes made with  $ZrB_2$  contacts deposited at different temperatures showing variation of (a) the barrier height, (b) the ideality factor and (c) the series resistance.

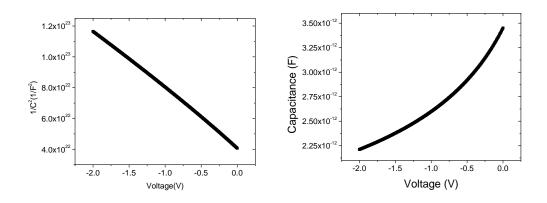

Fig. 11 (a) shows a plot of the Schottky barrier height (SBH) versus the deposition temperature of the ZrB<sub>2</sub>/SiC Schottky contacts. As can be seen from this figure, there is a remarkable increase of the SBH from 0.87 eV for deposition temperature of 20 °C to 1.07 eV for a deposition temperature of 600 °C from the I-V measurements ( $\Delta\Phi_B=0.20$  eV). The C-V measurements revealed a similar trend with slightly higher values for the SBH of 1.05 eV for contacts deposited at 200 °C to 1.17 eV for contacts deposited at 600 °C. Fig. 11 (b) shows the variation of the ideality factor (n) with the deposition temperature. It is seen here that the ideality factor decreases from 2.91 for contacts deposited at 20 °C to 1.06 for contacts deposited at 600 °C, indicating improvement of the interface homogeneity.

A no ideal Schottky diode with ideality factor greater than one suggests the presence of other carrier transport mechanisms in addition to thermoinic emission. For such a diode, the flat band Schottky barrier height, independent of the current conduction mechanism, provides a more representative value. Thus for the results of our I-V measurements shown in Fig. 11 (a) and (b), the larger ideality factors at lower deposition temperatures result in underestimated barrier heights that can reduce the trend of SBH increase with increasing deposition temperature. However, theoretical and experimental studies have shown that SBH determined by C-V method essentially match the flat band SBH [20, 21]. The values of the SBH we determined by C-V measurements shown in Fig. 11 (a) confirm the trend of increasing SBH with the deposition temperature. Note that the trend is less for the C-V measurements than for the I-V measurements. An estimate of the series resistance (R<sub>S</sub>) of the as-deposited Schottky contacts was made using the procedure outlined in chapter 2. Fig 11 (c) shows the variation of the average

values of  $R_S$  with the deposition temperature. As can be seen here, there is a decrease in the value of  $R_S$  from about 502  $\Omega$  to 76  $\Omega$  as the deposition temperature was varied from 200 °C to 600 °C, and slightly rising to about 94  $\Omega$  for contacts deposited at 800 °C.

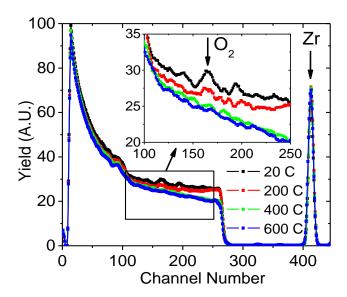

To study the physical properties of the boride/SiC films with the alteration of the substrate temperature during deposition, several unpatterned SiC samples were prepared.  $ZrB_2$  films were deposited on each sample at different temperatures of 20 °C, 200 °C, 400 °C and 600 °C. The samples were then analyzed using Rutherford backscattering spectroscopy (RBS), and the resulting spectra from these films are shown in Fig. 12. The inset is an expanded view of the spectra showing the decrease in the oxygen peak with the deposition temperature. From the simulation of these spectra, the Zr:B:O ratios at these deposition temperatures are 1:2:1 at 20 °C; 1:2:0.4 at 200 °C; and 1:2:0 at 400 °C and 600 °C.

Fig. 11. Rutherford backscattering spectra of  $ZrB_2$  films deposited on SiC at different temperatures. The inset shows an expanded view of the spectra showing the decrease of the  $O_2$  peak with deposition temperature.

This implies that deposition of the borides on SiC held at or above  $400\,^{\circ}\text{C}$  results in little or no  $O_2$  in the boride/SiC contacts. The escape of  $O_2$  in the form of volatile  $B_2O_3$  has been reported in investigations of  $CrB_2$  and  $TiB_2$  films [22, 23]. It is therefore plausible to expect that in the boride contacts here studied,  $O_2$  would similarly escape by way of oxides such as  $B_2O_3$  or  $H_3BO_3$  known to be volatile at  $300\,^{\circ}\text{C}$ , when these borides are deposited on SiC substrates held at  $400\,^{\circ}\text{C}$  and above [24, 25]. Since the presence of impurities such as  $O_2$  at the interface is known to contribute to undesirable electrical characteristics, the improvement of the barrier properties of the boride/SiC contacts is possibly due to the escape of  $O_2$  from the metal/SiC interface. For this reason, the temperature of  $600\,^{\circ}\text{C}$  was selected as the one at which all the boride contacts in this study would have their optimum electrical properties, when compared to boride contacts deposited on unheated SiC samples.

#### 3.2 I-V Characterization

The current-voltage (I-V) measurements were taken on at least five different Schottky diodes separately for those with the Schottky contacts deposited at room and those with the contacts deposited at 600 °C. The samples were glued to a copper plate using conductive silver paste with the backside ohmic contact attached to the copper plate which was connected by a wire to the negative terminal of the Keithley Sourcemeter (model 2400). The Schottky contact on the top side of the sample was connected to the positive terminal through a small probe. A Labview software program written for the I-V measurements was used to collect the data, where the current was measured as the voltage was varied from 0 to 3 volts for the forward bias measurements. In this range,

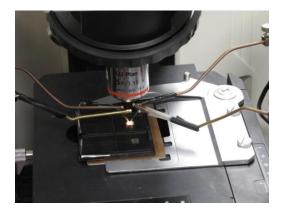

300 data points were collected. For reverse bias measurements, the voltage was varied from -20 V to 0 volts. Figure 13 (a) shows the Keithley Source meter used for this characterization and Fig. 13 (b) shows three samples glued to the copper plate used in the measurements.

Fig. 12. (a) Keithley source meter (b) samples on a copper plate

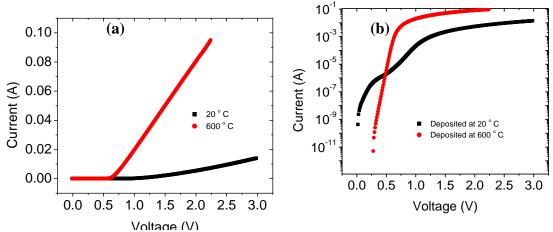

To test for thermal stability of the diodes, the samples were then removed from the copper plate, thoroughly cleaned with acetone to remove residual silver paste and placed in the rapid thermal processor for annealing. The annealing was performed in a pure nitrogen environment to eliminate oxidation of the samples when raised to a high temperature. Each sample was annealed at 600 °C for 20 minutes. Following the annealing, the samples were again glued to the copper plate and the I-V measurements repeated. Where possible, the I-V measurements were performed on the same diodes for accurate comparison of the results obtained before and after annealing. The results from these measurements were analyzed using the Schottky-Mott theory where thermionic emission is assumed as the dominant charge transport mechanism. Fig. 14 shows the plot

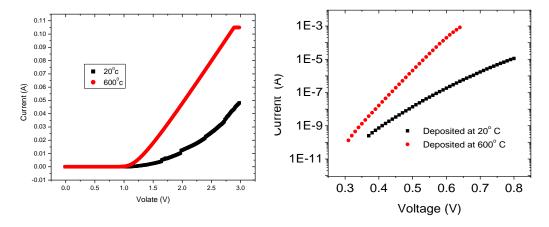

Fig. 13. Current- voltage data for the borides deposited at 20 °C and 600 °C. (a) shows the plot with both I and V on linear scales and (b) shows the plot with I on a log scale while V is on a linear scale.

of the data on a linear scale and on a semi log scale. The linear portion of the semi log plot (under low voltage, prior to roll-over, Fig. 14 (b)) is extracted and analyzed. Its slope is used to compute the ideality factor and its intercept is used to compute the Schottky barrier height. Since the slope = q/nkT, it implies that the steeper linear portion will yield a smaller value of the ideality factor.

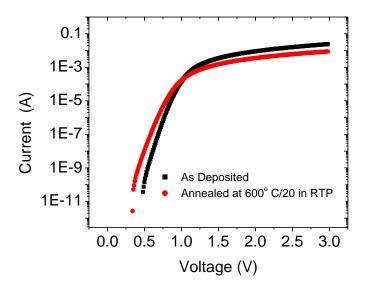

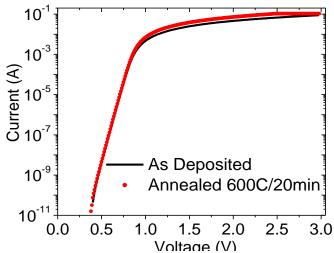

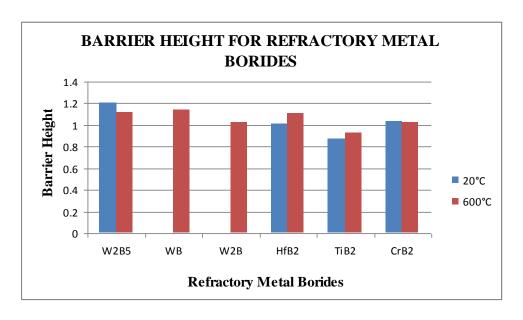

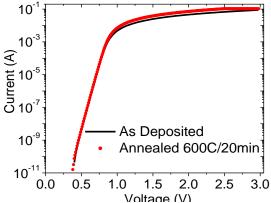

Fig. 15 shows a semi log I-V plot from diodes made with WB Schottky contacts and deposited at 20 °C. I-V measurements were done on as-deposited Schottky contacts and then after the diodes were annealed at 600 °C for 20 min. As can be seen, the low-voltage linear portion of this plot is not very straight, indicating a poor quality diode. By contrast, similar plots for diodes with WB contacts deposited at 600 °C (Fig. 16) shows a more linear semi log plot which remains unchanged even after the annealing at 600 °C for 20 min in N<sub>2</sub>. The calculations and analyses of these measurements were conducted with the help of equations explained in Chapter 2 and the results are shown in Fig. 17 and Fig. 18.

Fig. 14. Semi log I-V plot from diodes made with WB Schottky contacts deposited at 20  $^{\circ}$ C before annealing and after annealing at 600  $^{\circ}$ C/20 min in N<sub>2</sub>.

Fig. 15. Current-Voltage plot of diodes with the WB deposited at 600  $^{\circ}$ C before (as-deposited) and after annealing at 600  $^{\circ}$ C for 20 min in  $N_2$ .

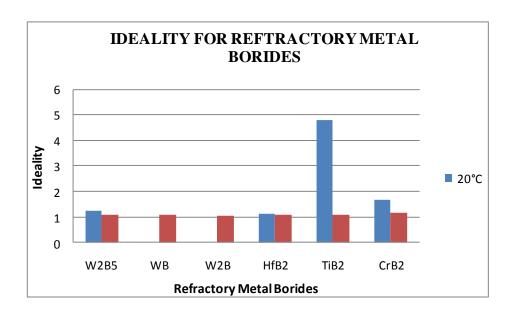

A contrast can be seen in diodes with the Schottky contacts deposited at room temperature compared to the Schottky contacts deposited at high temperature (600  $^{\circ}$ C). For WB and W<sub>2</sub>B metals, room temperature deposition didn't yield good ideality values

because the data was not good enough to extract these values. When ideality value was close to one, the value of the barrier height could be trusted. The Schottky contacts which were deposited at  $600\,^{\circ}$ C have ideality values approximately equals to one when compared to those deposited at  $20\,^{\circ}$ C.

Fig. 16. Values of the ideality factor for the refractory metal borides

Fig. 17. Values of the Schottky barrier heights for the refractory metal borides

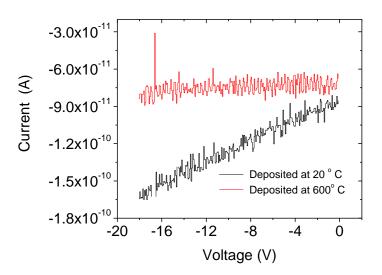

# 3.3 Measurement and Analysis of the Contacts in Reverse Bias

Reverse bias I-V characteristics were performed to find the leakage current density and breakdown voltage of the Schottky diodes. The Keithley source meter available in our laboratory for this investigation has a voltage range of 5  $\mu$ V to 20 V. This range is not sufficient to measure the breakdown voltage of the Schottky diode. However, leakage current densities at -15 V were measured for the Schottky diodes which were deposited at room and high temperature (600 °C). Fig. 19 shows the leakage current densities at room and high temperature. From the appendix 5 and 6 and from Fig. 19, a contrast can be seen in the Schottky contacts deposited at high temperature compared to the Schottky contacts deposited at room temperature.

Fig. 18. I-V plots of  $W_2B$  contact diodes deposited at 20 °C and 600 °C

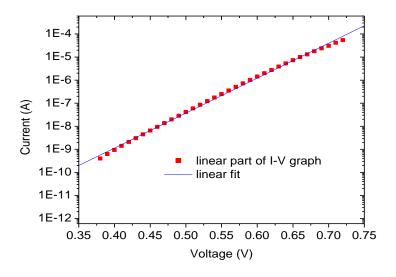

# 3.4 Determination of the Specific on-Resistance

The specific on-resistance ( $R_{on}$ ) of the diode is an important parameter for high efficiency power devices. In this study, on-resistance was obtained by first determining the series resistance  $R_s$  of the diode for the non-linear region of the ln(I) versus V plot. As explained in Chapter 2, if V >> 3kT/q, we can use the equation

$$I = AA^*T^2 \exp\left(\frac{-q\Phi_B}{kT}\right) \exp\left[\frac{q(V - IR_S)}{nkT}\right]$$

(3.1)

which can be rearranged to give,

$$I = \frac{1}{R_s} \left( \frac{dV}{d[\ln(I)]} \right) - \left( \frac{kT}{q} \right) \left( \frac{n}{R_s} \right)$$

(3.2)

A graph of I versus dV/d[ln(I)] was plotted and the series resistance was then obtained from the reciprocal of the slope of the linear section of graph. The specific onresistance was determined by multiplying series resistance ( $R_S$ ) by the area (A) of the diode.

Fig. 19 A plot of current I versus dV/d[ln(I)] of a W<sub>2</sub>B contact deposited at 600 °C

Fig. 20 shows a plot of I versus dV/d[ln(I)] with non-annealed  $W_2B$  deposited on silicon carbide at 600 °C, yielding a typical resistance of 13 $\Omega$  with the diode contact area  $2.83\times10^{-4}~cm^2$ ; the calculated specific resistance was  $3.72m~\Omega$ -cm [7]. The series resistances of all the Schottky diodes were obtained. Different Schottky diodes have different series resistance. Appendices 7 and 8 show the steps for the calculation of series resistance.

# 3.5 Results from I-V-T Measurements

In this research, current-voltage-temperature (I-V-T) measurements were performed only on CrB<sub>2</sub>/SiC samples. The I-V-T measurements were performed to find out the Richardson constant, and barrier height of the diodes. The characteristic energy values, from which the current-conduction mechanism can be deduced, were not determined in this work. The I-V-T measurements were performed when the samples were glued using silver paste to a plate underneath which was a ceramic heater. The temperature of the sample was monitored using a thermocouple and the I-V measurements were performed for each set temperature ranging from 25 °C to 250 °C in steps of 25 °C. I-V characteristics were obtained with Keithley source meter after the temperature stabilized in increments of 25 °C. The ideality factor and the saturation current parameters were extracted from the linear region of the forward bias I-V characteristics. The standard diode equation Eq. 3.1 was used to extract the ideality factor (n) and saturation current (I<sub>s</sub>), which is expressed as

$$I_o = AA^*T^2 \exp\left(-\frac{q\Phi_B}{kT}\right)$$

(3.3)

After rearranging the Richardson constant  $A^*$ , zero-bias barrier height  $\Phi_{bo}$  can be obtained from

$$\ln\left(\frac{\text{Io}}{\text{AT}^2}\right) = \ln(\text{A}^*) - \left(\frac{q\Phi_{\text{B}}}{\text{kT}}\right)$$

(3.4)

Plot of 1/kT versus  $ln(I_s/A_eT^2)$  is referred to as a Richardson plot where the slope gives the barrier height and the y-intercept is  $ln(A^*)$ . From the y-intercept a Richardson constant was obtained.

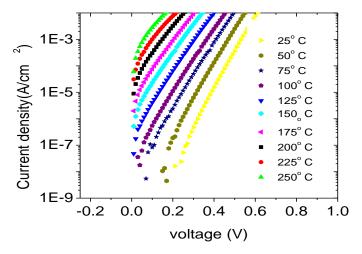

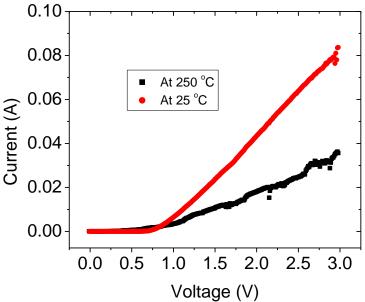

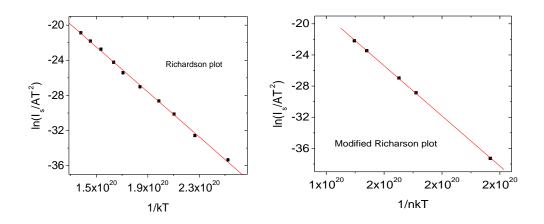

Current density-voltage data at selected temperatures of CrB<sub>2</sub>/SiC Schottky diodes are shown in Fig. 21 (log plot). Linear plot of the CrB2/SiC at 25 °C and 250 °C is shown in Fig. 22. From the log plot, intercept and slope were obtained, and from those values ideality factor and barrier height values were obtained. After finding I<sub>s</sub> from the standard diode equation, plotted 1/kT versus ln(I<sub>s</sub>/A<sub>e</sub>T<sup>2</sup>) and the Richardson constant were obtained. The value obtained did not match the theoretical Richardson constant for n-type SiC which is 146 AK<sup>-2</sup>cm<sup>-2</sup>. In the investigation of the effect of threading dislocation on n-type GaN Schottky diode, A.R Arehart et al. reported a modified

Fig. 20. Current density versus voltage plots in 25 °C increments

Richardson plot [26]. The plot between  $ln(I_s/A_eT^2)$  versus 1/nkT is called the modified Richardson plot. Fig. 23 shows the Richardson and modified Richardson plots for the  $CrB_2/SiC$  Schottky diode. Also, the Richardson constant value obtained from the modified Richardson plot did not match the theoretical Richardson constant.

Fig. 21. I-V at measuring temperatures 25 °C and 250 °C

Table 3 shows the values of the Richardson constant and modified Richardson constant values obtained for the CrB<sub>2</sub>/SiC Schottky contact.

Table 3. Richardson Constants obtained for CrB<sub>2</sub>/SiC contacts

|                  | Deposition  | Measurement | Richardson constant | (AK <sup>-2</sup> cm <sup>-2</sup> ) |  |

|------------------|-------------|-------------|---------------------|--------------------------------------|--|

| Metal            | Temperature | temperature | from Richardson     | from Modified                        |  |

|                  |             |             | Plot                | Richardson plot                      |  |

| CrB <sub>2</sub> | 600 °C      | 25-250 °C   | 0.14                | 4925814                              |  |

| CrB <sub>2</sub> | 600 °C      | 250-25 °C   | 0.30                | 741181                               |  |

| CrB <sub>2</sub> | 600 °C      | 25-250 °C   | 33.78               | 591253                               |  |

Fig. 22. (a) Richardson and (b) modified Richardson plot

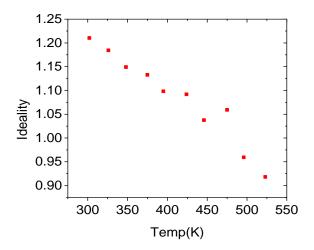

The effect of ideality factor and barrier height with the temperature measurement was also studied. The plots of ideality versus temperature and barrier height versus temperature are shown in Fig. 24 and Fig. 25. From the ideality and temperature plot, it seems that the ideality is inversely proportional to the measuring temperature until 250 °C. As the temperature increased the ideality approached to unity.

Fig. 23. Temperature versus ideality plot using IVT measurements

Based on the barrier height versus temperature plot, it seems that the barrier height is directly proportional to the measuring temperature. Along with the increase in temperature, barrier height also increased.

Fig. 24. Temperature versus barrier height plot using IVT measurements

Table 4. Schottky contacts deposited at 20  $^{\rm o}C$  (a) measured from 25  $^{\rm o}C$  to 250  $^{\rm o}C$  and (b) measured back from 250  $^{\rm o}C$  to 25  $^{\rm o}C$

|         | Ideality | Barrier     |

|---------|----------|-------------|

| Temp(K) | factor   | Height( eV) |

| 295     | 1.24     | 1.02        |

| 327     | 1.19     | 1.05        |

| 351     | 1.18     | 1.06        |

| 371     | 1.17     | 1.07        |

| 399     | 1.1      | 1.10        |

| 428     | 1.05     | 1.12        |

| 446     | 1.04     | 1.12        |

| 473     | 1.07     | 1.12        |

| 498     | 0.98     | 1.14        |

| 523     | 0.91     | 1.16        |

|         | Ideality | Barrier     |  |

|---------|----------|-------------|--|

| Temp(K) | factor   | Height( eV) |  |

| 523     | 0.91     | 1.16        |  |

| 496     | 0.95     | 1.15        |  |

| 475     | 1.05     | 1.12        |  |

| 446     | 1.03     | 1.12        |  |

| 424     | 1.09     | 1.10        |  |

| 395     | 1.09     | 1.09        |  |

| 375     | 1.13     | 1.08        |  |

| 348     | 1.14     | 1.07        |  |

| 326     | 1.18     | 1.06        |  |

| 302     | 1.21     | 1.04        |  |

|         |          |             |  |

(a) (b)

Table 4 and 5 shows the vales of the ideality factors and the barrier height values for the samples deposited at 20 °C and 600 °C with the measuring temperature. The temperature measurement was from 25 °C to 250 °C and back to 25 °C. In Table 4 and 5, temperature is expressed in Kelvin.

Table 5. Schottky contacts deposited at 600  $^{\rm o}C$  (a) measured from 25  $^{\rm o}C$  to 250  $^{\rm o}C$  (b) measured back from 250  $^{\rm o}C$  to 25  $^{\rm o}C$

|         | Ideality | Barrier     |

|---------|----------|-------------|

| Temp(K) | Factor   | Height (eV) |

| 294     | 1.25     | 1.07        |

| 323     | 1.19     | 1.09        |

| 348     | 1.23     | 1.08        |

| 376     | 1.17     | 1.09        |

| 397     | 1.16     | 1.09        |

| 426     | 1.17     | 1.09        |

| 447     | 1.13     | 1.09        |

| 472     | 1.12     | 1.1         |

| 501     | 1.15     | 1.1         |

| Temp(K) | Ideality<br>factor | Barrier<br>Height (eV) |  |

|---------|--------------------|------------------------|--|

| 473     | 1.75               | 1.52                   |  |

| 452     | 1.22               | 1.13                   |  |

| 427     | 1.21               | 1.13                   |  |

| 398     | 1.24               | 1.13                   |  |

| 376     | 1.27               | 1.11                   |  |

| 347     | 1.28               | 1.11                   |  |

| 328     | 1.3                | 1.1                    |  |

| 299     | 1.31               | 1.11                   |  |

(a) (b)

# **CHAPTER FOUR**

# EFFECT OF DEPOSITION TEMPERATURE USING C-V CHARACTERIZATION

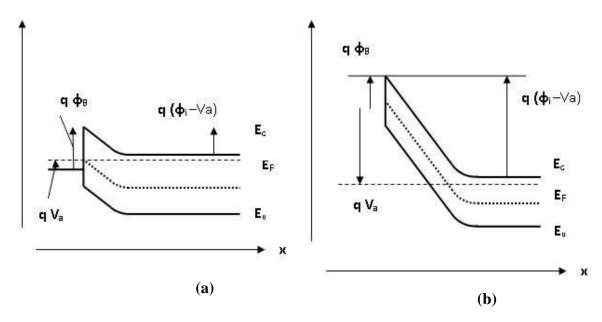

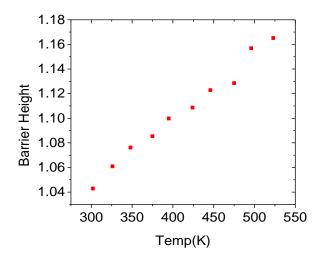

The electric field and potential distribution in the depletion region of the Schottky barrier junction depends on the barrier height, the applied voltage, and the impurity concentration. The barrier height and the doping concentration can also be determined by capacitance-voltage measurement. The capacitance-voltage technique relies on the fact that the width of a reverse-bias space charge region of a semiconductor junction device depends on applied voltage. Considering the Schottky barrier diode in Fig. 26, the semiconductor is n-type 4H-SiC with doping density N<sub>D</sub>. A dc bias voltage is applied to the metal contact and the reverse bias produces a space charge region (scr) of width W. In Fig.26 dW is the slight increase in the scr after dc and ac biasing of the diode.

Fig. 25. Schottky diode with bias

The differential or small signal capacitance is defined by,

$$C = -\frac{dQ_s}{dV} \tag{4.1}$$

where  $Q_s$  is the semiconductor charge. The negative sign accounts for more negative charge in the semiconductor space charge region for higher positive voltage on the metal. The capacitance was determined when a small ac voltage was superimposed on a dc bias. Charges of one sign are induced on the metal surface and charges of the opposite sign on the semiconductor [27]. The voltage change affects the depletion width which is inversely proportional to the capacitance. The C-V curves are also affected by the frequency at which they are being measured. The curve for low and high frequency in the accumulation region is the same but this is not the case in the inversion region. As explained in Chapter 2, the relationship between capacitance (C) and voltage (V) is given by the Eq. 4.1,

$$C = \sqrt{\frac{q\varepsilon_o N_D}{2\left(V_{bi} - V - \frac{kT}{q}\right)}}$$

(4.2)

Eq. 4.1, can be written in the form,

$$\frac{1}{C^2} = \frac{2\left(V_{bi} - V - \frac{kT}{q}\right)}{q\varepsilon_o N_D} \tag{4.3}$$

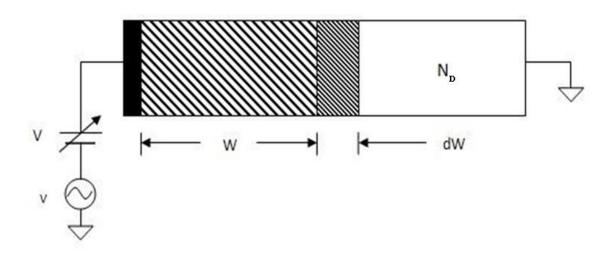

The capacitance-voltage (C-V) measurements were taken on the Schottky diodes before and after the annealing where the Schottky contacts were deposited at room and

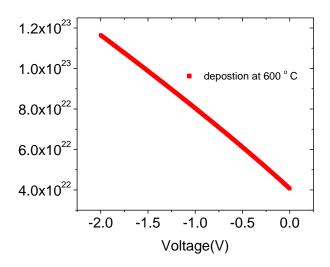

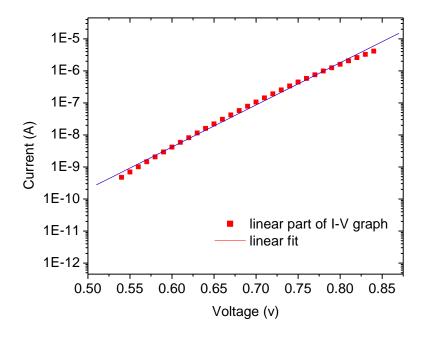

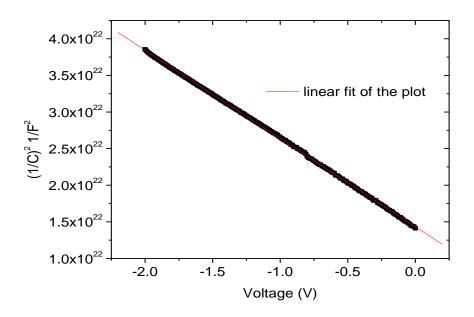

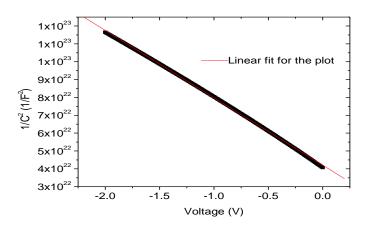

high temperature (600  $^{\circ}$ C). From the Eq. 4.3, the plot of (A/C)  $^{2}$  versus the reverse-bias voltage gives a straight line graph from which the values of doping concentration (N<sub>D</sub>) and barrier height ( $\phi_{B}$ ) can be determined. Fig. 27 shows the plots between C versus V and  $1/C^{2}$  versus V for a Schottky diode made with one of the refractory metal boride as the Schottky contact. For uniformity doped materials,  $1/C^{2}$ -V data was linear whereas C-V data is not as linear as  $1/C^{2}$ -V data.

Fig. 26. (a)  $1/C^2$  versus V and (b) C versus V.

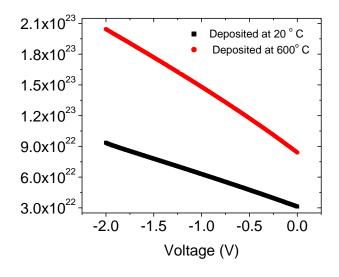

Fig. 27. 1/C<sup>2</sup>-V plots of diodes with W<sub>2</sub>B contact deposited at 20 °C and 600 °C

Fig. 28 shows the 1/C<sup>2</sup>-V graphs for the Schottky diodes which were deposited at room and high temperature. Appendices 3 and 4 show the steps to find the barrier height and doping concentration of the Schottky diodes from the slope and intercept of the plot.

# **4.1 Testing Method for C-V Characterization**

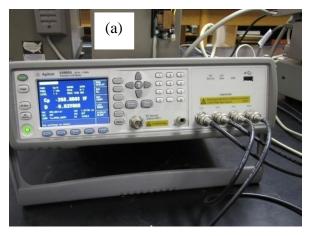

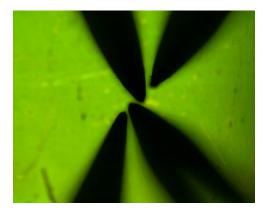

The reverse bias C-V characterization was taken with the help of the Agilent precision LCR meter model E4980A. The Agilent LCR meter was connected to a PC which was running LabView by using a GPIB cable. For each negative voltage applied, a corresponding capacitance measurement through the diode was taken. The LCR meter has four probes. Two of these probes are named as 'high' and connected together. The other two probes are named as 'low' and also connected together. The SiC sample was mounted on the copper plate with silver paste and C-V measurements were taken. All the circular Schottky contacts were tested with a single needle probe attached to the high terminals of the Agilent precision LCR meter with the copper substrate attached to the low terminals. Capacitance-voltage measurements are very sensitive to noise and light means capacitance measurement was not linear if the samples were not measured with in an isolated container. So, all the measurements were done by covering the sample and the single needle probe in an isolated container as shown in Fig. 29. The C-V measurements were performed by superimposing a small alternative voltage of 10 mV at 1 MHz on the reverse dc bias and the capacitance was recorded when the voltage was changed from -5 V to 0 V. Different circular Schottky contacts were selected for each measurement. Five Schottky diodes were characterized for each sample. Fig. 29 shows the setup for the C-V measurements and the samples on the copper plate.

Fig. 28. (a) Agilent precision LCR meter (b) samples on copper substrate (c) samples on isolated container

By plotting (A/C)  $^2$  versus the reverse bias voltage V, a straight line was obtained whose slope is  $2/q\epsilon_0N_D$  and the intercept on the V-axis is  $V_i=-V_{bi}+kT/q$ . From the relation of the Schottky barrier height (SBH) and the built-in potential, we obtain

$$\Phi_{\rm B} = {\rm Vi} + \left(\frac{kT}{\rm q}\right) \left[1 + \ln\left(\frac{No}{N_D}\right)\right] \tag{4.4}$$