# BINARY LOGIC TUTORS FOR TRAINING INDUSTRIAL ELECTRICAL TECHNICIANS

by

Alfred W. Vahey

Submitted in Partial Fulfillment of the Requirements

for the Degree of

Master of Science in Engineering

in the

Electrical Engineering

Program

Skarote 8/10/73 Samue

Adviser

Date

Dean of the Graduate School

Date

YOUNGSTOWN STATE UNIVERSITY

### ABSTRACT

BINARY LOGIC TUTORS FOR TRAINING INDUSTRIAL ELECTRICAL TECHNICIANS

Alfred W. Vahey Master of Science in Engineering Youngstown State University, 1973

This thesis represents the results of obtaining and building tutoral equipment, and developing a series of experiments that can be performed on this equipment to adequately train industrial electrical maintenance technicians in the basics of logic circuitry through a "hands on" approach to understanding.

Although this type of tutoral equipment is becoming more economically available on the market in recent years, there is little available information aimed at practical laboratory reinforcement in this area for industrial electrical technicians.

COUNSSTOWN STATE HNIVEDSIT 277087

#### ACKNOWLEDGEMENTS

My love has deepened for my family as a result of this thesis. The many hours I was removed from them and the house while researching and writing placed an extra burden on them. The completion of this work was possible only through their sacrifice and willingness to do many of the male role chores around the house. I appreciate this sacrifice and will try now to devote the extra hours to my wife, Mary, and my children, Walter, Judee, Andy, Susie, and Stephen.

I express my sincere thanks to Mr. Kramer, Mr. Skarote and Dr. Siman from the Electrical Engineering Department for their guidance and advice in this project, to Barbara Rolla for her typing and special efforts in finalizing this thesis, and to Mr. Joseph Parlink for his photographic contributions.

I am indebted to Mr. Chris Hastings for his help in providing data sheets and DSL materials for experimentation, to Mr. J. Fred Bucy from Texas Instruments, Inc. for providing a number of TTL integrated circuits for experimental use, to Mr. Gary W. Breeding from Monsanto Company for his help in obtaining LED displays, and to the Youngstown Sheet and Tube Company for making available prodac materials.

iii

# TABLE OF CONTENTS

| 4         |                                                   |      |      |     |     |    |   |   |   |   |   | PAGE |

|-----------|---------------------------------------------------|------|------|-----|-----|----|---|---|---|---|---|------|

| ABSTRACT  |                                                   | •••  | •••  | • • | •   | •  | • | • | • | • | • | ii   |

| ACKNOWLE  | DGEMENTS                                          | • •  | ••   | • • | •   | •  | • | • | • | • | • | iii  |

| TABLE OF  | CONTENTS                                          | ••   | •••  | • • | •   | •  | • | • | • | • | • | iv   |

| LIST OF   | SYMBOLS                                           | ••   | •••  | • • | •   | •  | • | • | • | • | • | v    |

| LIST OF 1 | FIGURES                                           | •••  | • •  | • • | •   | •  | • | • | • | • | • | ix   |

| LIST OF   | CABLES                                            | • •  | ••   | • • | •   | •  | • | • | • | • | • | xi   |

| CHAPTER   |                                                   |      |      |     |     |    |   |   |   |   |   |      |

| I.        | INTRODUCTION                                      | • •  | • •. |     | •   | •  | • | • | • | • | • | l    |

| II.       | THEORY AND BASIC BUILDING BLOCK                   | cs.  | • •  | • • |     | •  | • | • | • | • | • | 4    |

| III.      | DSL (CUTLER HAMMER) CONVENTIONA                   | L L  | OGIC | TU: | TOP | ۲. | • | • | • | • | • | 16   |

|           | The Logic Tutor                                   | • •  | •••  | • • | •   | •  | • | • | • | • | • | 16   |

|           | DSL Experiments                                   | • •  | • •  |     |     | •  | • | • | • | • | • | 20   |

| IV.       | ADDITIONAL THEORY                                 | • •  | ••   |     |     | •  |   |   | • |   | • | 47   |

|           | Boolean Algebra                                   | • •  | •••  |     |     | •  | • | • | • | • | • | 47   |

|           | Conversions Between Convention<br>Inverting Logic | onal | and  |     |     |    |   |   |   |   |   | 54   |

| ٧.        | TTL (TEXAS INSTRUMENTS) INVERTI                   | NG   | LOGI | ст  | UTC | DR |   | • |   |   |   | 63   |

|           | The Logic Tutor                                   |      |      |     |     |    | • | • |   |   |   | 63   |

|           | TTL Experiments                                   | •••  |      |     |     | •  | • | • |   |   |   | 68   |

| VI.       | PRODAC (WESTINGHOUSE) NOR LOGIC                   |      |      |     |     | •  | • |   | • |   |   | 86   |

| VII.      | SUMMARY                                           | •    |      |     |     | •  |   | • | • | • |   | 95   |

| APPENDIX  | A. PRODAC Functional Area Cod                     | le.  | • •  |     |     |    | • |   |   | • | • | 97   |

| BIBLIOGRA | PHY                                               |      |      |     |     |    |   |   |   |   |   | 98   |

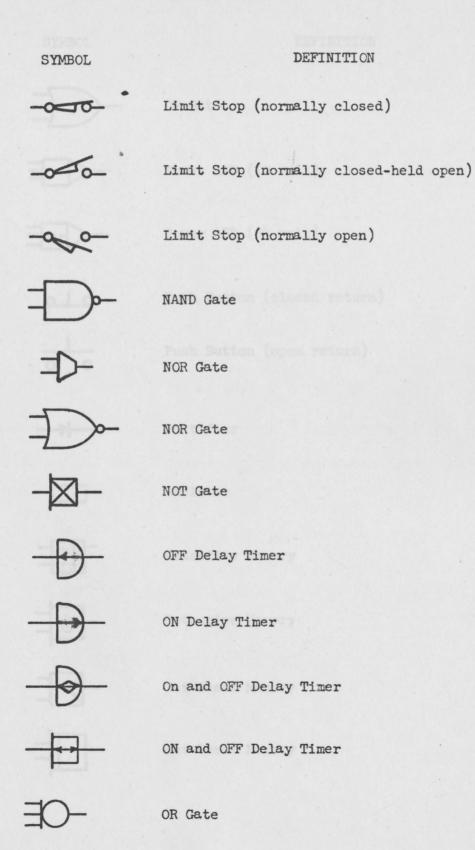

# SYMBOL

### DEFINITIO

DEFINITION

AND Gate

AND Gate

Battery

Capacitor

Contact (normally open)

Contact (normally closed)

D.C. Signal Converter

Exclusive NOR

Exclusive OR

Ground

Indicating Light

Inverter

vi

SYMBOL

DEFINITION

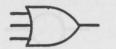

OR Gate

Power AND (10 volt)

-

Power AND (24 volt)

0

Push Button (closed return)

Push Button (open return)

Rectifier

Resistor

Retentive Memory

Retentive Memory

B

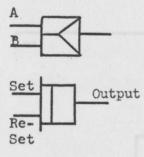

Set-Reset Memory

Set-Reset Memory

SYMBOL

DEFINITION

Solenoid or relay coil

Transistor (NPN)

Transistor (PNP)

Prime operator (negation)

Line over letter or number (negation)

• Dot operator (Series Connection)

+ Plus operator (Parallel Connection)

(+) Exclusive OR operator

# LIST OF FIGURES

| FIGURE |                                             | PAGE |

|--------|---------------------------------------------|------|

| 1.     | Basic Logic System                          | . 4  |

| 2.     | Basic Transistor Switch                     | . 6  |

| 3.     | The "AND" Function                          | • 7  |

| 4.     | The "AND" Circuit                           | . 7  |

| 5.     | The "OR" Function                           | . 8  |

| 6.     | The "OR" Circuit                            | . 8  |

| 7.     | The "NOT" Function                          | • 9  |

| 8.     | The "NOT" Circuit                           | • 9  |

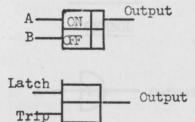

| 9.     | The Off-Return Memory Function              | . 10 |

| 10.    | The Off-Return Memory Circuit               | . 10 |

| 11.    | The Retentive Memory Function               | . 12 |

| 12.    | The Delay Function                          | . 13 |

| 13.    | The "NOR" Function                          | . 14 |

| 14.    | The "NOR" Circuit                           | . 15 |

| 15.    | DSL Logic Tutor                             | . 17 |

| 16.    | DSL Circuit Board and Interconnection Board | . 18 |

| 17.    | DSL Power Supply                            | . 19 |

| 18.    | The DSL AND Board                           | . 21 |

| 19.    | The DSL OR Board                            | . 24 |

| 20.    | The DSL NOT Board                           | . 27 |

| 21.    | The DSL Power AND Board                     | . 30 |

| 22.    | The DSL D.C. Signal Converter               | . 32 |

| 23.    | The Reset Gate                              | • 36 |

| 24.    | The DSL Set-Reset Memory Board              | • 37 |

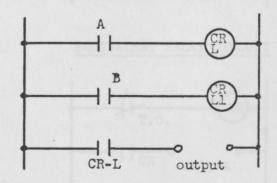

| 25.    | Relay and Static Logic Comparison No. 1     | . 42 |

# LIST OF FIGURES (CONT.)

| FIGURE | E                                        |     |   |     |       |   |   | I | AGE |

|--------|------------------------------------------|-----|---|-----|-------|---|---|---|-----|

| 26.    | Relay and Static Logic Comparison No. 2. |     | • | • • |       |   | • | • | 44  |

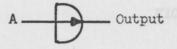

| 27.    | Non-Inverting Logic Circuit              |     | • | • • |       | • | • | • | 54  |

| 28.    | Inverting Type Logic                     | • • | • | • • | <br>• | • | • | • | 55  |

| 29.    | Gate Conversion Method                   |     |   |     |       |   |   |   |     |

| 30.    | TTL Digi-Kit Tutor                       |     |   |     |       |   |   |   |     |

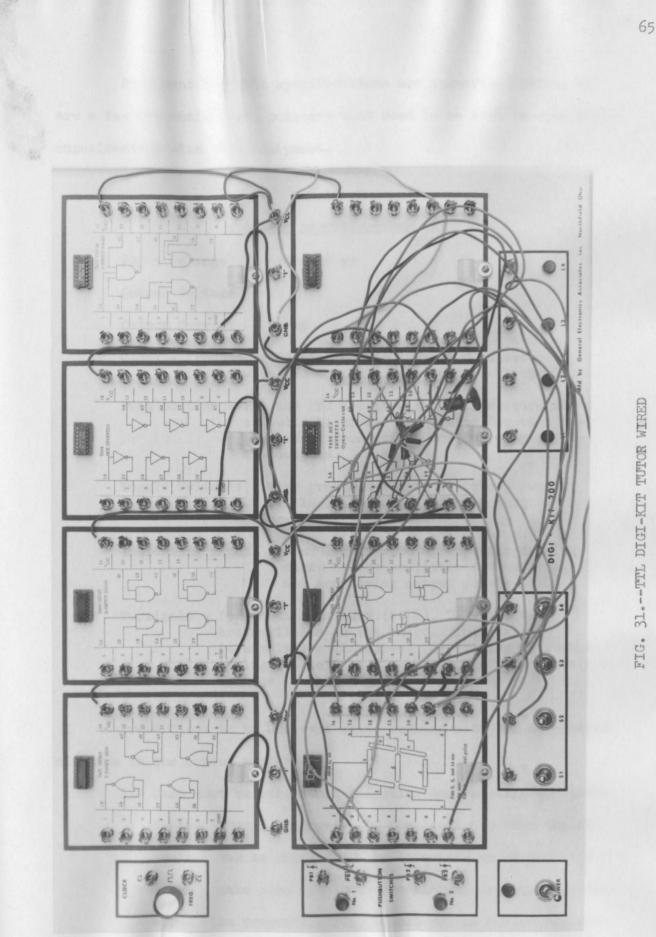

| 31.    | TTL Digi-Kit Wired                       | • • | • | • • |       | • | • | • | 65  |

| 32.    | NOR Elements                             |     | • | • • | <br>• | • | • | • | 89  |

| 33.    | PRODAC Modules and NOR Elements          |     | • | • • | <br>• | • | • | • | 90  |

# LIST OF TABLES

| ABLE |                                    |   |     |      |   |     |   |   |   |   |   | PA  | GE |

|------|------------------------------------|---|-----|------|---|-----|---|---|---|---|---|-----|----|

| 1.   | Relay-Static Logic Comparison      | • | •   | •••  | • | •   | • | • | • | • | • | •   | 4  |

| 2.   | Conventional Logic Symbols         | • | •   | • •  | • | •   | • | • | • | • | • | • 2 | 0  |

| 3.   | The Boolean Structure              | • | •   | • •  | • | •   | • |   | • | • | • | • 4 | 8  |

| 4.   | Boolean Definitions and Postulates | • |     |      | • | •   | • | • | • | • |   | . 4 | 9  |

| 5.   | Boolean Theorems                   |   | •   | • .• |   |     |   | • | • | • |   | • 5 | 1  |

| 6.   | Gate Conversions                   | • | • · | • •  |   | . • | • | • | • | • | • | • 5 | 8  |

| 7.   | Gate Truth Table Summary           | • | •   |      | • | •   | • | • | • | • |   | • 5 | 9  |

| 8.   | Exclusive OR Truth Tables          |   |     |      |   | •   | • | • |   | • | • | . 6 | 0  |

| 9.   | Exclusive OR Diagrams              | • |     |      | • | •   | • | • | • | • | • | . 6 | 1  |

| 10.  | Digi-Kit Specifications            |   |     |      | • |     | • | • | • | • | • | . 6 | 6  |

| 11.  | Basic Gates With TTL               |   |     |      |   |     | • | • | • | • | • | . 6 | 9  |

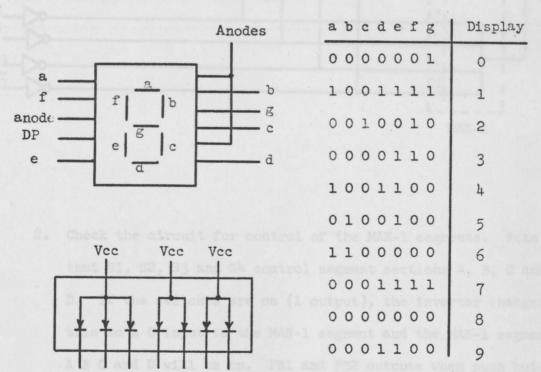

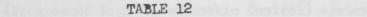

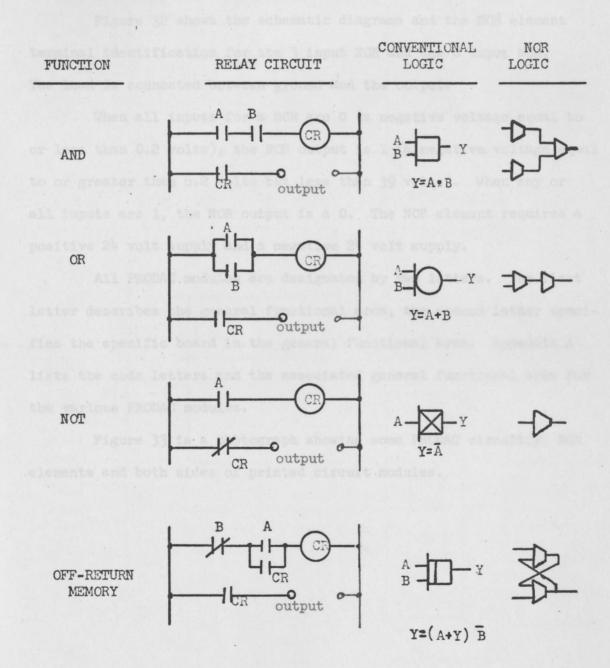

| 12.  | NOR Logic Gates                    |   |     |      |   |     |   |   |   |   | • | . 8 | 7  |

In many industries today the continued education of electrical schuldans in the area of logic circuitry troubleshooting is serious! Aching. I will confine my remarks have to the paris steel industry ith which I do more familiar.

This type of circuitry is becoming much more common in industry today and will be more so in the near future with new equipment installes tions and rewappe on older equipment. This new equipment for a period of time generally requires little maintenance and the manufacturer probably handles problems for the first year. As the equipment ages and the responsibility to maintain it falls on the industrial maintenance people, the training or lack of training impact reveals itself.

# CHAPTER I

1

### INTRODUCTION

The object of this thesis is to develop a practical approach whereby electrical maintenance technicians and apprentices could through a "hands on" approach be able to understand and work with digital circuits and hardware.

The scope will be limited to developing a sufficient number of experiments to enable the electrical technician to adequately understand basic industrial digital circuitry. Three manufacturer's circuitry will be utilized. Cutler Hammer's DSL (Direct Static Logic) which employs conventional logic will be covered, as well as Westinghouse's Prodac and Texas Instruments TTL (Transistor-Transistor Logic) which utilizes inverting logic (NOR circuitry).

In many industries today the continued education of electrical technicians in the area of logic circuitry troubleshooting is seriously lacking. I will confine my remarks here to the basic steel industry with which I am more familiar.

This type of circuitry is becoming much more common in industry today and will be more so in the near future with new equipment installations and revamps on older equipment. This new equipment for a period of time generally requires little maintenance and the manufacturer probably handles problems for the first year. As the equipment ages and the responsibility to maintain it falls on the industrial maintenance people, the training or lack of training impact reveals itself.

Generally, a crash program of one or two weeks duration follows the installation of a new line or updating of control on an older installation. The men absorb a lot in a short time, but there is very little time to digest sufficiently for retentive purposes an adequate amount of the material covered. Often times the design engineers who have lived with the control from its start conduct these sessions. They understand the circuitry thoroughly but in many instances take a lot for granted and don't give the students a proper understanding of the overall system operation or how the control system accomplishes its purpose. There is a tendency to get directly into the theory of semiconductors or the design circuitry itself. My intention is not to be cricical because on one hand the design engineer probably doesn't understand too well what a blast furnace does or perhaps has never seen a hot strip mill operate and on the other hand, the technician probably doesn't grasp very rapidly, without experimenting with it, the latest circuit design capabilities. Each most likely feels more comfortable in the area he is most familiar with. Thus the design engineer will tend to stick with circuit design and operation while avoiding the overall system functions and the technician on the other hand, will probably be somewhat overwhelmed with his lack of understanding of the circuit details and quietly absorb what information he can.

From the training standpoint and for the average technician or maintenance man, a better approach would be to review the operation of the facility involved (Blast Furnace, Hot Strip, etc.) using flow diagrams, photographs, etc. and then take an individual unit (skip car, turnaround, etc.) and show how the control will accomplish the operations involved for that unit. Next, take a second unit (perhaps a little more advanced) break it down and show how the control accomp-

lishes this function. After general descriptions of what the control is expected to do, the basic building blocks can be developed and then the more complex circuitry of the building blocks can be explained.

It is probably critical to proper understanding that the individual get his hands on the parts and experiment with them. This is the basic intent of my thesis, that a technician by experimentation with inputs and outputs and interconnections of various logic devices will be more adequately equipped to maintain and understand industrial logic systems.

### CHAPTER II

# THEORY AND BASIC BUILDING BLOCKS

In comparing relay type circuits and static logic circuits, consider the following comparison

#### TABLE 1

avitch repre

### RELAY-STATIC LOGIC COMPARISON

Relay Control Static Control

Input Devices Input Devices Push buttons Limit switches

Relays

Output Devices Contactors Solenoids

Push buttons Limit switches

Control Devices Control Devices Static logic

> Output Devices Contactors Solenoids

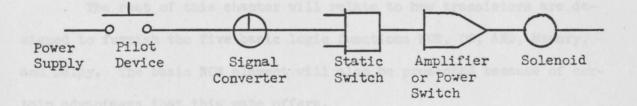

Figure 1 shows a basic diagram for a static logic control system.

# FIG. 1.--BASIC LOGIC SYSTEM

The power supply provides the required d.c. voltages for the operation of the static control components. This is generally 5, 10, or

24 volts, although higher voltages might be required for better reliability of the pilot devices and output devices.

The pilot devices could consist of push buttons, selector switches, limit switches or other similar devices for initiating intelligence for the control circuit. These pilot devices do not operate satisfactorily at low energy levels encountered in static switching. Higher voltages are needed to break through the contact resistance of these devices. The signal converter converts the higher energy level used by the pilot device to a lower level compatible with static logic components.

The static switch represents logic gates or static switches that are capable of driving other static switches either singly or as multiple units. The number of static switches used is determined by the complexity of the control required of the system.

The amplifier or power switch is a static switch capable of switching higher levels of power. The purpose of the power switch is to increase the output power level sufficiently to drive output devices such as relays, solenoids, and contactors.

The output device operates that which the system has been designed to control. It could be a starter for a motor, a solenoid for providing mechanical movement or a relay for energizing a bell or an alarm.

The rest of this chapter will relate to how transistors are designed to furnish the five basic logic functions NOT, OR, AND, Memory, and Delay. The basic NOR element will also be presented because of certain advantages that this gate offers.

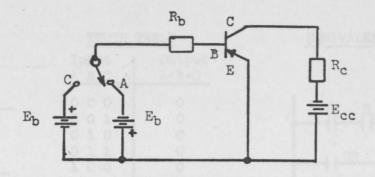

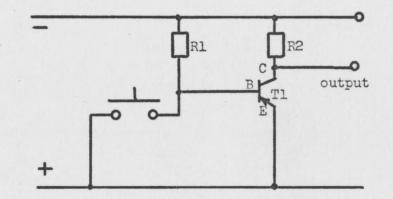

A very brief explanation might be appropriate here to indicate how a transistor functions as a switch. For use as a switching device the transistor is generally used in the common emitter configuration. Figure 2 shows a basic transistor switch.

FIG. 2 .-- BASIC TRANSISTOR SWITCH

The control of current between the collector and emitter of the transistor is controlled by the base bias. If the base is made more negative then the emitter, the emitter junction is biased in the forward directcurrent flows across the emitter junction to the collector. ion and It requires only a small current in the base to control a larger current flowing through the collector-emitter path. When the switch is in position C the transistor is held in cutoff, because the base emitter junction is blased in a reverse direction, and no current flows from emitter to collector. Thus, we might say the emitter to collector switch is open. As the current applied to the base becomes negative enough saturation results and there is an extremely low impedance between collector and emitter. So if the switch is moved from C to A and back to C the collector to emitter path rapidly switches from a very high impedance state to a very low impedance state and back to the high impedance state. This is the basic operation of the transistor as a switch.

# The "AND" Function

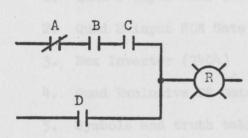

The AND logic function is accomplished by a device which produces an output only when every input is energized. Symbols encountered for this function, the truth table, and the equivalent relay circuit are

### given in Figure 3.

| SYMBOLS        | TRUTH             | TABLE           | EQUIVALENT RELAY CIRCUIT |

|----------------|-------------------|-----------------|--------------------------|

| an output when | Input<br>A B C    | Output<br>A•B•C |                          |

|                | 000               | 0               |                          |

| A              | 010<br>011<br>100 | 0               |                          |

|                | 101<br>111        | 0<br>1          | l output l               |

# FIG. 3 .-- THE "AND" FUNCTION

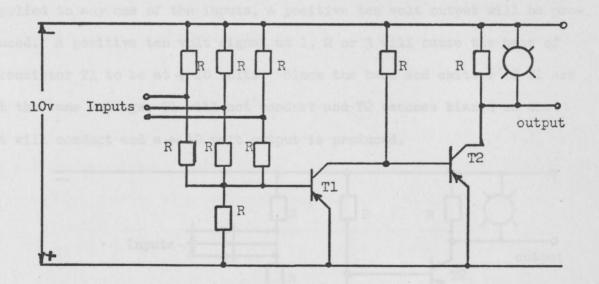

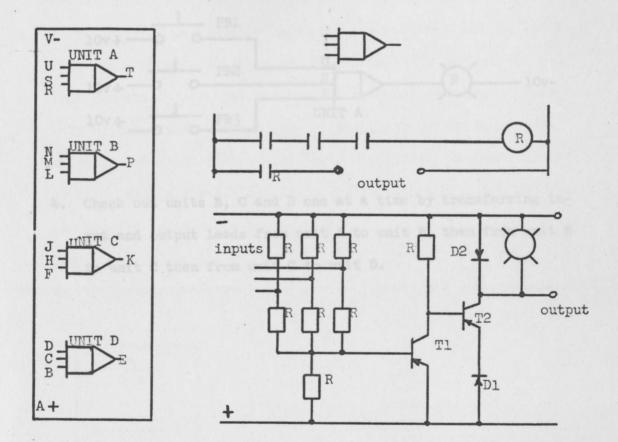

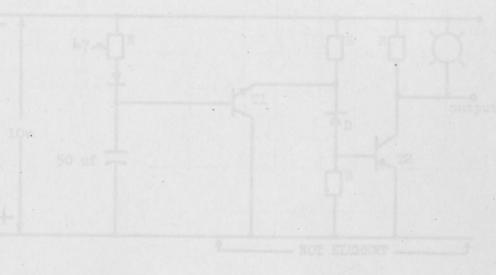

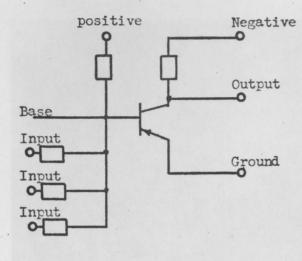

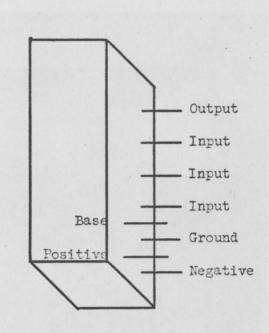

Figure 4 shows a three input AND. When all three inputs have a ten volt signal applied, a positive ten volt output will be produced. If any of the inputs do not have a positive ten volt signal, a negative voltage will appear at the base of transistor Tl causing it to conduct. This in turn prevents transistor T2 from conducting and no output voltage will be present. All inputs must be present to obtain an output.

FIG. 4 .-- THE "AND" CIRCUIT

277087

7

LIBRARY

### The "OR" Function

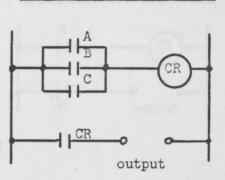

The OR logic function is accomplished by a device which produces an output when one or more of the inputs are energized. Symbols encountered for this function, the truth table, and the equivalent relay circuit are given in Figure 5.

SYMBOLS

| TRUTH                                                  | TABLE                 |

|--------------------------------------------------------|-----------------------|

| Input<br>A B C                                         | Output<br>A+B+C       |

| <br>0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1 | 0<br>1<br>1<br>1<br>1 |

| 110                                                    | 1                     |

EQUIVALENT RELAY CIRCUIT

FIG. 5.--THE "OR" FUNCTION

Figure 6 shows a three input OR. When a positive ten volts is applied to any one of the inputs, a positive ten volt output will be produced. A positive ten volt signal at 1, 2 or 3 will cause the base of transistor T1 to be at + 10 volts. Since the base and emitter of T1 are at the same voltage, T1 will not conduct and T2 becomes biased so that it will conduct and a + 10 volt output is produced.

FIG. 6.--THE "OR" CIRCUIT

# The "NOT" (Inverter) Function

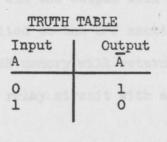

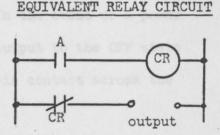

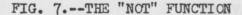

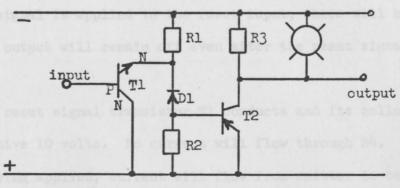

The NOT (Inverter) function is accomplished by a device which produces an output only when the input is not energized. Symbols encountered for this function, the truth table, and the equivalent relay circuit are given in Figure 7.

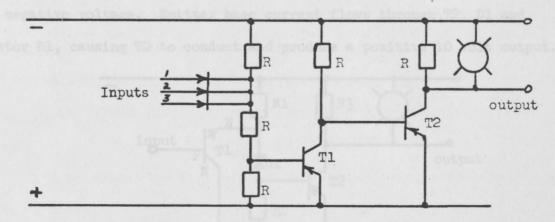

Figure 8 shows a typical NOT element circuit. A positive ten volt signal at the input will produce no output. When there is no positive ten volt input, there will be a positive ten volt output. If the input is at positive ten volts, current will flow through transistor T1 from base to emitter through resistor R1 to the negative side of the line, causing T1 to conduct. This makes the base of transistor T2 more positive, preventing it from conducting so that no output is produced. No positive input signal means T1 will not conduct and its emitter will be at a negative voltage. Emitter base current flows through T2, D1 and resistor R1, causing T2 to conduct and produce a positive 10 volt output.

FIG. 8.--THE "NOT" CIRCUIT

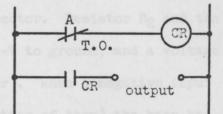

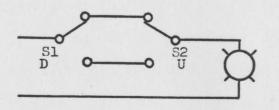

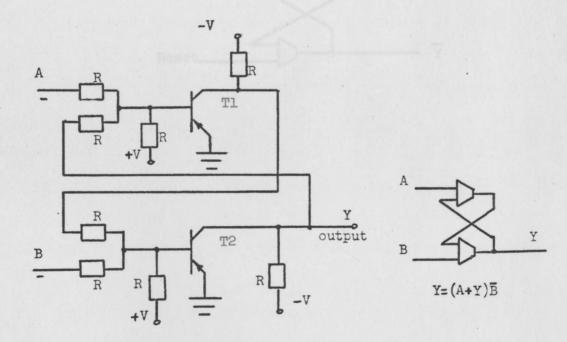

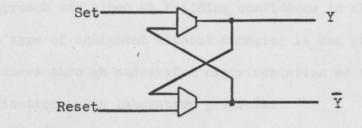

### The OFF-RETURN (Set-Reset) Memory

The OFF-RETURN function is accomplished by a device which returns the condition of output corresponding to the input last energized, except upon interruption of power, it returns to the off condition. As in the case of a seal-in relay circuit, a momentary signal to the A section will turn the unit on and the output will continue indefinitely until a B input signal is applied to the OFF section. In the event of a power failure, the OFF-RETURN memory will return the output to the OFF state as in the case of the relay circuit with a seal-in contact across the start button.

#### SYMBOLS

### EQUIVALENT RELAY CIRCUIT

## FIG. 9 .- - THE OFF-RETURN MEMORY FUNCTION

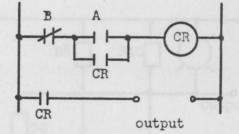

Figure 10 shows a set-re<sub>30</sub>t memory circuit. If the set input receives a momentary + 10 volt signal, a +10 volts will be produced at the output and will remain even after the input set signal is removed. If a + 10 volt signal is applied to the reset input, there will be no output, and the output will remain off even after the reset signal is removed.

With no reset signal transistor Tl conducts and its collector will be at positive 10 volts. No current will flow through R<sup>4</sup>. If no set signal is being applied, current will flow from emitter to base of

transistor T2, through diode D1, and resistors R9 and R10, causing transistor T2 to conduct. Transistor T3 will not conduct and the output will be zero.

When a + 10 volt set signal is applied, no current can flow through diode Dl, base current of transistor T2 stops and T2 cuts off. Transistor T3 conducts and a + 10 volts output is produced. Removal of the set signal causes no change since T3 and resistor R9 provide a + 10volts to Dl, keeping T2 turned off.

Applying the reset signal causes the base and emitter of Tl to be at the same potential. Tl will not conduct and current will flow from emitter to base of T2 through R4 and R1. T2 conducts preventing T3 from conducting and the positive 10 volt output goes to zero.

Fig. 10.--THE OFF-RETURN MEMORY CIRCUIT

### The Retentive Memory

The retentive memory is accomplished by a device which retains the condition of output corresponding to the input last energized. The retentive memory always remembers the state which last existed after the restoration of power following a power failure. It is turned on and off exactly as is the off-return memory unit but in addition, when power returns after an outage, the circuit will be restored to the ON state if that was its original condition or to the OFF state if that was its original condition.

In relay circuitry retentive memory is accomplished by a device has two coils, one of them picks up the relay. (equivalent to the A input of the logic unit) after which a mechanical latch holds it in the energized position following the de-energization of the operating coil, and the second coil (corresponding to the B input of the logic unit) unlatches the unit when it is desired to open the relay. Refer to Figure 11.

SYMBOLS

### EQUIVALENT RELAY CIRCUIT

FIG. 11 .-- THE RETENTIVE MEMORY FUNCTION

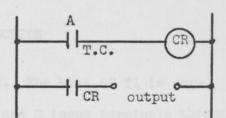

### The Delay Function

The delay function is accomplished by a device that produces an output after a definite intentional time delay after its input is energized (time delay energizing), or else whose output is de-energized following a definite intentional time delay after its input is de-energized (time delay de-energizing).

Delay components perform the same functions as timers in conventional relay circuits. The two general types are ON delay (output produced following a definite intentional time delay after input is energized), and OFF delay (output removed following a definite intentional time delay after input is de-energized). Refer to Figure 12.

ON DELAY

SYMBOL

OFF DELAY

SYMBOL

EQUIVALENT RELAY CIRCUIT

#### EQUIVALENT RELAY CIRCUIT

Output

ON AND OFF DELAY

SYMBOLS

FIG. 12.--THE DELAY FUNCTION

## The NOR Function

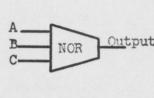

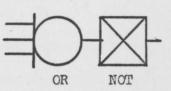

The NOR function is accomplished by a circuit that combines the OR and NOT functions together. This is called NOR logic since we get an output if neither A NOR B NOR C is present. The NOR circuit would become a simple NOT if only one input were used. This device can be used to handle the AND, OR, NOT and memory functions.

SYMBOL

TRUTH TABLE

| A | B | c | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 1 | 0 | 0 | 0      |

| 0 | 1 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 0      |

| 1 |   | 1 | 0      |

|   |   |   |        |

COMPARES TO

FIG. 13 .-- THE NOR FUNCTION

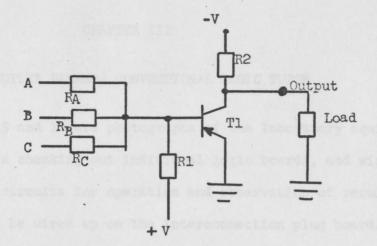

Figure 14 shows a three input NOR. The base of Tl is connected to + V(reverse bias) and to A, B, and C input terminals through three resistors  $R_A$ ,  $R_B$  and  $R_C$ . With no negative input signal at A nor B nor C there is no emitter-base current and the transistor is in effect an open circuit emitter to collector. Resistor  $R_2$  and the load are in series across the potential -V to ground, and a voltage will appear across a load (output resistor). When a negative input is applied to A or B or C (or any combination of them) the base becomes negative with respect to the emitter and current will pass from emitter to base and thus grounds the collector. This results in the load resistor being short circuitd and there is no output.

### CHAPTER III

DSL (CUTLER HAMMER) CONVENTIONAL LOGIC TUTOR

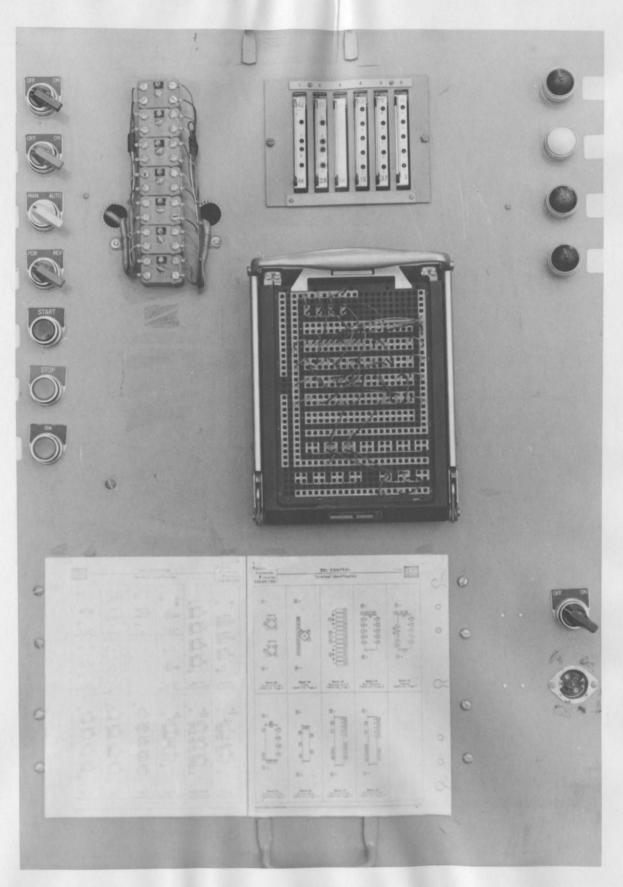

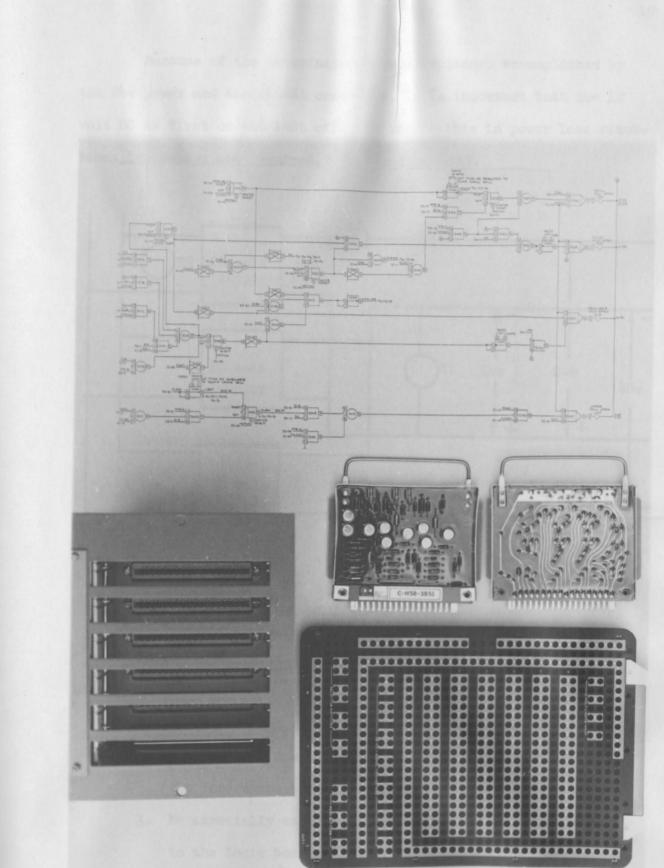

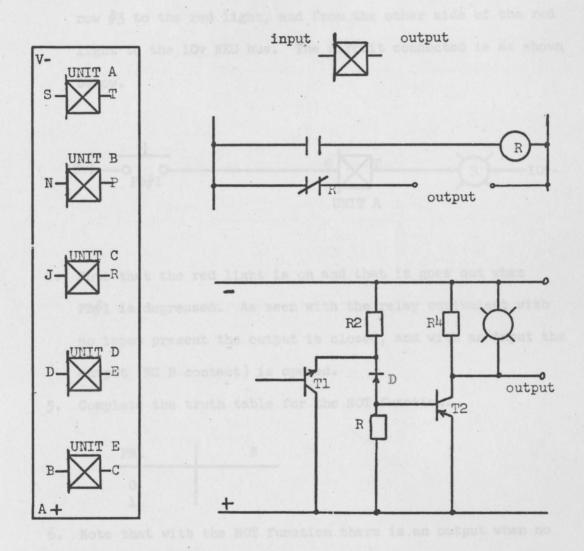

Figures 15 and 16 are photographs of the laboratory equipment to be used in checking out individual logic boards, and wiring up various logic circuits for operation and observation of results. All circuits will be wired up on the interconnection plug board. Note the four selector switches and three push buttons along the left side, the four indicating lights along the right side, the on-off switch at the lower right, the bucket that can accommodate up to six logic boards at a time, and the interconnection plug board where all wiring will be done.

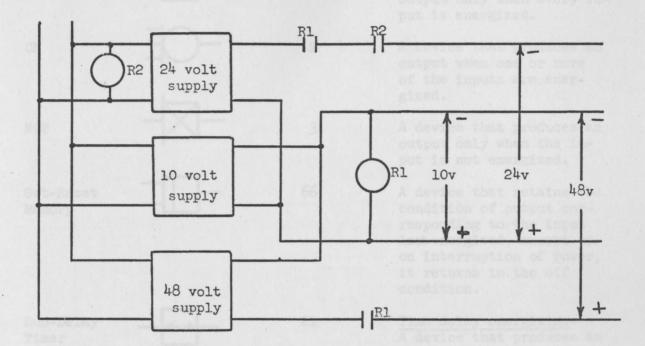

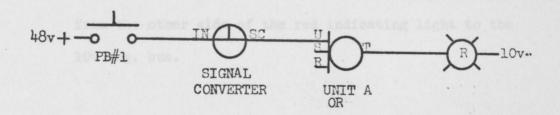

The power supply provides 48v, 24v and 10v filtered direct current which is available on the interconnection plug board as marked on the corresponding buses. Depending on what components are used, one, two or three different voltages may be used in the static switching control. These voltages are related as indicated in Figure 17.

FIG. 15.--LOGIC TUTOR (DSL)

FIG. 16 .-- DSL CIRCUIT BOARD AND INTERCONNECTION BOARD

Because of the interfacing between voltages accomplished by the 24v power and the signal converter, it is important that the 10 volt DC is first on and last off. To insure this in power loss situations two relays are required. Refer to figure 17.

FIG. 17 .-- DSL POWER SUPPLY

In the experiments that follow, certain precautions must be observed.

- 1. Never pull out or insert boards while power is on.

- 2. Turn power off when making or breaking connections on the interconnection plug board.

- Be especially careful not to apply 24 or 48 volt power to the logic boards.

- 4. If at all in doubt about the circuitry, have an instructor check it out before applying power.

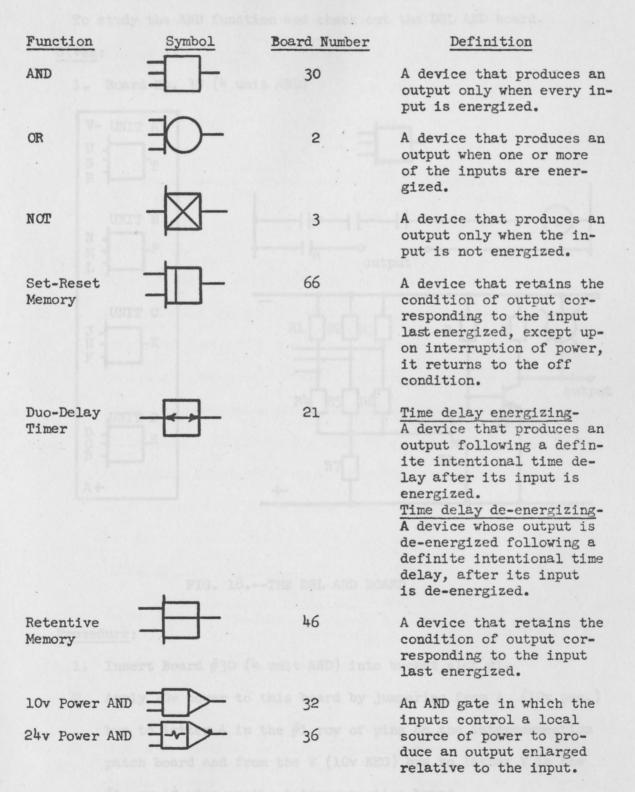

# TABLE 2

# CONVENTIONAL LOGIC SYMBOLS AND DEFINITIONS

Experiment 1 (The AND Function)

# Object:

To study the AND function and check out the DSL AND board.

# Given:

1. Board No. 30 (4 unit AND)

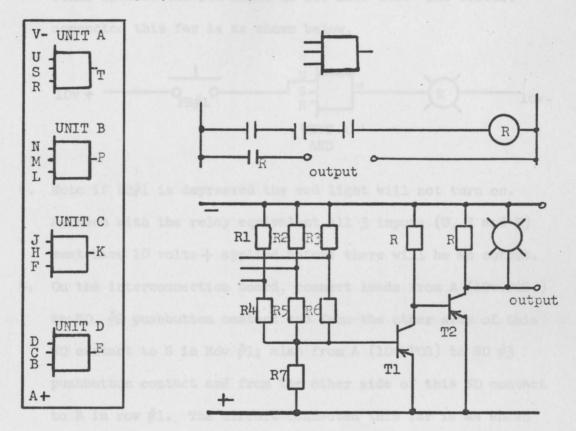

FIG. 18 .-- THE DSL AND BOARD

# Procedure:

- 1. Insert Board #30 (4 unit AND) into bucket slot #1.

- 2. Apply 10v power to this board by jumpering from A (10v pos.) bus to letter A in the #1 row of pins on the interconnection patch board and from the V (10v NEG) bus to letter V in the #1 row of pins on the interconnection board.

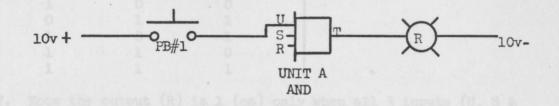

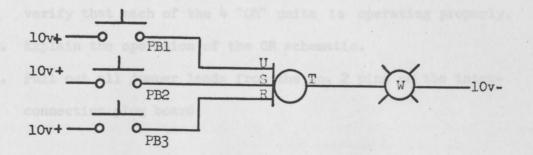

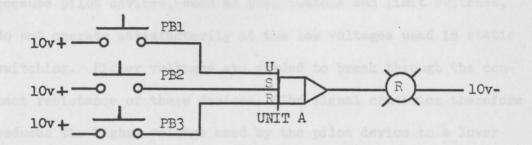

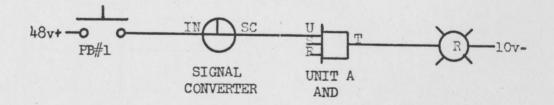

3. On the interconnection board connect leads from A (+10v) to normally open #1 pushbutton contact; from the other side of the the NO pushbutton contact to U in Row #1 (first input of unit A AND): from T in Row #1 to the red light, and from the other side of the red light to 10v NEG. bus. The circuit connected this far is as shown below.

- 4. Note if PB#1 is depressed the red light will not turn on.

As seen with the relay equivalent all 3 inputs (U, S and R)

must have 10 volts + applied before there will be an output.

- 5. On the interconnection board, connect leads from A (10v POS.) to NO #2 pushbutton contact and from the other side of this NO contact to S in Row #1; also from A (10v POS) to NO #3 pushbutton contact and from the other side of this NO contact to R in row #1. The circuit connected this far is as shown below.

10v + PEl 0 0 10v + PE2 0 0 S P R 10v - 10v + PE3 0 0

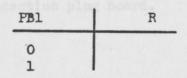

6. Complete the truth table by examining each of the possible combinations of depressing the 3 push buttons. If the red

light is on, put a 1 in the R column, and if the light is off, put a 0 in the R column for each of the 8 possible combinations for pushing the 3 buttons.

| PBL | PB2 | PB3 | R .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 0   | 1   | in the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 1   | 0   | and the second se |

| 1   | 0   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 1   | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | 0   | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | 1   | 0   | a sea a s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | 1   | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

- 7. Note the output (R) is 1 (on) only when all 3 inputs (U, S & R) are 1 (energized). This constitutes the AND function that says when all three inputs have a + 10 volts applied a + 10v output will be produced.

- 8. Transfer the input and output leads from unit A to unit B. That is in row #1 of the interconnection board move U to N, S to M, R to L and T to P. Check out unit B "AND" by verifying that there will only be an output (red light on) when all three pushbuttons are depressed.

- Check out unit C AND and unit D AND in a similar manner to verify that each of the 4 AND units are operating properly.

- 10. Explain the operation of the AND schematic.

- Pull out all jumper leads from the No. 1 pins on the interconnection plug board.

bus to letter A in the #2 row of pins on the inte

Experiment 2 (The OR Function)

Object:

To study the OR function and check out the DSL OR board.

Given:

1. Board No. 2 (4 unit OR)

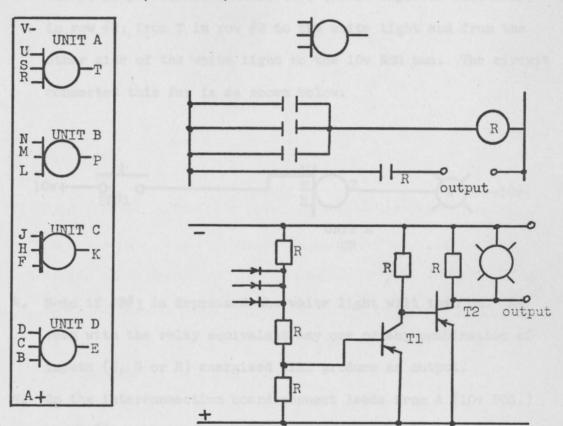

FIG. 19 .-- THE DSL OR BOARD

# Procedure:

- 1. Insert Board #2 (4 unit OR) into bucket slot #2.

- Apply 10v power to this board by jumpering from A (10v POS.)

bus to letter A in the #2 row of pins on the interconnection

patch board and from the V (lOv NEG.) bus to letter V in the #2 row of pins on the interconnection board.

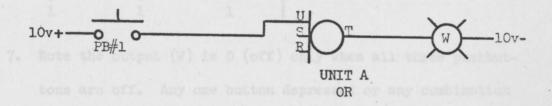

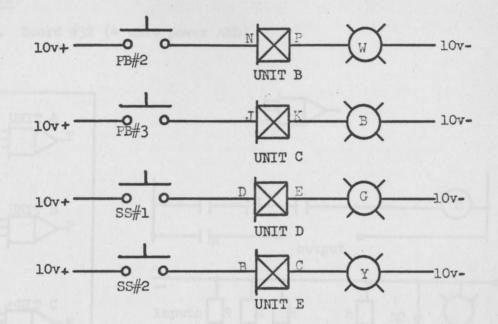

3. On the interconnection board, connect leads from A (lov POS.) to normally open #1 pushbutton contact; from the other side of the NO #1 pushbutton contact to U (first input of unit A OR) in row #2; from T in row #2 to the white light and from the other side of the white light to the lov NEG bus. The circuit connected this far is as shown below.

- 4. Note if PB#1 is depressed the white light will turn on. As seen with the relay equivalent any one or any combination of inputs (U, S or R) energized will produce an output.

- 5. On the interconnection board connect leads from A (10v POS.) to NO #2 pushbutton contact and from the other side of this NO contact to S in row #2; also from A (10v POS.) to NO #3 pushbutton contact and from the other side of this NO contact to R in row #2. The circuit connected this far is as shown below.

6. Complete the truth table by examining each of the possible combinations of depressing the 3 push buttons. If the white light is on put a 1 in the W column, and if the light is off put a 0 in the W column for each of the 8 possible combinations for pushing the 3 buttons.

| PBL | PB2 | PB3 | W |

|-----|-----|-----|---|

| 0   | 0   | 0   |   |

| 0   | 0   | 1   |   |

| 0   | 1   | 0   |   |

| 1   | 0   | 0   |   |

| 0   | 1   | 1   |   |

| 1   | 0   | 1   |   |

| 1   | 1   | 0   |   |

| 1   | 1   | 1   |   |

- 7. Note the output (W) is 0 (off) only when all three pushbuttons are off. Any one button depressed or any combination of the three depressed will produce an output. This consititutes the OR function that says when any one or any combination of inputs have a + 10 volts applied a + 10v output will be produced.

- 8. Transfer the input and output leads from unit A to unit B. That is in row #2 of the interconnection board move U to N, S to M, R to L and T to P. Check out unit B "OR" by verifying that there will be an output if any one or any combination of inputs are energized.

- 9. Check out unit C "OR" and unit D "OR" in a similar manner to verify that each of the 4 "OR" units is operating properly.

- 10. Explain the operation of the OR schematic.

- 11. Pull out all jumper leads from the No. 2 pins on the interconnection plug board.

Experiment 3 (The NOT Function)

Object:

To study the NOT function and check out the DSL NOT board. Given:

1. Board No. 3 (5 unit NOT)

FIG. 20.--THE DSL NOT BOARD

#### Procedure:

- 1. Insert Board #3 (5 unit NOT) into bucket slot #3.

- Apply 10v power to this board by jumpering from A (10v POS) bus to letter A in the #3 row of pins on the interconnection

patch board, and from the V (10v NEG) bus to letter V in the #3 row of pins on the interconnection board.

3. On the interconnection board, connect leads from A (10v POS) to normally open #1 pushbutton contact; from the other side of the NO #1 pushbutton contact to S in row #3; from T in row #3 to the red light, and from the other side of the red light to the 10v NEG bus. The circuit connected is as shown below.

- 4. Note that the red light is on and that it goes out when PB#1 is depressed. As seen with the relay equivalent with no input present the output is closed, and with an input the output (NC R contact) is opened.

- 5. Complete the truth table for the NOT function.

- Note that with the NOT function there is an output when no input is present and there is no output when the input is present.

- 7. Set up the following circuits to check out each of the other NOT units on the NOT board.

- 8. Explain the operation of the NOT schematic.

- Pull out all jumper leads from the No. 3 pins on the interconnection plug board.

Experiment 4 (The 10v Power AND)

Object:

To check out the DSL lOvolt power AND board.

Given:

1. Board #32 (4 unit power AND)

FIG. 21 .-- THE DSL POWER AND BOARD

Procedure:

- 1. Insert Board #32 (4 unit power AND) into bucket slot #5.

- 2. Apply 10v power to this board by jumpering from A bus to let-

ter A in the #5 row of the interconnection patch board, and from V bus to letter V in the #5 row on the interconnection board.

.3. Set up the following circuit to check out unit A power AND.

4. Check out units B, C and D one at a time by transferring input and output leads from unit A to unit B, then from unit B to unit C then from unit C to unit D. Experiment 5 (D.C. Signal Converter)

Object:

To check out and apply the d.c. signal converter.

#### Information:

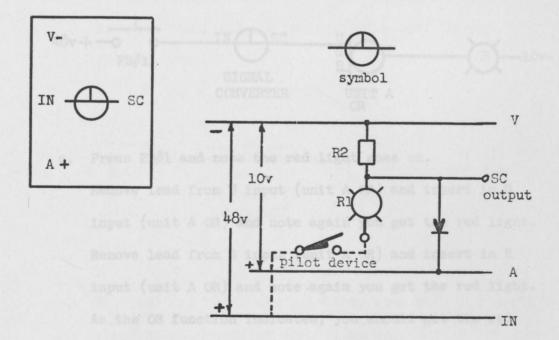

The signal converter is necessary in most practical applications because pilot devices, such as push buttons and limit switches, do not operate satisfactorily at the low voltages used in static switching. Higher voltages are needed to break through the contact resistance of these devices. The signal converter therefore reduces the higher voltage used by the pilot device to a lower voltage compatible with static logic circuitry. A signal converter is a voltage divider and it lowers the pilot device voltage to the desired voltage for logic units.

#### Given:

1, DC Signal Converter

FIG. 22.--THE DSL D.C. SIGNAL CONVERTER

#### Procedure:

- Wire up the A unit of the OR board and an indicating light from the output of a signal converter. To do this see that the OR board is in bucket slot #2 and wire as follows:

- Apply 10v power to the OR board by jumpering from A

bus and V bus to A and V respectively on #2 row of the

interconnection plug board.

- b. Jumper from 48v + bus to the normally open contact on PB#1, from the other side of PB#1 to the in terminal of the signal converter. Jumper from A bus and V bus to A and V respectively on the signal converter. Jumper from SC (signal converter output) to U (input of unit A OR). Jumper from T (output or unit A OR) to the red indicating light and from the other side of the red indicating light to the lOv neg. bus.

c. Press PB#1 and note the red light goes on. Remove lead from U input (unit A OR) and insert in S input (unit A OR) and note again you get the red light. Remove lead from S input (unit A OR) and insert in R input (unit A OR) and note again you get the red light. As the OR function indicates, you should get the red light if U or S or R or any combination of them is energized.

d. Remove all jumpers from the interconnection board.

2. Wire up the A unit of the AND board and an indicating light from the output of a signal converter. To do this see that the AND board is in bucket slot #1 and wire as follows:

a. Apply lov power to the AND board by jumpering from A bus and V bus to A and V respectively on #1 row of the interconnection plug board.

b. Apply lov power to the signal converter by jumpering from A bus and V bus to A and V respectively for the signal converter on the interconnection plug board.

c. Jumper from the 48v + bus to the N.O. contact on PB#1, from the other side of PB#1 to the in terminal of the signal converter. Jumper from SC (signal converter output) to U (input of unit A AND). Jumper from T (output of unit A AND) to the red indicating light and from the other side of the red indicating light to the lOv neg. bus.

d. Note the red light does not go on when PB#1 is pressed since unused inputs of any AND units must have l0volts+

applied to them. Jumper from A (10v+bus) to both S and R inputs of the unit A AND. Now when PB#1 is pressed, the red light goes on. Since U, S and R inputs are energized (10 volts + applied) the red light (output) lights.

Example resetting a set reset amony to the no output condition. When the 10 wolt power is first turned on, the transistors in the system start turning on. In elements such as ARDS, ORS, and NOTS the inputs originating from limit switches and pushbuttons insure that the proper transistors end up conducting. Memory type dirouits, those that pick up on a short signal and latch in, however cannot have their input states predictable without a resetting action. For this reason a mister reset terminal is provided that resets all elements on the board. The master reset terminal should be held argetive to reset and then positive to

FIG. 23. -- THE RESET GATE

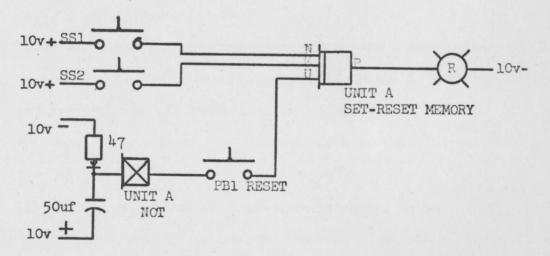

Experiment 6 (Set-Reset Memory)

Object:

To study Set-Reset Memory and check out the DSL Set-Reset Memory board.

Information:

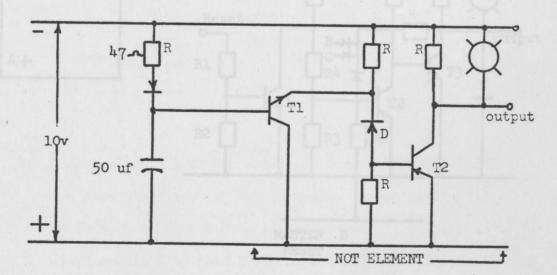

The term reset means returning a switch to a predetermined state. Example resetting a set reset memory to the no output condition. When the 10 volt power is first turned on, the transistors in the system start turning on. In elements such as ANDS, ORS, and NOTS the inputs originating from limit switches and pushbuttons insure that the proper transistors end up conducting. Memory type circuits, those that pick up on a short signal and latch in, however cannot have their input states predictable without a resetting action. For this reason a master reset terminal is provided that resets all elements on the board. The master reset terminal should be held negative to reset and then positive to permit normal operation.

FIG. 23.--THE RESET GATE

This reset gate plus a set-reset memory can be used to provide under voltage protection.

#### Given:

- 1. Board No. 66 (3 unit set-reset memory)

- 2. Board No. 3 (5 unit NOT)

- 3. Reset resistor-capacitor network

FIG. 24 .-- THE DSL SET-RESET MEMORY BOARD

#### Procedure:

- Insert Board #66 (3 unit Set-Reset Memory) into bucket slot #4. Insert Board #3 (4 unit NOT) into bucket slot #5.

- 2. Apply 10v power to board #66 by jumpering A bus and V bus to respective letters in the #4 row on the interconnection patch board. Apply 10v power to board #3 by jumpering A bus and V bus to respective letters in the #5 row on the interconnection patch board.

- 3. Hook up the following circuit to check out the A unit of the set-reset memory board. Notice seal-in effect for each of the set inputs and the drop out or reset effect when PB#1 is pressed. Compare this circuit to the equivalent relay circuit.

4. Check out unit B on the set-reset memory board by keeping the same circuitry but interchanging respective inputs (N to H, M to J, and U to L) and respective outputs (P to K) from unit A to unit B of the set reset memory on the interconnection plug board.

5. Check out unit C on the set-reset memory board by keeping the same circuitry but interchanging respective inputs (H to B, J to C, and L to F) and respective outputs (K to E) from unit B to unit C of the the set reset memory on the interconnection plug board.

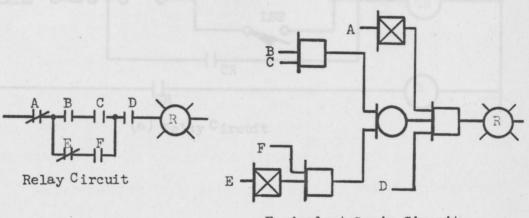

alay Circuit

Experiment 7 (Interconnecting DSL Gates)

Object:

To become better acquainted with interconnections between logic gates and to be better able to compare relay circuitry with its equivalent in DSL logic circuitry.

Given:

- 1. Board #30 (4 unit AND)

- 2. Board #2 (4 unit OR)

- 3. Board #3 (5 unit NOT)

- 4. Board #32 (4 unit 10v power AND)

- 5. 4 signal converters

Procedure:

- Plug in logic boards, 30, 2, 3, and 32 into bucket slots

1, 2, 3 and 4 respectively.

- 2. Apply 10v power for each board and the 4 signal converters by jumpering from the 10v + and from the 10v bus to each board and converter on the interconnection plug board. NOTE: Do not remove these power feed connections when told to remove jumpers.

- Compare the relay and DSL logic circuits given below. Wire up the logic circuit and compare its operation to the relay circuit. Remove jumpers.

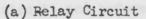

Relay Circuit

Equivalent Logic Circuit

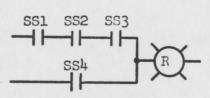

4. Compare the relay equivalent circuit and the DSL logic circuits given below. Wire up the logic circuit and compare its operation to the relay circuit. Use SS1, SS2, SS3, SS4, PB1 and PB2 for A B C D E and F respectively. Remove jumpers.

Equivalent Logic Circuit

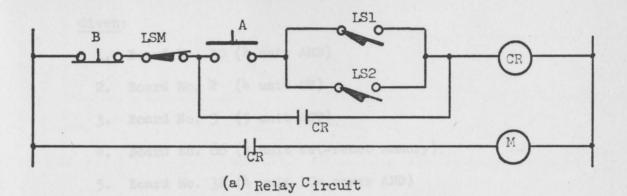

5. Compare the relay circuit and the equivalent conventional logic circuit. Wire up the logic circuit and compare its operation to the relay circuit. Refer to Figure 25. Caution: Have instructor check out the circuit before turning on the power. It is very important that you don't apply 48 volts to any logic gates. The 48v + bus should go through the selector switches and pushbuttons and only to the in terminal of the signal converters. Remember that any unused inputs of AND gates must be connected to 10v + bus.

1

b) Equivalent Logic Circuit

FIG. 25 .-- REIAY AND STATIC LOGIC COMPARISON NO. 1

Experiment 8 (A DSL Logic Circuit)

Object:

This experiment will give a comparison of relay circuitry and equivalent DSL logic circuitry.

Given:

- 1. Board No. 30 (4 unit AND)

- 2. Board No. 2 (4 unit OR)

- 3. Board No. 3 (5 unit NOT)

- 4. Board No. 66 (3 unit set-reset memory)

- 5. Board No. 32 (4 unit 10v power AND)

- 6. Relay circuit and circuit requirements

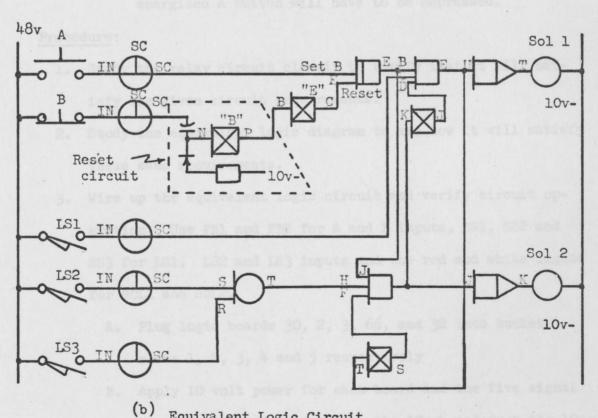

- 7. Corresponding logic circuit to satisfy same requirements. Refer to Figure 26.

Equivalent Logic Circuit

FIG. 26 .- - RELAY AND STATIC LOGIC COMPARISON NO. 2

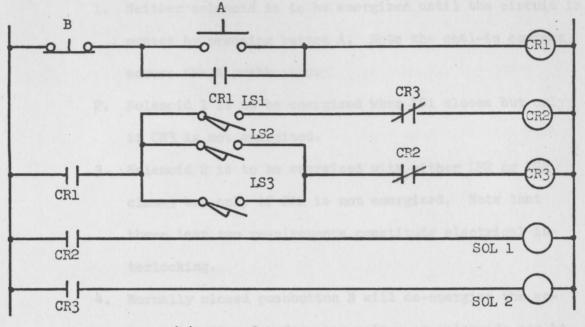

#### Circuit requirements

- Neither solenoid is to be energized until the circuit is preset by pressing button A. Note the seal-in contact across the A pushbutton.

- Solenoid 1 is to be energized when LS1 closes but only if CR3 is not energized.

- 3. Solenoid 2 is to be energized with either LS2 or LS3 closed but only if CR2 is not energized. Note that these last two requirements constitute electrical interlocking.

- 4. Normally closed pushbutton B will de-energize the entire circuit and before any relays or solenoids can be energized A button will have to be depressed.

#### Procedure:

- Study the relay circuit closely to verify that it will satisfy the given circuit requirements.

- Study the equivalent logic diagram to see how it will satisfy these same requirements.

- 3. Wire up the equivalent logic circuit and verify circuit operation. Use PB1 and PB2 for A and B inputs, SS1, SS2 and SS3 for LS1. LS2 and LS3 inputs and the red and white lights for SOL1 and SOL2.

- A. Plug logic boards 30, 2, 3, 66, and 32 into bucket slots 1, 2, 3, 4 and 5 respectively

- B. Apply 10 volt power for each board and the five signal converters by jumpering from the 10v + and from the 10v bus to each board or converter on the interconnection

plug board.

C. Wire from the 48v+ bus through the selector switches and push buttons to the signal converters. Note: This is the only place the 48v + bus should be connected. It is very important that 48 volts are not applied to any logic gates. Follow the diagram closely and wire up the rest of the circuit. Note also that any unused AND gate inputs must be connected to the 10v + bus. Be sure the instructor checks your circuit before you apply power.

# CHAPTER IV

# ADDITIONAL THEORY

# Boolean Algebra

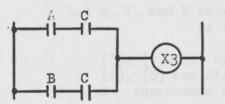

Any given contact circuit can be represented by an equation or in word form. Having any one of the three the other two can be obtained at will. The following table illustrates this for switching variables A, B, C, . . . and relays X1, X2, X3, . . . TABLE 3

THE BOOLEAN STRUCTURE

Equation Form X1= A·B·C

X2 = A+B+C

# Word Form

X1 will be energized if A AND B AND C are closed.

X2 will be energized if A OR B OR C is closed

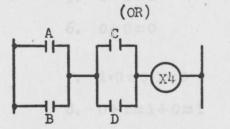

$A \qquad (OR)$   $B \qquad C \qquad X3$   $A \qquad C \qquad X3$

X3 = AC + BC

(OR) X3=(A+B) C

X4 = AC+AD+BC+BD

X3 will be energized if A AND C are closed OR if B AND C are closed

(OR)

X3 will be energized if A OR B AND C are closed

X4 will be energized if A AND C, OR A AND D, OR B AND C, OR B AND D are closed.

20

(OR)

X4 = (A+B) (C+D)

X4 will be energized if A OR B, and C OR D are closed

(OR)

Some of the basic definitions, postulates and theorems of Boolean Algebra are summarized in Tables 4 and 5.<sup>1</sup>

The switching variables are two valued in the sense that they can represent only two states of operation. For this reason they can be referred to as binary variables.

#### TABLE 4

#### BOOLEAN DEFINITIONS AND POSTULATES

#### Definitions:

# Let X, Y, and Z represent circuit variables such as switches or relay contacts

('), (•), (+) are prime, dot, and plus operators

(1), (0) are digits representing states of inputs or outputs

0 represents an open circuit

1 represents a closed circuit

+ signifies a parallel connection

signifies a series connection

Postulates:

|    | X=0 if X≠1<br>X=1 if X≠0 | Shows that switching variables are actually binary variables and that at any given time either X=0 or X=1. |  |  |  |  |

|----|--------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    | 0•0=0                    | An open circuit in series with an open circuit is an open circuit.                                         |  |  |  |  |

| 4. | 1+1=1                    | A closed circuit in parallel with a closed circuit is a closed circuit.                                    |  |  |  |  |

| 5. | 1.1=1                    | A closed circuit in series with a closed circuit is a closed circuit.                                      |  |  |  |  |

| 6. | 0+0=0                    | An open circuit in parallel with an open<br>circuit is an open circuit.                                    |  |  |  |  |

| 7. | 1.0=0.1=0                | A closed circuit in series with an open<br>circuit in either order is an open circuit.                     |  |  |  |  |

| 8. | 0+1=1+0=1                | An open circuit in parallel with a closed<br>circuit in either order is a closed circuit                   |  |  |  |  |

|    | 0'=1<br>1'=0             | The opposite of the O state is the 1 state.<br>The opposite of the 1 state is the O state.                 |  |  |  |  |

|    |                          |                                                                                                            |  |  |  |  |

<sup>1</sup>Claude E. Shannon, "A Symbolic Analysis of Relay and Switching Circuits." AIEE Transactions. 1938. Vol.57, p. 713. It should be noted that duality relationships exist between postulates 3 and 4, between 5 and 6, and between 7 and 8. That is if each 1 digit in postulate 4 is changed to a 0 digit and the (+)operator is changed to the  $(\cdot)$  operator we obtain postulate 3 and likewise if every 0 digit in postulate 3 is changed to a 1 digit and the  $(\cdot)$  operator is changed to (+) operator we obtain postulate 4. Postulates 9 and 10 introduce negation or complementation. We can refer to 0 as the complement of 1 or we can refer to 1 as the complement of 0.

ality. Each of the paired duality relationships in tables 4 and 5

# TABLE 5

#### BOOLEAN THEOREMS

| 1.<br>2.   | $\begin{array}{c} x+y=y+x\\ x \cdot y=y \cdot x \end{array}$                             |                                                 |         |            |  |

|------------|------------------------------------------------------------------------------------------|-------------------------------------------------|---------|------------|--|

| 3.<br>4.   | X + (Y+Z)=(X+Y)+Z=X+Y+Z<br>$X \cdot (Y \cdot Z)=(X \cdot Y) \cdot Z = X \cdot Y \cdot Z$ | Associative 1<br>be omitted in<br>several terms | n a sum |            |  |

| 5.         | $X \cdot (Y+Z) = X \cdot Y + X \cdot Z$<br>$X + (Y \cdot Z) = (X+Y)(X+Z)$                | Distributive<br>out products                    |         |            |  |

| 7.<br>8.   | 1•X=X<br>0+X=X                                                                           |                                                 |         |            |  |

| 9.<br>10.  | 1+X=1<br>0•X=0                                                                           |                                                 |         |            |  |

| 11.<br>12. | $\begin{array}{c} x+x := 1 \\ x \cdot x := 0 \end{array}$                                |                                                 |         |            |  |

| 13.<br>14. | x+x=x<br>x•x=x                                                                           |                                                 |         |            |  |

| 15.<br>16. | (x)'=x'<br>(x')'=x                                                                       |                                                 |         | by Theorem |  |

| 17.<br>18. | x+xy=x<br>x•(x+y)=x                                                                      |                                                 |         |            |  |

| 19.<br>20. | (X+Y') Y=XY XY' + Y = X+Y                                                                |                                                 |         |            |  |

| 21.        | (X+Y) (Y+Z)(Z+X')=(X+Y)(<br>XY+ YZ+ZX'=XY+ZX'                                            | (Z+X*)                                          |         |            |  |

| 23.<br>24. | (X+Y+Z+)'=X'Y'Z'<br>(X•Y•Z•)'=X'+Y'+Z'+                                                  |                                                 |         | Ty Theorem |  |

| 25.        | (X+Y) (X'+Z)=XZ+X'Y                                                                      |                                                 |         |            |  |

Some time should be spent to visualize each of the postulates and theorems in terms of contact circuitry to try to justify each equality. Each of the paired duality relationships in tables 4 and 5 should also be studied to better understand the duality concept. The following example illustrates the application of theorems in simplifying or reducing the algebraic equations. The (') prime signifies a normally closed contact and is similar to the NOT function of the previous chapter. Thus -|B'| = -|B|. B' might also be represented by B meaning NOT B.

)]

Algebraic Representation and Reduction:

$$X2 = [A+(B \cdot C)] + [(A^{*} \cdot B^{*}) + A]$$

$$X2 = [A+(B \cdot C)] + [(A+A^{*}) (A+B^{*})]$$

$$X2 = [A+(B \cdot C)] + [(1) (A+B^{*})]$$

$$X2 = [A+(B \cdot C)] + [A+B^{*}]$$

$$X2 = A+B \cdot C+A+B^{*}$$

$$X2 = A+B \cdot C+B^{*}$$

$$X2 = A+(B^{*}+B) (B^{*}+C)$$

$$X2 = A+(1) (B^{*}+C)$$

$$X2 = A+B^{*}+C$$

Resulting Equivalent Circuit:

By Theorem 6 By Theorem 11 By Theorem 7 By Theorem 3 & 4 By Theorem 13 By Theorem 6 By Theorem 11 By Theorem 7

Proof of Equivalence:

| Inputs | 1. 101 | ef erre | 11.12 | -  | CA. PERCH | bitted the b |                      |                   |

|--------|--------|---------|-------|----|-----------|--------------|----------------------|-------------------|

| ABC    | B•C    | A+(B•C) | A '   | B' | A *• B*   | A+ (A'•B')   | Original<br>Equation | Final<br>Equation |

| 000    | 0      | 0       | 1     | 1  | 1         | 1            | 1                    | 1                 |

| 001    | 0      | 0       | 1     | 1  | 1         | 1            | 1                    | 1                 |

| 010    | 0      | 0       | 1     | 0  | 0         | 0            | 0                    | 0                 |

| 011    | 0      | 1       | 1     | 0  | 0         | 0            | 1                    | 1                 |

| 100    | 0      | 1       | 0     | 1  | 0         | 1            | 1                    | 1                 |

| 101    | 0      | 1       | 0     | 1  | 0         | 1            | 1                    | 1                 |

| 110    | 0      | 1       | 0     | 0  | 0         | 1            | 1                    | 1                 |

| 111    | 1      | 1       | 0     | 0  | 0         | 1            | 1                    | 1                 |

The truth tables for the original equation and the final equation are identical for each of the eight possible combinations of inputs assuring the equivalence of the two circuits.

Some working knowledge of truth tables can be gained by setting up truth tables for each side of the equality sign for some of the Theorems stated in Table 5. It should be noted that there are  $2^{N}$  possible combinations of N input variables. In the above circuit simplification there are 3 input variables (A, B and C), thus the truth table had to consider  $2^{3}$  or 8 possible combinations of these three variables.

# Conversions Between Conventional (Non-Inverting) and Inverting Logic

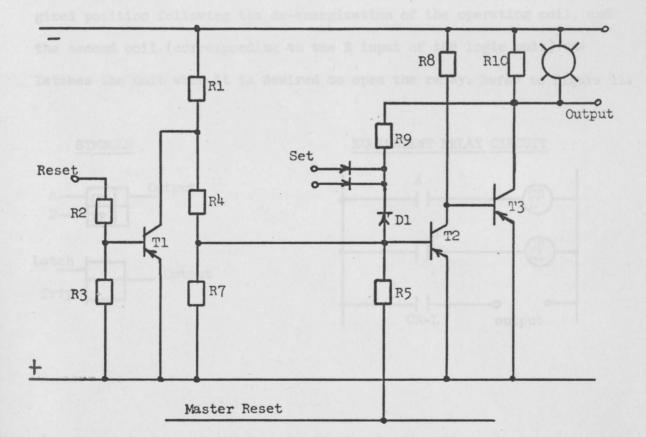

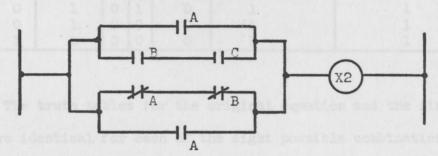

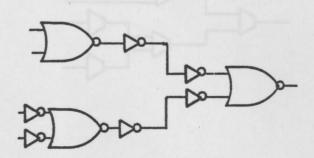

A brief circuit comparison between the non-inverting and the inverting type logic will now be made and we will complete this chapter with practice in making conversions between gates of various logic types.

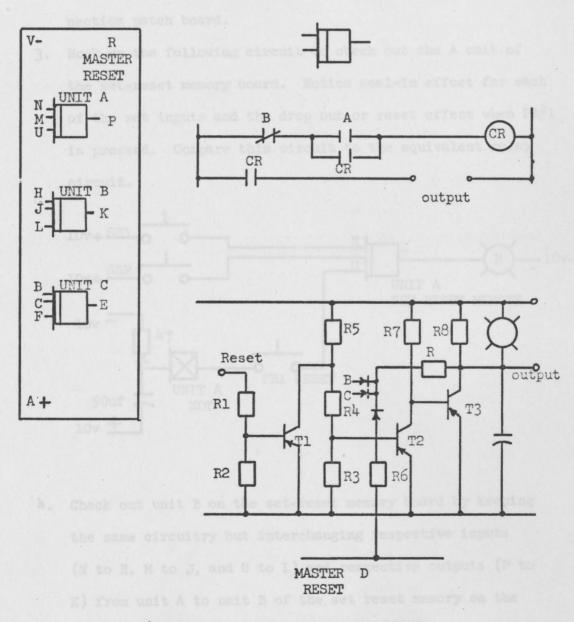

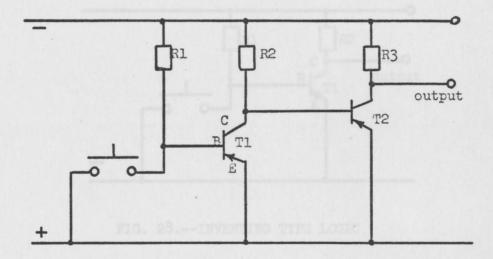

Consider the circuit in Figure 27 that illustrates the noninverting type logic. Transistor T2 will re-invert the output signal from the first transistor (T1) thereby restoring similarity with the input signal. Since the output signal looks like the input signal the circuit is called non-inverting logic.

FIG. 27 .-- NON-INVERTING LOGIC CIRCUIT

With the push button open transistor Tl is forward biased and base current flows from the + bus through Tl (E to B) and through Rl to the - bus. Tl while conducting acts like a closed switch (E to C). With Tl conducting the base of T2 is at the same potential as the emitter and T2 will not conduct. T2 acts like an open switch (E to C) and there will be no output signal across R3. When the push button is closed Tl does not conduct and acts like an open circuit (E to C) since its base and emitter are at the same potential. This places a negative voltage on the base of T2 through R2, forward biasing T2 causing it to conduct. T2 will draw base current and act like a short circuit (closed switch E to C) and 10 volts will appear across output load resistor R3.

Thus with the non-inverting circuit with no input (PB open) there is no output (O volts across R3). When there is an input (PB closed) there is an output (10 volts across R3). Figure 28 illustrates the inverting type logic.

FIG. 28.--INVERTING TYPE LOGIC

With the push button open Tl is forward biased and base current flows from the + bus through Tl (E to B) and through Rl to the negative bus. When Tl conducts it acts like a short circuit (closed switch) E to C and 10 volts appears across output resistor R2.

With the push button closed Tl cannot conduct since the base and emitter are at the same potential. Tl acts like an open switch E to C and no voltage appears across output resistor R2.

Thus with the inverting circuit with no input (PB open) there is an output (10 volts across R2). With an input (PB closed) there is no output (0 volts across R2).

Is should be noted that small circles encountered in the outputs or inputs of inverting logic symbols signify inverters. This can be noticed in the MAND and the NGR gates in Figure 25. We can say that the WAND is an AND with an invertor in its output. We can also say

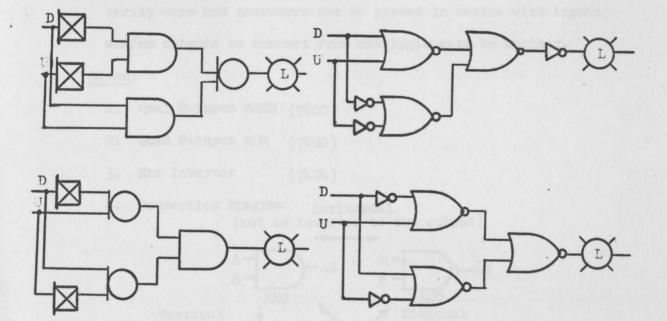

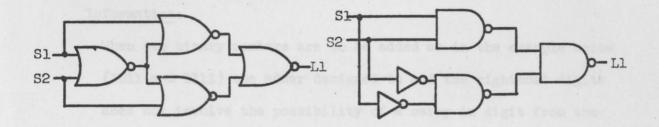

#### Conversions Between Conventional and Inverting Logic

Since the major suppliers of electrical equipment might utilize either or both types of logic systems, it becomes important to be able to convert circuitry from one system to another. Also, since required logic gates might have to be constructed from other available logic gates, it becomes important to be able to convert from one gate to another.

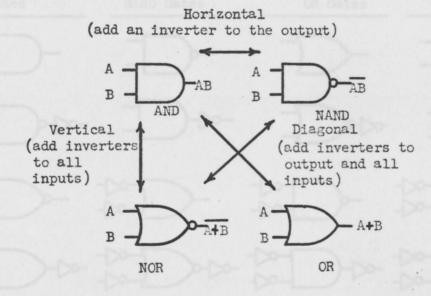

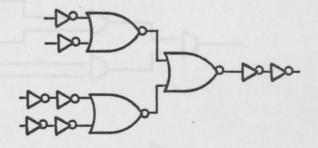

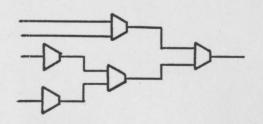

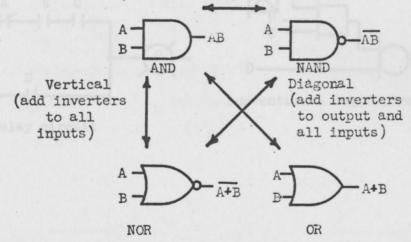

Figure 29 presents a simplified method for converting from one logic gate to another by adding inverters to inputs and/or output.

FIG. 29 .-- GATE CONVERSION METHOD 2

It should be noted that small circles encountered in the outputs or inputs of inverting logic symbols signify inverters. This can be noticed in the NAND and the NOR gates in Figure 29. We can say that the NAND is an AND with an inverter in its output. We can also say

<sup>&</sup>lt;sup>2</sup>Technical Staff, <u>Practical Applications of Digital Integrated</u> Circuits (Northfield, Ohio: General Electronics Associates, Inc., 1972),

that the NOR is an OR with an inverter in its output. The symbol

->>- also represents an inverter. Placing inverters in series with the input leads of an OR make it act like a NAND, and placing inverters in series with the input leads of an AND makes it act like a NOR gate. Two inverters in series cancel each other and may be eliminated.

To better understand the given conversion method verify each entry in Table 6.

#### TABLE 6

#### GATE CONVERSIONS

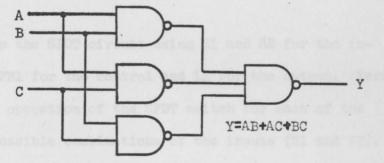

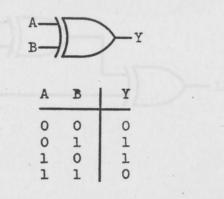

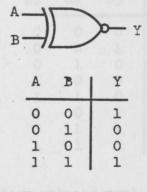

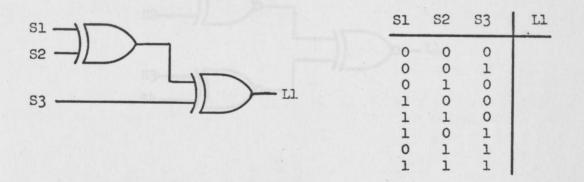

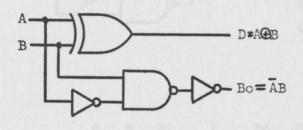

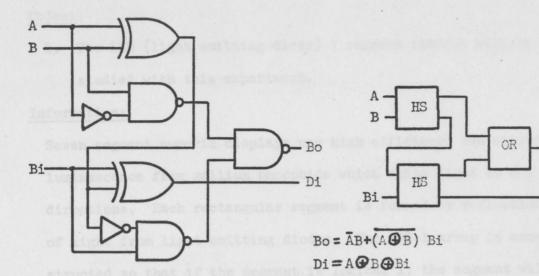

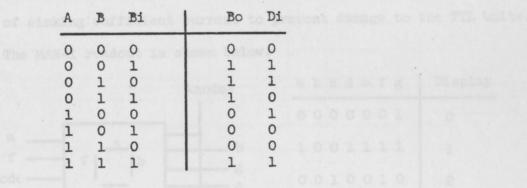

The final aim of this chapter is to present the exclusive OR and utilize it to compare conventional (non-inverting) circuitry and inverting circuitry. More will be said about the exclusive OR in the next chapter. The exclusive OR will produce a 1 if only one of its inputs (an odd number) is 1 but not if both inputs (an even number) are 1. Consider this function in Table 7 which is a truth table summary for the gates we have studied.

# TABLE 7

| GATE | TRUTH | TABLE | SUMMARY |  |

|------|-------|-------|---------|--|

|      |       |       |         |  |

| Inputs<br>A I | 5 | AND              | OR               | NAND             | NOR              | Exclusive OR     |

|---------------|---|------------------|------------------|------------------|------------------|------------------|

| 0 ]           |   | 0<br>0<br>0<br>1 | 0<br>1<br>1<br>1 | 1<br>1<br>1<br>0 | 1<br>0<br>0<br>0 | 0<br>1<br>1<br>0 |

|               |   |                  |                  |                  |                  |                  |

|               |   |                  |                  |                  |                  |                  |

|               |   |                  |                  |                  |                  |                  |

|               |   |                  |                  | 1.3-             |                  |                  |

|               |   |                  |                  |                  |                  | 0 1 1            |

|               |   |                  |                  |                  |                  |                  |

|               |   |                  |                  |                  |                  | 0                |

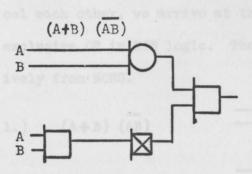

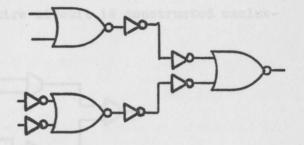

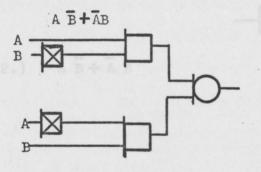

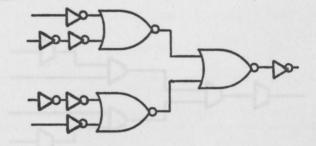

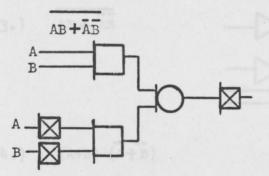

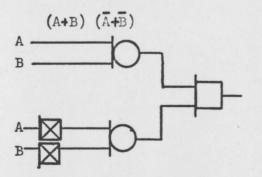

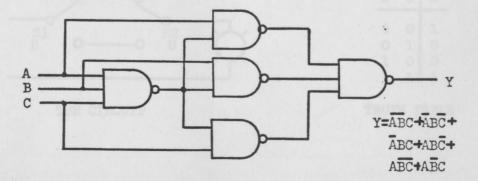

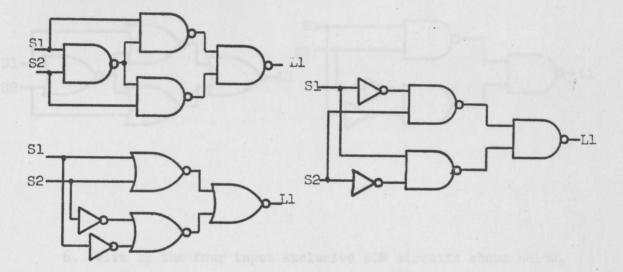

The conventional logic diagrams have been drawn in Table 9 for each of these equivalent exclusive OR forms, as well as an equivalent inverting logic diagram using only ROR elements and invertors. Four ways that the exclusive OR can be represented algebraically as seen by the equivalence of the column with the asterisk (\*) are  $(A+B)(\overline{AB})$ ,  $\overline{AB}+\overline{AB}$ ,  $\overline{AB}+\overline{AB}$ , and  $(A+B)(\overline{A}+\overline{B})$ .

## TABLE 8

EXCLUSIVE OR TRUTH TABLES

| A B                      | A+B              | AB               | AB               | (A+B)(AB) *             |

|--------------------------|------------------|------------------|------------------|-------------------------|

| 0 0<br>0 1<br>1 0<br>1 1 | 0<br>1<br>1<br>1 | 0<br>0<br>0<br>1 | 1<br>1<br>1<br>0 | 0<br>1<br>1<br>0        |

|                          | 1 - 1            |                  |                  |                         |

| A B                      | AB               | ĀB               |                  | AB+ AB *                |

| 0 0<br>0 1<br>1 0<br>1 1 | 0<br>0<br>1<br>0 | 0<br>1<br>0<br>0 | A<br>A           | 0<br>1<br>1<br>0        |

| A B                      | AB               | ĀB               | AB + A           | B AB + AB               |

| 0 0<br>0 1<br>1 0<br>1 1 | 0<br>0<br>0<br>1 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1 | 0<br>1<br>1<br>0        |

| A B                      | A+B              | Ā +              | B                | (A+B)(A+B) *            |

| 0 0<br>0 1<br>1 0<br>1 1 | 0<br>1<br>1<br>1 | 1<br>1<br>1<br>0 | 1                | 0 · ·<br>1 · ·<br>0 · · |

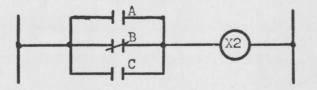

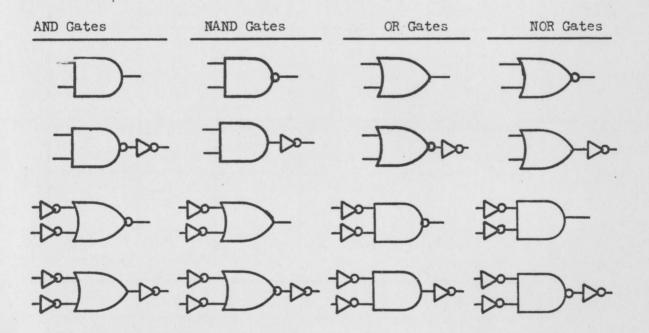

The conventional logic diagrams have been drawn in Table 9 for each of these equivalent exclusive OR forms, as well as an equivalent inverting logic diagram using only NOR elements and inverters.

# TABLE 9

# EXCLUSIVE OR DIAGRAMS

Conventional logic

NOR logic

In NOR logic as used with Westinghouse (Prodac) that will be covered in Chapter VI, the symbol  $\longrightarrow$  is used to represent a NOR. If the inputs of a NOR are shorted together to make a single input, it acts as an inverter. Also since two inverters in series cancel each other, we arrive at the following simplified diagrams for the exclusive OR in NOR logic. The entire circuit is constructed exclusively from NORS.

1.) (A+B) (AB)

2.) A B + A B

3.) AB + AB

4.)  $(A+B)(\bar{A}+\bar{B})$

#### CHAPTER V

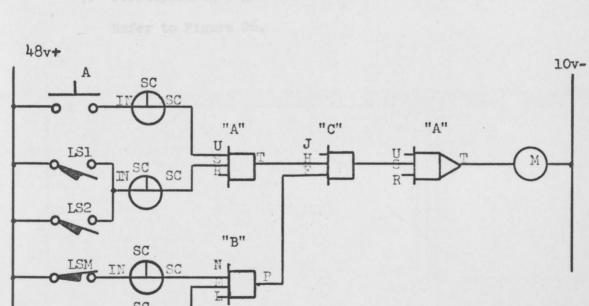

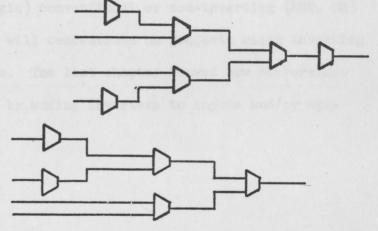

TTL (TEXAS INSTRUMENTS) INVERTING LOGIC TUTOR

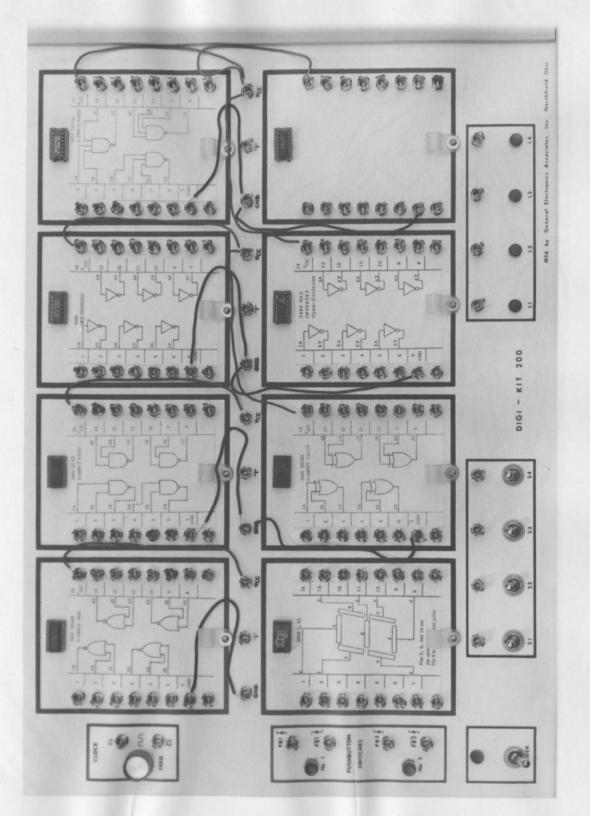

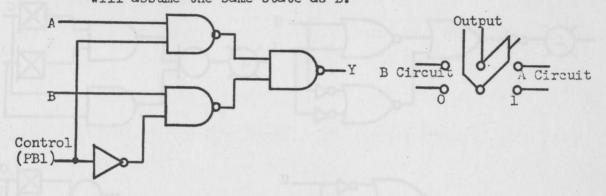

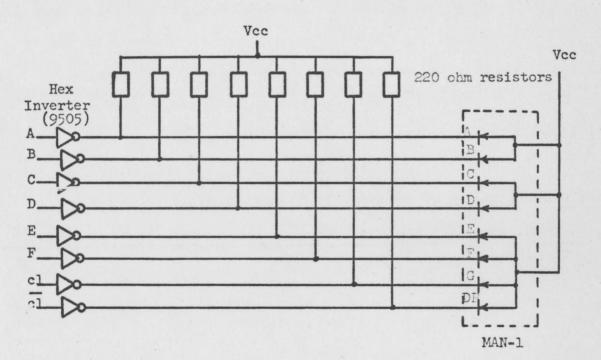

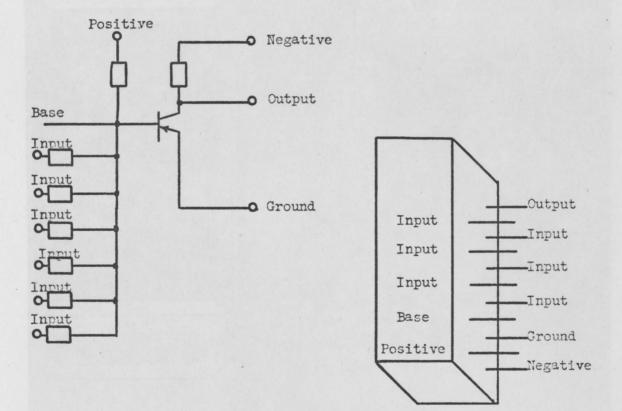

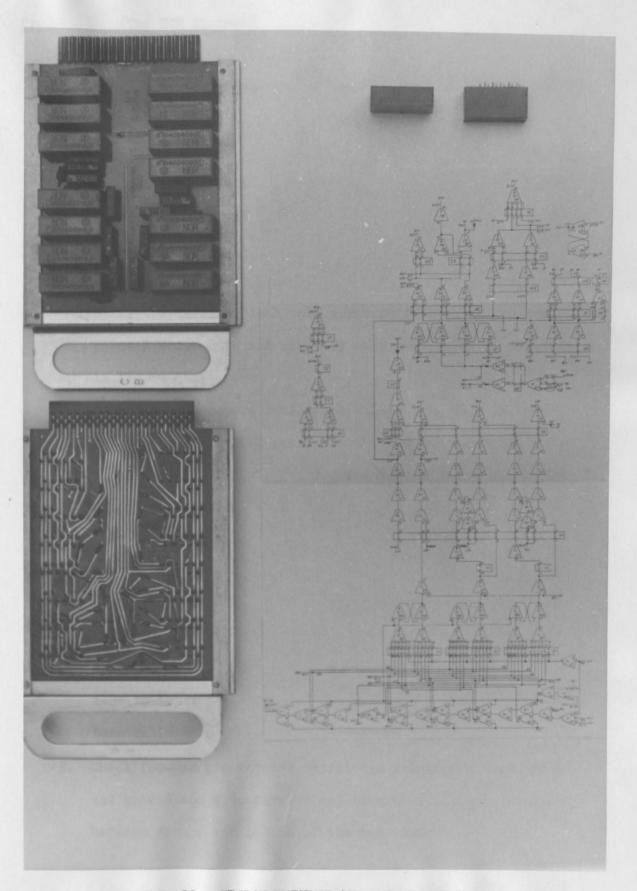

Figure 30 is a photograph of the laboratory equipment to be used in completing the experiments of this chapter. The Digi-Kit Midel 200 was purchased from General Electronics Associates, Inc., Northfield, Ohio, and the projects will utilize the 7400 line of TTL (Transistor to Transistor Logic) integrated circuits manufactured by Texas Instruments, Incorporated.

Chapter III contained a group of experiments using Cutler Hammer DSL (Direct Static Logic) conventional or non-inverting (AND, OR) type logic. This chapter will concentrate on projects using inverting (NAND, NOR) logic hardware. The last chapter showed how conversions can be made between gates by adding inverters to inputs and/or outputs of other gates.

FIG. 30.--TTL DIGI-KIT TUTOR

Pertinent Digi-Kit specifications are summarized below, as are a few precautions and pointers that need to be kept in mind while experimenting with this equipment.

# TABLE 10

#### DIGI-KIT SPECIFICATIONS

| Input Voltage  | -   | 110v  | 60 | Hz |

|----------------|-----|-------|----|----|

| Output Voltage | e - | 5v    |    |    |

| Output Curren  | t - | 1 amp |    |    |

Clock - frequency adjustable from 10 to 200 pulses per second with two complementary outputs CL and CL.

Push buttons - PBl and PB2 are prewired with electronic circuits to provide one pulse for each depression. Each switch has two complementary outputs.

Toggle Switches - four prewired toggle switches, supply TTL logical 1 and logical 0 outputs for gating functions.

Indicating lights - four lights with appropriate driving circuits are available for testing, and monitoring output points.

Terminals - four sets of ground (G ND), "1", and Vcc are available on the board. The logical "1" terminals are convenient for driving or stabilizing TTL devices without damage since this voltage is limited to a safe value.

Precautions to be observed while working with TTL integrated circuits in the coming projects.

Care must be taken when inserting and removing the integrated circuit packages. If the leads are bent the IC sockets can be damaged. When inserting an IC into its socket, make sure all leads are aligned properly and then apply firm pressure. ICs should not be pulled out with your fingers. Use an extractor or a small screwdriver and be careful.

- 2. A small etched marking on top of the IC or small notch at one end indicates the location of pin #1. If the IC is held with the notch to the left and the pin tips pointing downward, #1 pin will be toward you to the left. Pin #1 goes into the socket corner that is rounded off. In our case the notched IC end goes to the far left of the socket.

- 3. There are paper overlay cards that are placed directly below the IC and between terminals. These cards identify the various inputs and outputs of the IC.

- 4. The IC cards are provided with 5v power by connecting ground terminal of the IC to the ground bus and Vcc terminal of the IC to Vcc bus. These must be connected for each IC package. Position these power feed leads so that they will stay in place and do not need to be disconnected in going from one experiment to the next.

- 5. If at all in doubt about the circuitry, have an instructor check it out before applying power. Be sure to turn power off when making or breaking connections.

goes out. The outputs of each push button has complimentary outputs. Outputs FEL and FE2 will deliver a positive going pulse when their respective buttons are depressed, and conversely outputs FEL and FEE will deliver a negative going pulse when their respective buttons are copressed. Renoval

Experiment 1 (The Basic Logic Gates)

### Object:

This experiment is to familiarize you with the tutor that will be used in the coming experiments and to review the basic logic gates.

### Given:

- 1. Digi-Kit 200 and jumper leads.

- 2. Quad 2 input NOR (7402) and associated overlay

- 3. Quad 2 input NAND (7400) and associated overlay

- 4. Hex Inverter (7404) and associated overlay

- 5. Table of 5 basic gates

#### Procedure:

- Jumper from Sl toggle switch to Ll, from S2 to L2, from S3 to L3 and from S4 to L4. As each of the respective toggle switches is closed, observe lights. Remove jumpers.

- Jumper from each of the four "1" terminals to the four indicating lights and verify "1" terminal outputs. Remove jumpers.

- 3. Jumper from PB1, FE1, FE2, and FM2 to L1, L2, L3, and L4 respectively. Notice that the two indicating lights supplied from FB1 and FE2 are on similating normally closed contacts on the pushbuttons. Depress FB1 and note that L1 goes on as L2 goes off. Depress FB2 and note that L3 goes on and L4 goes out. The outputs of each push button has compliment-ary outputs. Outputs FB1 and FE2 will deliver a positive going pulse when their respective buttons are depressed, and conversely outputs FB1 and FE2 will deliver a negative going pulse when their respective buttons are depressed. Remove

jumpers.

- 4. Jumper from clock terminal CL to L1 and from clock terminal CL to I2. Adjust frequency for lowest value and note complimentary. The clock serves as a pulse generator to provide a series of pulses for driving counters, shift registers, and other sequential circuits. Note the effect as the frequency is increased. Remove jumpers.

- 5. Wire up and verify the operation of each of the five basic gates given in Table No.11, and complete the truth tables for the output (L1) of each of these five basic gates.

# TABLE 11

BASIC GATES WITH TTL

| Gate     | IC No.       | Circuit    | Truth Tables                                                             |

|----------|--------------|------------|--------------------------------------------------------------------------|

| Inverter | 7404         | 51 — Do 11 | SI LI<br>O<br>I                                                          |

| NOR      | 7402         |            | S1     S2     L1       0     0       0     1       1     0       1     1 |

| NAND     | 7400         |            | <u>S1 S2 L1</u><br>0 0                                                   |

| AND      | 7400<br>7404 |            | Ll S1 S2 L1                                                              |

| OR       | 7402<br>7404 | s1         | L1 0 0 1<br>1 0<br>1 1<br>S1 S2 L1                                       |

|          |              |            |                                                                          |

1

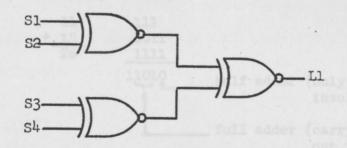

Experiment 2 (Interconnecting Logic Gates)

Object:

Practice interconnecting various integrated circuits will be accomplished in this experiment by wiring up three special circuits and verifying their operation.

Given:

Quad 2 input NAND