# MICRO-CONTROLLER AND DIGITAL SIGNAL PROCESSING

An investigation into digital signal processing,

with emphasis on simplicity and practically.

by

Seyed Akhavi

Submitted in Partial Fulfillment of the Requirements

for the degree of Master of Science in Engineering

in the

**Electrical Engineering**

Program

92 41 Advisor Date

101301

Sally M. Hotchkiss

Dean of the Graduate School

# YOUNGSTOWN STATE UNIVERSITY

June, 1992

Date

1992

15

# ABSTRACT

# MICRO-CONTROLLER AND DIGITAL SIGNAL PROCESSING SEYED AKHAVI

# MASTER OF SCIENCE IN ENGINEERING YOUNGSTOWN STATE UNIVERSITY, 1992

New advances in digital electronics have made it possible to manufacture microcontrollers which are capable of analyzing and processing signals. Now applications that require bulky components and complex hardware can be implemented by using microcontrollers. The auto industry is using these single chips to monitor and control the speed of the motor, fuel injection rate and spark timing. Precision electronic instruments, peripheral devices, communication devices such as pagers, laser printers, color copiers, are all equipped with one or more microcontroller chips. A modern approach, which takes full advantage of the microcontroller 's programmability, has made it feasible to simulate such tasks as filtering in the digital domain. This thesis investigates the design and implementation of a 5-band audio signal analyzer by using the latest 16-bit microcontroller manufactured by Motorola. Methods and techniques involved in the areas of analog-to-digital conversion, digital signal processing, serial interfacing, and related programming routines are discussed and developed. Hardware as well as software design goals, with the emphasis on programmability of microcontrollers, are presented.

1-10-4

# ACKNOWLEDGMENTS

I wish to acknowledge the assistance of my advisor Professor Skarote for teaching the courses which gave birth to the ideas of this project. His teachings have always been an inspiration for me to try and pursue new ideas.

I also wish to thank Microcontroller Unit of Motorola for their assistance in obtaining literature, samples, and information. And finally, I must acknowledge my deep debt to my wife, Mansureh, without whose support, patience, and tolerance I would not have brought this project to conclusion.

# TABLE OF CONTENTS

| ABSTRACT                               | ii  |

|----------------------------------------|-----|

| ACKNOWLEDGMENTS                        | iii |

| TABLE OF CONTENTS                      | iv  |

| LIST OF SYMBOLS                        | vi  |

| LIST OF FIGURES                        | ix  |

| CHAPTER I                              | 1   |

| INTRODUCTION                           | 1   |

| OVERVIEW                               | 1   |

| SELECTION OF DESIGN CRITERIA           | 4   |

| DESIGN SPECIFICATIONS                  |     |

| Conditioning The Incoming Signal       |     |

| System Clock And Timing                | 5   |

| ANALOG TO DIGITAL CONVERSION           | 8   |

| HARDWARE                               | 9   |

| Microcontroller                        | 9   |

| Audio Frequency Analyzer               | 10  |

| SOFTWARE                               | 11  |

| CHAPTER II                             |     |

| ADC CONVERSION                         | 12  |

| SUCCESSIVE-APPROXIMATION ADC CONVERTER | 12  |

| Overview                               | 12  |

| HARDWARE                               | 12  |

| Analog Subsystem                       | 14  |

| Digital Control Subsystem              | 14  |

| Bus Interface Subsystem                | 14  |

| SOFTWARE                                            | 15 |

|-----------------------------------------------------|----|

| Successive Approximation Register (SAR):            | 15 |

| Result Registers                                    | 15 |

| Module Configuration Register (ADCMCR):             | 16 |

| ADC Control Register 0 (ADCTL0):                    | 16 |

| ADC Control Register 1 (ADCTL1):                    | 17 |

| ADC Status Register (ADSTAT):                       | 18 |

| Conversion Complete Field (CCF):                    | 18 |

| Conversion Counter Field (CCTR):                    | 18 |

| Sequence Complete Flag (SCF):                       | 19 |

| ADC PROGRAM                                         | 19 |

| CHAPTER III                                         | 21 |

| DIGITAL SIGNAL PROCESSING                           | 21 |

| INFINITE IMPULSE-RESPONSE (IIR) FILTER              | 21 |

| THE DIFFERENCE EQUATION                             | 24 |

| RESPONSE OF THE DIGITAL FILTER                      | 25 |

| ANALYSIS CONSTRAINTS OF THE BILINEAR TRANSFORMATION | 30 |

| COEFFICIENT QUANTIZATION                            | 30 |

| SIGNAL PEAK DETECTOR                                | 33 |

| CHAPTER IV                                          | 36 |

| CONCLUSIONS                                         | 36 |

| AREAS FOR FURTHER DEVELOPMENT                       | 37 |

| APPENDIX A                                          | 38 |

| CALCULATION OF THE COEFFICIENTS                     | 38 |

| APPENDIX B                                          | 41 |

| COMPLETE LIST OF THE PROGRAM                        | 41 |

| BIBLIOGRAPHY                                        | 63 |

# LIST OF SYMBOLS

# SYMBOL DEFINITION

# UNITS OR REFERENCE

| Analog-to-digital conversion             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A bus interface unit                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADC module configure register            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADC control register 0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADC control register 1                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADC status Register                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Audio frequency analyzer                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Arithmetic logic unit                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Binary digit 0 or 1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Group of bits, usually eight             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Capacitance                              | farad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Channel selection field                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conversion complete field                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conversion counter field                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Central processing unit                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Digital to analog conversion             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Digital signal processing                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Decibel, unit of logarithmic power ratio | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Center frequency                         | cycles/second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Sampled frequency                        | cycles/second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Freeze                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| General purpose timer                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                          | A bus interface unit<br>ADC module configure register<br>ADC control register 0<br>ADC control register 1<br>ADC status Register<br>Audio frequency analyzer<br>Arithmetic logic unit<br>Binary digit 0 or 1<br>Group of bits, usually eight<br>Capacitance<br>Channel selection field<br>Conversion complete field<br>Conversion counter field<br>Conversion counter field<br>Digital to analog conversion<br>Digital signal processing<br>Decibel, unit of logarithmic power ratio<br>Center frequency<br>Sampled frequency<br>Freeze |

| HCMOS | High-density complementary metal   |       |

|-------|------------------------------------|-------|

|       | oxide semiconductor                |       |

| I/O   | Input/output                       |       |

| IIR   | Infinite impulse response          |       |

| IMB   | Intermodule bus                    |       |

| kbyte | kilo- (one thousand byte)          |       |

| kHz   | kilo- (one thousand hertz)         |       |

| L     | Inductance                         | henry |

| LED   | Light emitting diode               |       |

| Mag   | Magnitude                          | dB    |

| MCU   | Microcontroller unit               |       |

| MULT  | Multichannel conversion bit        |       |

| MSB   | Most significant bit               |       |

| PIT   | Programmable interrupt timer       |       |

| PRS   | Prescalar rate selection           |       |

| Q     | Quality factor                     | none  |

| QSM   | Queued serial module               |       |

| QSPI  | Queued serial peripheral interface |       |

| R     | Resistance                         | ohm   |

| RAM   | Random access memory               |       |

| RC    | Resistor-capacitor                 |       |

| Ref.  | Reference                          |       |

| Res.  | Resolution                         |       |

| rms   | Root mean square                   |       |

| ROM   | Read only memory                   |       |

| S8CM     | Select eight-conversion sequence mode     |        |

|----------|-------------------------------------------|--------|

| SAA      | Small angle approximation                 |        |

| SAR      | Successive approximation register         |        |

| SCAN     | Scan mode selection bit                   |        |

| SCF      | Sequence complete flag                    |        |

| SCI      | Serial communication interface            |        |

| SIM      | System integration module                 |        |

| SRAM     | Standby RAM                               |        |

| STS      | Sample time select field                  |        |

| SUPV     | Supervisor/unrestricted                   |        |

| Tc       | Clock period                              | second |

| Ts       | Sampled period                            | second |

| VLSI     | Very large scale integration              |        |

| $Z^{-1}$ | Inverse z-transform operator              |        |

| $\phi$   | Phase angle                               | radian |

| θ        | Sampled period                            | radian |

| α        | Coefficient related to analog domain in z |        |

| 0        | ~ ~ ~                                     |        |

Coefficient related to analog domain in z γ

$A(\omega)$ Gain

β

Coefficient related to analog domain in z

# LIST OF FIGURES

| FIGURE                                                     | PAGE |

|------------------------------------------------------------|------|

| 1. Audio Frequency Analyzer System Diagram                 | 3    |

| 2. Transfer Function Without Low Pass Anti-Aliasing Filter | 5    |

| 3. AFA Software Flow Diagram                               | 7    |

| 4. AFA Sampling Period                                     | 8    |

| 5. Analog-to-Digital Converter Block Diagram               | 13   |

| 6. ADCMCR Configuration                                    | 16   |

| 7. ADCTL0 Configuration                                    | 17   |

| 8. ADCTL1 Configuration                                    | 18   |

| 9. SCF Configuration                                       | 19   |

| 10. Op-Amp Active Bandpass Filter                          | 22   |

| 11. DSP Memory Configuration                               | 32   |

| 12. Relationship Between Signal Amplitude and The LED Bar  | 35   |

# CHAPTER I

#### INTRODUCTION

# **OVERVIEW**

Semiconductor manufacturers have produced 16- and 32- bit microprocessors which can handle larger sizes of data at a faster rate. These microprocessors not only are used in fast computers and workstations but also they have been employed in realtime control applications. The microprocessor, and several other chips which handle timing, interrupts, serial communications, and parallel communications might be needed in design of a real-time control. In a real time-control the microprocessor interacts with resources which make up an instrument or device, at times dictated by the hardware external to the microprocessor. Many applications require fast response and service by a microprocessor. One approach that semiconductor manufacturers have chosen to increase the system speed is to build faster microprocessors. Another technique has combined the microprocessor with RAM, ROM, and variety of input/output capabilities on a single chip, which is commonly referred to as a microcontroller.

This technique has been made possible by recent advances in very large scale integration (VLSI) chip manufacturing. Now it is conceivable to build a single chip that contains all of the major elements of a computer system. This single chip, which is a microcontroller unit (MCU), includes the central processing unit (CPU), comprised of the arithmetic logic unit (ALU) and control unit, plus interfacing devices and memory units. The MCU is a single chip which is built up from standard modules that interface via a common internal bus[1]. The study of a 16-bit microcontroller and its application in digital signal processing (DSP) is the main scope of this thesis. The advantages of the digital domain over the analog domain have initiated a new trend where traditional electronic circuits are now being emulated in software and hardware. One such area is in digital signal processing. This new method offers a primary advantage over analog and has much greater flexibility. The programmability of DSP is what makes it flexible. If a designer is using analog components such as resistors and capacitors in a low pass filter, and later on might want to make changes to the filter specifications, one must go back and replace the wiring as well as the components. Once DSP is applied to make any changes, the designer need only substitute some of the codes in the software and in this way alter the behavior of the filter. Fast microcontrollers have made it possible to generate and process frequencies up to 40 kHz.

The designed project uses a microcontroller to:

- Convert the audio signal into a digital signal.

- Sample and subject the data signal to five DSP band pass filter algorithms.

- Extract the peak of each filter.

- Encode the peaks of each band and send them through queued serial peripheral interface (QSPI) to the LED array in real time.

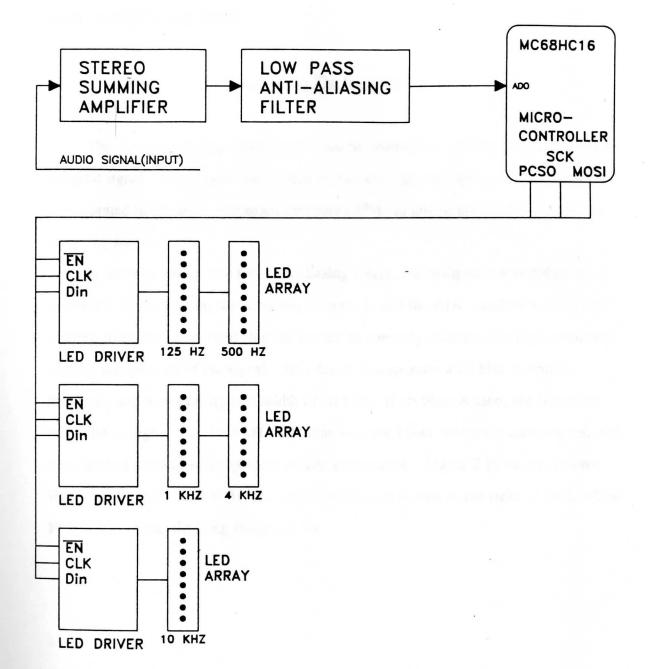

Figure 1 in the next page shows the block diagram of the project.

Figure 1. Audio Frequency Analyzer System Diagram

# SELECTION OF DESIGN CRITERIA

# **DESIGN SPECIFICATIONS**

# Conditioning The Incoming Signal

The incoming analog audio signal must be conditioned before being converted to a digital signal. A low pass filter which eliminates high and unwanted frequencies is incorporated in the audio frequency analyzer (AFA) to utilize the conditioning of the incoming signal.

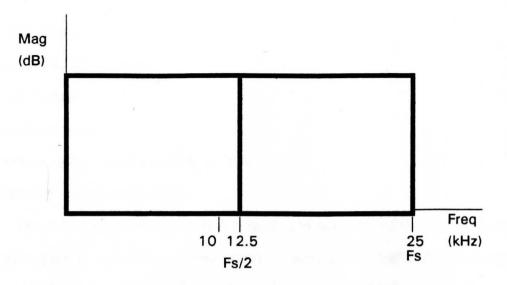

In order to design low pass anti-aliasing filters, the designer has to define the bandwidth of the system, the sampling frequency, and the ADC resolution. The antialiasing filter is an important element needed to correctly attenuate the high frequency aliasing components of the signal. This design incorporates a 25 kHz sampling frequency and a processing bandwidth of 10 kHz. If no filter is used, the frequency components higher than 12.5 kHz will alias with the lower frequency components, and the digitized samples will represent invalid information. Figure 2 shows the desired signal left of Fs/2, 12.5 MHz, and undesired aliased signals to the right of Fs/2, where Fs/2 is half of the sampling frequency Fs.

Figure 2. Transfer Function Without Low Pass Anti-Aliasing Filter

# System Clock And Timing

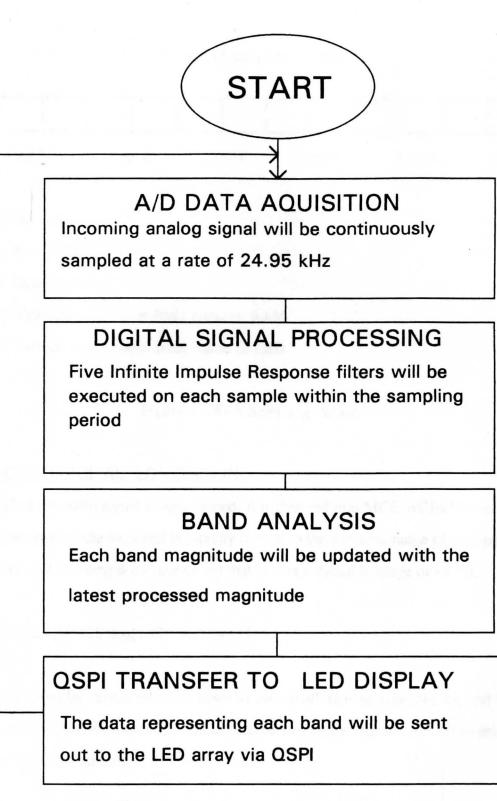

The software flow diagram of the AFA is shown in Figure 3. This flowchart contains the steps listed earlier to complete the program. The flowchart shows that the AFA will run in a continuous loop. The main objective is to extract digital data from the ADC, run five infinite impulse response (IIR) bandpass filter routines, detect the peak amplitude of each filter, encode the peak value to an LED value, and update the QSPI transmit registers, which outputs the information to the LED array.

The MC68HC16Z1 runs on a 16.78 MHz which has a system clock period of 60 nsecs. The processing of the signal should take no longer than 40080 nsecs which is about 668 clock cycles. This is shown below:

Fs=Sampling frequency

Ts=Sampling period

Fc=MC68HC16Z1 CPU clock frequency

Tc=MC68HC16Z1 CPU clock period

Fs = 224.9 kHz

Ts=1/Fs=40.08 microsec

Fc=16.78 MHz

Tc = 1/Fc = 60nsec

System clock cycles per sampling period=Ts/Tc

# Ts/Tc = 668 system clock cycles

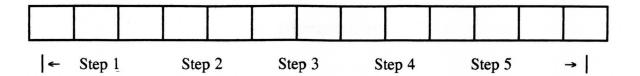

The sampling period is shown in Figure 2, which shows the relationship between sampling periods and real time digital signal processing. In DSP, all calculations and internal/external communications must be taken care of within the given sample period. Figure 4 relates the software flowchart in Figure 3 to the designated sample period.

Figure 3. AFA Software Flow Diagram

WILLIAM F. MAAG LIBRARY YOUNGSTOWN STATE UNIVERSITY

# Stream of sampling periods

- Step 1: Get ADC value

- Step 2: Run 5 IIR DSP routine

- Step 3: Detect peak of each filter

Step 4: Write peak values to QSPI transmit RAM

Step 5: Turn on QSPI output peak values to LED

# Figure 4. AFA Sampling Period

# ANALOG TO DIGITAL CONVERSION

After the audio signal is conditioned, it is then fed into MC68HC16Z1's ADC. The attenuation of the stopband is directly related to the dynamic range of the sampled data. We will be using 8-bit conversion that allows a dynamic range of 48 dB.

Attenuation (dB) =  $20 \times \log[1/(2 \times ADCres.)]$

The signal must be attenuated 48dB down to cut out all aliasing components, and have a drop-off slope of 96dB/octave. 100 dB/octave was chosen for the roll-off to insure meeting the specifications.

# Microcontroller

The MC68HC16Z1 is a high speed 16-bit control unit designed and manufactured by Motorola. MC68HC16Z1 is a member of the M68300/68HC16 Family of modular microcontrollers. This microcontroller incorporates a true 16-bit CPU, a system integration module (SIM), an 8/10-bit analog to digital converter (ADC), a queued serial module (QSM), a general-purpose timer (GPT), and a 1024-byte standby RAM (SRAM). All these modules are interconnected by the intermodule bus (IMB). Although all these capabilities might be present in other microcontrollers, for the first time Motorola designers have included instructions and hardware necessary to implement control-oriented digital signal processing functions with a minimum of interfacing, in the MC68HC16Z1. A multiply and accumulate unit provides the capability to multiply signed 16-bit fractional numbers and store the resulting 32-bit fixed point product in a 36-bit accumulator. Modulo addressing supports finite impulse response filters; this feature was the main reason for selecting the MC68HC16Z1 for this design. The DSP techniques and all of the complex mathematical routines involved in DSP boil down to multiplication and addition. There are four internal registers, which facilitates DSP mathematical routines [2].

This microcontroller has an embedded module for ADC conversion. The ADC is a unipolar, successive-approximation converter with eight modes of operation. It has selectable 8 or 10-bit resolution.

The queued serial module (QSM) provides the MC68HC16Z1 with two serial communication interfaces divided into two submodules: the queued serial peripheral interface (QSPI) and the serial communications interface (SCI). The QSPI is a full-

duplex, synchronous serial interface for communicating with peripherals and other MCUs. It is enhanced by the addition of a queue for receiving and transmitting data.

The general-purpose timer (GPT), a module in MC68HC16Z1 is a 11-channel timer for use in systems where a moderate level of CPU control is required. The GPT is made up of different submodules: the compare/capture unit, the pulse accumulator, and the pulse-width modulation unit.

The standby RAM (SRAM) is a 1kbyte array of fast (two bus cycle) static RAM, which is especially useful for system stacks and variable storage.

The system clock for the MC68HC16Z1 is 16.78 MHz, and high-density complementary metal-oxide semiconductor (HCMOS) architecture makes the basic power consumption of MC68HC16Z1 low.

# Audio Frequency Analyzer

Spectral analysis is a method of determining the specific frequency content of a signal and the energy levels of these frequencies. The energy level, in this case the peak voltage, is processed by either Fourier Transform methods or by specific filtering of the signal. The result is then tabulated for more analysis or displayed in a visual format. This AFA is built by implementing digital signal processing filter techniques.

The input consists of two stereo audio signals that are added together with an opamp summing circuit. The output is then sent to the anti-aliasing filter to remove unwanted high frequency components. The biasing circuit is used to adjust the signal to alter between  $\pm 2.5$  volts for proper analog-to-digital conversion. The digital signal processing takes place in the MC68HC16Z1. MAX 274 manufactured by Maxim is used as a low frequency filter. MAX 274 is an 8th order, programmable, continuoustime active filter. There are four 2nd-order filter sections in MAX 274. MAX 274 uses a four-amplifier design which is insensitive to parasitic capacitances and high bandwidth. The built-in capacitors and amplifiers, together with external resistors, form cascaded integrators with feedback to provide simultaneous lowpass and bandpass filtered outputs.

MC14489 is selected to drive 16 LEDs and three of them are cascaded to drive a total of 40 LEDs. MC14489 receives the signal on its serial input from QSPI of the MC68HC16Z1.

#### SOFTWARE

A program has to be developed in order for Audio Frequency Analyzer to work properly. The main program is divided into 4 sections; each of these sections will perform a distinct operation. The first program is initializing the ADC submodule of MC68HC16Z1 and digitizes the analog input. The second program initializes the QSPI and defines the serial communication between the MC68HC16Z1 and MC14489. The third program activates the PIT and synchronizes the system operation with the incoming stream of data. The fourth and final program subjects the digitized data to five DSP routines to detect the peak of the samples at 125 Hz, 500 Hz, 1 kHz, 4 kHz, and 10 kHz (See Appendix B).

# CHAPTER II

# ADC CONVERSION

# SUCCESSIVE-APPROXIMATION ADC CONVERTER

# Overview

The successive-approximation method of converting an analog signal to a digital signal is used when the analog voltage changes rapidly and where the speed of conversion is a factor. In this method the counter is first reset, then the MSB is set to a 1. The DAC converter generates a voltage caused by the MSB, and this is compared to the input analog voltage. If the DAC voltage is greater than the input voltage, the MSB is reset. Then the second MSB is set to a 1, and the comparisons are made again. This process is repeated for each bit until the proper combination of bits is present.

The MC68HC16Z1 uses the successive-approximation method to convert the incoming audio signal.

#### HARDWARE<sup>1</sup>

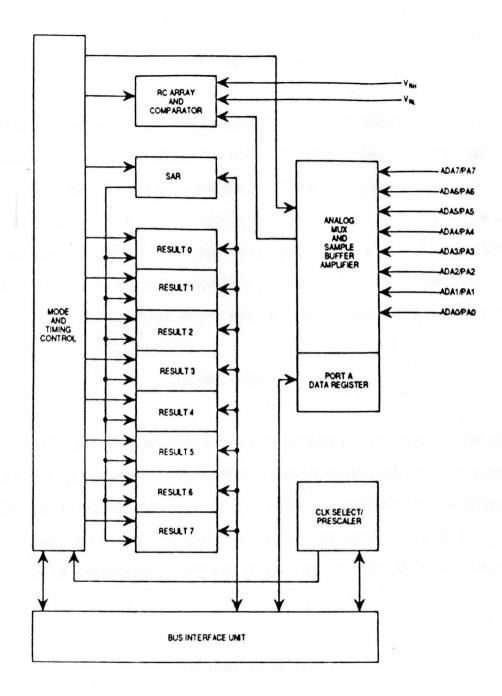

The ADC submodule is capable of performing 8-bit single conversion in 8 microseconds, and a 10-bit single conversion in 9 microseconds. The ADC functions are divided into three basic subsystems: an analog front end, a digital control section, and a bus interface. A block diagram of the converter is shown in Figure 5.

<sup>&</sup>lt;sup>1</sup>For more detailed description of the ADC hardware see "The Technical Summary 16-Bit Modular Microcontroller".

<sup>&</sup>lt;sup>2</sup>This diagram shows the unconventional method of ADC which utilizes software for operation.

#### Analog Subsystem

The analog front end of the ADC submodule of this microcontroller (MC68HC16Z1) includes a multiplexer, a resistor-capacitor array, and a high-gain comparator. The multiplexer selects one of eight internal or eight external signal sources for conversion. The resistor-capacitor (RC) array performs two functions, it acts as a sampled/hold circuit, and it accommodates the digital-to-analog comparison output necessary for successive approximation conversion. The comparator indicates whether each successive output of the RC array is higher or lower than the unit input.

# Digital Control Subsystem

The digital control part includes conversion sequence control logic, channel and reference select logic, successive approximation register, eight result registers, a port data register, and a control/status register. It controls the multiplexer and the output of the RC array during the sample and conversion periods, stores the results of comparison in the successive-approximation register, then transfers the result to a result register.

#### **Bus Interface Subsystem**

The bus interface contains the logic circuitry which is necessary to interface the ADC to the intermodule bus. The ADC acts as a slave device on the bus. The interface must respond with the appropriate bus cycle termination signals and supply appropriate interface timing to the other submodules.

## SOFTWARE<sup>3</sup>

Four registers must be configured for ADC operation. These registers are the Module Configuration Register, Control Register 0, Control Register 1, and Status Register. In addition to these four registers there are two general-purpose registers which are used for any type of ADC conversion. These two registers are discussed first in the following sections.

# Successive Approximation Register (SAR):

The successive approximation register accumulates the result of each conversion one bit at the time, starting with the most significant bit. At the start of the resolution period, the MSB of the SAR is set, and all less significant bits are cleared. Depending on the result of the first comparison, the MSB is set or cleared. Each successive bit is set or left cleared in descending order until all eight or ten have been resolved. When conversion is complete, the content of the SAR is transferred to the appropriate result register.

# **Result Registers**

Result registers are used to store data after the conversion is complete. The registers can be accessed from the IMB under ABIU control. Each register can be read from three different addresses in the ADC memory map. The format of the result data

<sup>&</sup>lt;sup>3</sup>There are more than one hundred memory mapped hardware registers that need to be configured for this project. I have chosen the ADC converter as an example to show how these registers and their related fields are selected and configured.

depends on the address from which it is read. Three types of formats can be specified, unsigned right-justified format {\$FFF710:\$FFF71E}, signed left-justified format {\$FFF720:\$FFF72E}, and unsigned left-justified format {\$FFF730:\$FFF73E}.

# Module Configuration Register (ADCMCR):

The module configuration register contains five fields. This register selects the normal mode of operation for ADC and initializes the ADC operation. Bit 15 is set to 0 for normal operation. Bits 13 and 14 are cleared and bit 7 is also cleared to have unrestricted access to ADC submodule. The fields associated with this register are shown below:

| 15   | 14  | 13 | 12       | 8      | 7    | 6 |          | 0 |

|------|-----|----|----------|--------|------|---|----------|---|

| STOP | FRZ |    | NOT USED | a foid | SUPV |   | NOT USED |   |

| 0    | 0   | 0  |          |        | 0    |   |          |   |

Figure 6. ADCMCR Configuration

# ADC Control Register 0 (ADCTL0):

This register is used to define ADC clock source and to set up prescaling. Storing data in this register has an immediate effect. There are three fields that need to be defined. The Prescalar Rate Selection field is defined to select a divisor value which corresponds to minimum and maximum system clock. ADC clock is generated from system clock using a modulo counter and a divide-by-two circuit. The way the ADC clock is selected is based on the value in the PRS region of ADCTL0. The system clock is divided by the PRS value plus one, then sent to the divide-by-two circuit. Bits 0 and 1 are set to select 16 MHz frequency for the ADC and the rest of the bits are cleared. The fields associated with this register are shown below:

| 15 |          | 8      | 7     | 6 | 5  | 4 |     | 0 |

|----|----------|--------|-------|---|----|---|-----|---|

|    | NOT USED | in i b | RES10 | S | TS |   | PRS |   |

# Figure 7. ADCTL0 Configuration

# ADC Control Register 1 (ADCTL1):

ADCTL1 is used to start analog to digital conversion. It has four functions. The first one is to select a channel or a block of inputs for ADC conversion. Bits 0 thru 3 {CD:CA} are used to specify which input line or block of data is to be converted to digital. The audio signal in this project is applied to the input line ADO, so the binary value 0000 is picked for this region. The second function of this register is to select the kind of conversion. A single or a continuous conversion can be chosen. If the SCAN bit is set, a continuous conversion takes place and if this bit is cleared, a single conversion is done. The third selection is accomplished by setting or clearing the multichannel conversion bit (MULT). The fourth field in this register is a bit which, if it is zero, four-conversion sequence takes place and if it is one, sequential conversion of a block of four or eight channels (selected by channel selection field) is performed. The fields associated with this register are shown below:

| 15       | 7 | 6    | 5    | 4    | 3  | 2  | 1  | 0  |

|----------|---|------|------|------|----|----|----|----|

| NOT USED |   | SCAN | MULT | S8CM | CD | cc | CB | CA |

Figure 8. ADCTL1 Configuration

# ADC Status Register (ADSTAT):

The last register that must be configured for proper operation of Analog Digital Converter submodule is its status register. This register is used to signal the CPU when the conversion is done. It has three active fields which will be discussed in detail here.

# Conversion Complete Field (CCF):

Each bit {0:7} in this field corresponds to an ADC result register (CCF7 to RSLT7, etc.). A bit is set when conversion for the corresponding channel is complete, and remains set until the result register is read. It is cleared when the register is read.

# Conversion Counter Field (CCTR):

This region shows the contents of the conversion counter pointer in either four or eight count conversion sequence. The value corresponds to the number of the next result register to be written, and thus indicates which channel is being converted.

#### Sequence Complete Flag (SCF):

SCF is set at the end of the conversion sequence when SCAN is cleared, and at the end of the first conversion sequence when SCAN is set. SCF is cleared when ADCTL1 is written and a new conversion sequence begins. The fields associated with this register are shown below:

| 15  | 14 11    | 10 8 | 7   | 0 |

|-----|----------|------|-----|---|

| SCF | NOT USED | CCTR | CCF |   |

| 0   |          |      |     |   |

# Figure 9. SCF Configuration

# ADC PROGRAM

The program which initializes and begins converting analog input to digital signal is shown below. First, the ADMCR register is configured for normal operation. In some applications the analog input lines could be used as an I/O port. In this project the AD0 thru AD7 are selected as analog input lines. Second, in ADCTL0 register, bit 7 is set to zero for 8-bit conversion, and PRS field is filled with 00011 for a 16 MHz prescaled rate for clock generation. Third, ADCTL1 is filled with 0000 to ensure the single conversion sequence will run on a single channel (AD0). Fourth, ADSTAT is configured so that the result register 7 will hold the digital equivalent of the incoming analog signal. The complete list is shown on the next page.

| ****   | ADC Initialization ***** |         |  |  |  |

|--------|--------------------------|---------|--|--|--|

|        | LDD                      | #\$0000 |  |  |  |

|        | STD                      | ADCMCR  |  |  |  |

|        | LDD                      | #\$0003 |  |  |  |

|        | STD                      | ADCTL0  |  |  |  |

| ****   | ADC Start                | ****    |  |  |  |

| LOOP   | LDD                      | #\$0000 |  |  |  |

|        | STD                      | ADCTL1  |  |  |  |

|        | LDAA                     | #\$80   |  |  |  |

| SCFSET | BITA                     | ADSTAT  |  |  |  |

|        | BEQ                      | SCFSET  |  |  |  |

|        | BRA                      | LOOP    |  |  |  |

#### CHAPTER III

# DIGITAL SIGNAL PROCESSING

### **INFINITE IMPULSE-RESPONSE (IIR) FILTER**

The theory of the infinite impulse response (IIR) algorithm used to perform the bandpass filtering is examined and developed briefly. The equations presented here are developed to aid in the calculation of the coefficients necessary for digital signal processing (DSP). This algorithm is used to design five digital filters with different bandpass and cutoff frequencies. The following questions need to be answered. If the characteristics of a filter are defined in analog domain, how are those characteristics employed in digital domain? What is the connection between the analog passive filter and the digital IIR filter?

To outline the characteristics of the digital filter, the equivalent analog passive RCL bandpass network is considered. By applying the voltage divider rule, the transfer function can be written as follows:[3]

$$\frac{v_0}{v_i} = \frac{R}{R + j(\omega L - 1/\omega C)} \tag{1}$$

where  $\omega = 2\pi f$ . The gain is the magnitude of Equation (1),

$$A(\omega) = \frac{1}{\sqrt{\left[1 + Q^2 \left(\frac{\omega^2 - \omega_0^2}{\omega \omega_0}\right)^2\right]}}$$

(2)

where  $\omega_0 = \frac{1}{\sqrt{LC}}$  and  $Q = \frac{\omega_0 L}{R}$ . The phase angle,  $\phi$ , is found by taking the ratio of

the imaginary to real parts of the transfer function of Equation (1):

$$\phi = \tan^{-1} \left[ Q \frac{(\omega^2 - \omega_0^2)}{(\omega \omega_0)} \right]$$

(3)

The equivalent s-plane expression is calculated by substituting  $s = j\omega$ :

$$H(s) = \frac{Rs}{Rs + Ls^2 + 1/C}$$

(4)

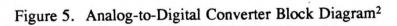

An op-amp active-filter circuit with essentially the same response as the passive RCL network is shown in Figure 10. This active filter has several advantages over the passive network: it eliminates the inductor; it is essentially isolated from input and output loading and can provide signal gain to the system.[4]

Figure 10. Op-Amp Active Bandpass Filter

A digital-transfer function representation of Equation (4) may be obtained by applying the bilinear transformation: [5,6]

$$s = \frac{2}{T} \frac{(1 - z^{-1})}{(1 + z^{-1})}$$

(5)

where  $z = e^{\beta}$ ,  $\theta = \omega T$ , and T is the sample period. Equation (5) can also be expressed as follows:

$$\omega = \frac{2}{T} \tag{6}$$

using the definition of s and z. Substituting Equation (5) into Equation (4) yields the zplane transfer function:

$$H(z) = \frac{\alpha(1-z^{-2})}{1/2 - \gamma z^{-1} + \beta z^{-2}}$$

(7)

where the coefficients,  $\alpha$ ,  $\beta$ , and  $\gamma$ , are related to R, C, and L by

$$\alpha = \frac{RT/2}{T^2/2C + RT + 2L}$$

(8)

$$\gamma = \frac{2L - T^2 / 2C}{T^2 / 2C + RT + 2L}$$

(9)

$$\beta = \frac{T^2 / 4C - RT / 2 + L}{T^2 / 2C + RT + 2L}$$

(10)

The nonlinear relation between the analog domain frequency and the digital domain frequency is often referred to as the frequency warp.[5] As the frequency starts from zero, both analog domain frequency and digital domain frequency are approximately equal, since  $\tan\theta \approx \theta$  for small angles. However, as analog domain frequency approaches infinity, digital domain frequency approaches  $2\pi F_S/2$ . In this particular application, most of the interesting and useful frequencies satisfy the small angle approximation (SAA) where  $\theta < \pi/4$ . Thus, using the SAA simplifies the digital analysis, and a direct correspondence to the analog RCL network is established. Although the SAA indeed simplifies the analysis, it must be used very carefully in the derivation because the nature of this IIR filter depends on very small differences of numbers. If not used correctly, the SAA can mask these differences and give totally erroneous results.

#### THE DIFFERENCE EQUATION

To implement the transfer function from Equation (7) as an IIR filter, it is necessary to transform it to a difference equation in the discrete time domain. In this form, the filter can be directly implemented in software. Applying the inverse ztransform operator,  $Z^{-1}$ , to Equation (7) yields the following:[7]

$$Z^{-1}\{H(z)\} = Z^{-1}\{Y(z) / X(z)\}$$

$$Z^{-1}\{Y(z)[1 / 2 - \gamma z^{-1} + \beta z^{-2}]\} = Z^{-1}\{X(z)[\alpha(1 - z^{-2})]\}$$

(12)

The time delay property of the z-transform can be stated as follows:

$$X(z)z^{-m} = Z\{[x(n-m)]\}$$

(13)

where n is the discrete time index variable associated with continuous time sampling at a rate T. Evaluating Equation (6b), using the property of Equation (7), gives the final IIR difference equation:

$$y(n) = 2\{\alpha[x(n) - x(n-2)] + \gamma y(n-1) - \beta y(n-2)\}$$

(14)

The coefficients,  $\alpha$ ,  $\beta$ , and  $\gamma$ , in the difference equation (Equation (14)) are used to adjust the filter response (gain and phase as a function of frequency). The representation of the time-varying data is based on standard notation used in digital filter theory.[5,6,7] Thus, x(n) is the current sampled data represented as an N-bit signed fraction; x(n-1) is the previous data word; and x(n-2) is the data word previous to x(n-1). The time index is n and it is assumed that the sampled period, T, is constant and is related to the sample frequency,  $f_s$ , by  $T=1/f_s$ . For example, the time between x(n) and x(n-2) is 2T. Sampled values of the input signal are only collected at integral multiples of T (i.e., the x(n)'s are standard sampled/digitized data).

The y(n) is similar to the input data, x(n), and represents the output data from the difference equation algorithm. As before, y(n) is the current output value; y(n-1) is the previous value; and y(n-2) is the value previous to y(n-1). Even though it is assumed that the input data is a signed fraction (a number between one and minus one), the y(n)'s can be greater than one (or less than minus one) unless scaling is performed to prevent this overflow condition.

The coefficients,  $\alpha$ ,  $\beta$ , and  $\gamma$ , in the difference equation (Equation (14)) are also fractional values (i.e. between one and minus one). As it will later be shown, scaling at the output can be controlled by imposing the following condition on two of these these coefficients:

$$\alpha = 1/4 - \beta/2 \tag{15}$$

This formula guarantees that, at the center frequency, the gain is one and the phase difference is zero. In this case, the bandpass filter acts as an attenuation filter and a phase shifter for all frequencies other than the center frequency. Limiting the gain to one and the input to a fraction scaled to a maximum of one does not always prevent overflow at the output .

### **RESPONSE OF THE DIGITAL FILTER**

The gain and phase response can be calculated solely from Equation (7). The advantage of complex numbers is that both gain and phase information are present in the transfer function. By definition, the gain is the absolute magnitude of H(z). In the RLC circuit, the gain is simply the ratio of the resistance to the magnitude of the total

complex impedance. The ratio of the real to imaginary components of the impedance is equal to the tangent of the phase. Likewise, the ratio of real to imaginary components of H(z) is equal to the tangent of the phase for the digital case.

Euler's identity is implemented to ease the calculation of gain,  $G(\omega)$ , and phase,  $\theta(\omega)$ :

$$e^{j\theta} = \cos\theta + j\sin\theta \tag{16}$$

The transfer function (Equation (7)) then becomes:

$$H(e^{j\theta}) = \frac{\alpha(e^{j2\theta} - 1)}{0.5e^{j2\theta} - \gamma e^{j\theta} + \beta}$$

(17)

and

$$H(e^{j\theta}) = \frac{\alpha(\cos 2\theta - 1) + j\sin 2\theta}{(0.5\cos 2\theta - \gamma\cos\theta + \beta) + j(0.5\sin 2\theta - \gamma\sin\theta)}$$

(18)

where  $\theta = \omega T$ . For example,  $\theta = \pi / 2$  would correspond to  $f = f_s / 4$  (since  $\omega = 2\pi f$  and  $T = 1/f_s$ ). If  $f_s = 44.1$  kHz, then  $\theta = \pi / 2$  would be a frequency of 11.025 kHz. The filter gain is found by evaluating the following expression:

$$G(\omega) = \sqrt{H(e^{j\theta})H^*(e^{j\theta})}$$

(19)

and, after some algebraic and trigonometric manipulations, becomes:

$$G(\omega) = \frac{2\alpha \sin\theta}{\{[(1/2 - \beta)\sin\theta]^2 + [(1/2 + \beta)(\cos\theta - \cos\theta_0)]^2\}^{1/2}}$$

(20)

where

$$\cos\theta_0 = \gamma(1/2 + \beta) \tag{21}$$

is the filter center frequency.

Examination of the gain in Equation (13) shows several important features:

- The gain,  $G(\omega)$ , is proportional to  $\alpha$ .

- The gain at the center frequency,  $\omega_0$ , is

$$G_0 = 2 \alpha / (1/2 - \beta)$$

(22)

as previously noted in Equation (9).

- The bandwidth is adjusted by  $\beta$  (that also affects the center frequency as shown by Equation (21)).

- Equation (20) is symmetric (neglecting the zero at  $\theta = \pi$ ) on a logarithmic scale. This characteristic of the gain can be seen more easily by taking the SAA of Equation (20) where

$$\sin\theta \approx \theta \tag{23}$$

$$\cos\theta \approx 1 - \theta^2/2 \tag{24}$$

so that

$$G_{a}(\omega) = \frac{G_{o}}{\sqrt{1 + (\frac{0.5 + \beta}{0.5 - \beta})^{2} (\frac{\theta_{o}^{2} - \theta^{2}}{2\theta})^{2}}}$$

(25)

Substitution of  $\theta = k\theta_0$  or  $\theta = \theta_0/k$  yields equivalent values of gain, thus proving that the gain is symmetrical over the log of frequency. The subscript "a" denotes that the SAA was used in that expression.

The phase shift,  $\varphi(\omega)$ , is found from the ratio of the imaginary to real part of H(z) from Equation (17):

$$\tan\phi = \frac{\mathrm{Im}[\mathrm{H}(\mathrm{e}^{j\theta})]}{\mathrm{Re}[\mathrm{H}(\mathrm{e}^{j\theta})]}$$

(26)

After some algebraic and trigonometric manipulations, Equation (26) can be written as

$$\tan\phi = \frac{(0.5 + \beta)(\cos\theta - \cos\theta_0)}{(0.5 - \beta)\sin\theta}$$

(27)

Applying the SAA simplifies the previous result:

$$\tan \phi_{a} = \frac{(0.5 + \beta)(\theta_{0}^{2} - \theta^{2})}{(0.5 - \beta)2\theta}$$

(28)

The SAA can be used to approximate the filter center frequency,  $\theta_0$ , from Equation (21):

$$\theta_{0_{\mathbf{a}}} = \sqrt{\frac{1+2\beta-2\gamma}{0.5+\beta}} \tag{29}$$

The SAA is accurate within a few percent for angles up to  $\pi/4$ . (This SAA corresponds to a filter frequency of  $f < f_s/8$ .)

The bandwidth of the filter is most easily determined from Equation (25). Generally, two frequencies are considered, one on each side of the center frequency,  $\theta_0$ . The gain at each of the frequencies,  $\theta_1$  and  $\theta_2$ , is equivalent and is commonly chosen so that the value of gain is  $G_0/\sqrt{2} = -3$  dB of the center frequency gain. As previously noted,  $\theta_1 = \theta_0/k$  and  $\theta_2 = k\theta_0$  for a filter symmetric about the center frequency over the log of frequency.

The Q of the filter in such a case is as follows:

$$Q = \frac{\theta_0}{\Delta \theta} = \frac{\theta_0}{k\theta_0 - \theta_0 / k} = \frac{k}{k^2 - 1}$$

(30)

where k > 1. Since, by definition, the bandwidth is determined at the frequencies corresponding to a gain of  $G_0/\sqrt{2}$ , using Equation (25), the following term is equal to one:

$$[(0.5 + \beta_{a}) / (0.5 + \beta_{a})]^{2} [(\theta_{1}^{2} - \theta_{1}^{2}) / 2\theta_{1}]^{2} = 1$$

(31)

and using Equation (30) to solve for  $\beta_a$  in terms of Q yields

$$\frac{0.5 + \beta_{a}}{0.5 - \beta_{a}} = \frac{2}{\theta_{0}} \bullet \frac{k}{k^{2} - 1} = \frac{2Q}{\theta_{0}}$$

(32)

Rearranging terms results in the final form:

$$\beta_{a} = \frac{Q - \theta_{0} / 2}{2Q + \theta_{0}}$$

(33)

where  $\theta_0 = 2\pi f_0/f_s$ . The subscript "a" is used to denote that the SAA was used in this derivation (i.e., by definition of Q from Equation (25)).

Solving for  $\gamma$  in Equation (21) gives

$$\gamma = (0.5 + \beta)\cos\theta_0 \tag{34}$$

For unity gain at the center frequency,  $\alpha$  (Equation (22)) becomes

$$\alpha = (0.5 - \beta) / 2 \tag{35}$$

Equation (25) now simplifies to the following equation for gain:

$$G_{a}(\omega) = \frac{1}{\sqrt{1 + Q^{2} [(\theta_{0}^{2} - \theta^{2}) / (\theta_{0} \theta)]^{2}}}$$

(36)

Equation (28) becomes

$$\phi_{\mathbf{a}}(\omega) = \tan^{-1} \{ \mathbf{Q}[(\theta_0^2 - \theta^2) / (\theta_0 \theta)] \}$$

(37)

Equations (20), (21), (22), and (27) provide a complete, theoretically accurate, and concise description of the digital filter response described by the difference equation (Equation (14)). The coefficients,  $\alpha$  and  $\gamma$ , can be found from  $\beta$ ,  $\theta_0$ , and  $G_0$ .  $\beta$  must be determined from the gain (Equation (20)) by picking  $G(\theta_1)$  and  $\theta_1$ , then finding the values of  $\beta$  from the equality. These four equations are exact and can be used over the entire frequency range from 0 to  $\pi$ .

Equations (33) through (37) provide a simplified set of formulas that are reasonably accurate for  $f < f_s/8$  and for unity gain at the center frequency.

## ANALYSIS CONSTRAINTS OF THE BILINEAR TRANSFORMATION

The passive series resonant network shows how to determine the IIR coefficients from the RCL values of a passive network filter based on the bilinear transformation. This technique is very powerful, especially if the frequencies of interest are much lower than the sample frequency (as is often the case in digital audio applications) so that the SAA can be used. The resonant and cutoff frequency and quality factor, Q, of most RCL networks are known or can be easily determined. The difference equation shows how to convert the transfer function to another difference equation, which is the final form (for software implementation) of the digital IIR filter. The relationship connecting the R, L, and C values of the analog filter to the coefficients  $\alpha$ ,  $\beta$ , and  $\gamma$  of the digital filter (from Equations 8 thru 10) holds true only for frequencies where the SAA is valid. This frequency range makes up the linear region of the bilinear transformation where (from Equation (6))  $\tan \theta \approx \theta$ . In this case, a direct correspondence between the response of almost any RCL network and an IIR filter's coefficients can be established, as previously demonstrated for the bandpass filter network. This technique lends itself to audio applications because the response of a network is usually described as a function of the log of frequency. The audio range is basically logarithmic, thus the SAA applies to most of the range of interest since  $f_e/8$  is very close to  $f_s/2$  on a log scale.

### COEFFICIENT QUANTIZATION

Coefficient quantization depends solely on the word length of the filter coefficients. Equations (20), (21), and (22) yield values for  $\alpha$ ,  $\beta$ , and  $\gamma$  for given values of center frequency and bandwidth. These formulas are exact. However, the

word size of the variables used to represent the coefficients in the filter algorithm are of finite length. Therefore, only certain discrete values of center frequency, bandwidth, and resonant frequency gain are obtainable.

To analyze the effects of coefficient quantization in this particular digital filter, let N be the number of bits used to represent data in the algorithm. Assuming that the coefficients are fractions, the smallest number that can be represented is therefore:  $\delta = 2^{-(N-1)}$  (38)

Using Equation (38),  $\alpha$ ,  $\beta$ , and  $\gamma$  can be represented as follows:

$$\gamma = 1 - n\delta \tag{39}$$

$$\beta = 1/2 - m\delta \tag{40}$$

since  $\beta < 1/2$  and  $|\gamma K|$ . This can be easily seen by evaluating the zeros of the transfer function (Equation 7) and then calculating the magnitude of that complex number. The resulting value is the distance from the origin to the pole in the complex plane and is equal to  $2\beta$ . Now, since the poles must lie within the unit circle  $\beta < 1/2$ .[7] Using Equation (19), it can be seen that  $|\gamma| < 1$ . The integers n and m take on values from 1 to  $2^{N-1}$ . Equation (29) can be written as

$$\theta_{0} = \sqrt{\frac{1 + 2(1/2 - m\delta) - 2(1 - n\delta)}{1/2 + (1/2 - m\delta)}} = \sqrt{\frac{2(n - m)\delta}{1 - m\delta}}$$

(41)

By inspection, the lowest nonzero value of  $\theta_0$  is with n=2 and m=1. The lowest obtainable frequency is then

$$f_{0} = \theta_{0} f_{s} / 2\pi = \frac{1}{2\pi} \sqrt{2(\frac{\delta}{1-\delta})} = f_{s} 2^{-N/2/\pi}$$

(42)

Assuming  $f_s = 44.1$  kHz. The lowest obtainable frequency for 16 bits is 54.8 Hz; for 24 bits, it is 3.4 Hz. Clearly, 16 bits does not yield the coefficient accuracy needed to implement filter responses in the low-frequency bands (i.e., 20 to 200 Hz) for audio applications.

The sampling frequency in this design is 24.95 kHz, and the center frequency and Q for all five bandpass filters are:

|               | F <sub>0</sub> | Fs        | Q   |

|---------------|----------------|-----------|-----|

| FIRST FILTER  | 125 Hz         | 24.95 kHz | 0.5 |

| SECOND FILTER | 500 Hz         | 24.95 kHz | 1.0 |

| THIRD FILTER  | 1 kHz          | 24.95 kHz | 1.5 |

| FOURTH FILTER | 4 kHz•         | 24.95 kHz | 1   |

| FIFTH FILTER  | 10 kHz         | 24.95 kHz | 0.5 |

Using above values and Equations (34), (35), and (36) the coefficients can be calculated (See appendix A). After the coefficients are calculated, these fractions are converted to 16-bit hexadecimal values. Two's complement arithmetic is utilized to the calculation, therefore the most significant bit is the sign bit. The fraction is contained in the remaining bits, 0-14. A total of fifteen bits will represent the numbers from 0 to 32,767. The fraction first is multiplied by 32,767, and then is converted to its hexadecimal equivalent. If this number is negative, the two's complement is taken to find the final answer.

A series of multiplications and additions are performed to implement these values with the 68HC16. The following figure shows the memory configuration used to carry out the mathematics. As an example, the 1 kHz filter's coefficients are used.

| XN1_1K | x(n-1) | YN1_1K | y(n-1)      | GAM_1K | γ  |

|--------|--------|--------|-------------|--------|----|

| XN2_1K | x(n-2) | YN2_1K | y(n-2)      | BET_1K | -β |

|        |        | X_2_1K | x(n)-x(n-2) | ALP_1K | α  |

Figure 11. DSP Memory Configuration

32

The ADC value x(n) is divided by two at the start of the algorithm. This is to ensure that no overflow will occur with the binary mathematics. Next, x(n-2) is subtracted from x(n). This value is stored away to location  $X_2_1K$ . Three MAC (multiply and accumulate) instructions starting at this address are executed. Then y(n-1) is multiplied by  $\gamma$  and is added to the accumulator. The equation that defines  $\beta$ above gives its positive value; this value is converted to its negative before storing it in memory. The next step is to multiply y(n-2) by  $-\beta$  and add it to M accumulator and multiply [x(n)-x(n-2)] by  $\alpha$ . This too is added to the accumulator. The last operation is the multiplication of the accumulator by two. This is done by a left shift instruction. This gives the y(n) value. Now the x and y terms need to be updated before the next sample is received. In other words, x(n-1) becomes x(n-2) and x(n) becomes x(n-1). Also, y(n-1) becomes y(n-2) and y(n) becomes y(n-1). Once the DSP is finished on the input x(n) sample, the peak detect algorithm is executed.

# SIGNAL PEAK DETECTOR

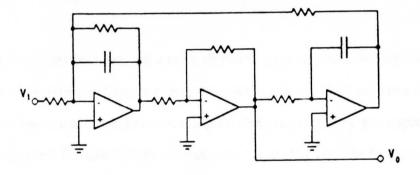

The audio signal is digitally sampled at 24.95 kHz. The amplitude will be detected from the sampled signal and encoded with a value that represents its peak value according to a bar of eight LEDs. Using a reference value of 0.775 Vrms equivalent to 0dB, the signal is measured and displayed from -15dB to +6dB. Figure 13 illustrates the relationship between the LED bar, decibels, Vrms, and Vpeak. This process begins by initializing the internal RAM, the ADC, QSPI, and the PIT; the code jumps to internal Ram at location \$F0000. This is necessary because the access time of the internal RAM is faster than the external RAM access time found on the evaluation board. This speed is for the DSP routine. The program then cycles in an infinite loop reading the ADC, encoding the ADC value to its equivalent LED value, and checking to see if the current value is greater than the previous peak value. If so, then the

current peak value is updated and stored away in memory. The code will increase the current peak value, not decrease it. It also updates the LED array every 10.26 msec with the current peak value. This routine uses a programmable interrupt timer (PIT) to detect the changes in incoming signal. The PIT times out every 62.5 msec to decrement the peak value and the LED display. If the input signal is sharply attenuated, the LED bar slowly decrements. After downloading the program, the 68HC16 is ready to analyze the audio signals.

A signal generator, voltmeter, counter, and an oscilloscope show the analyzer works precisely. A known signal sweeps and the results are displayed on the bar of LED's. The LED's are on and off, based on the magnitude of the input signal. The test verifies each filter is working properly and the software is reliable.

$dB=20*log(V_{in}/V_{ref})$  $V_{ref}=0.775 V_{rms}$  $V_{peak}=1.414 * V_{rms}$

Figure 12. Relationship Between Signal Amplitude and The LED Bar

# CHAPTER IV

## CONCLUSIONS

In this thesis an introduction to the basic operation of the MC68HC16 microcontroller was presented. A program for a five band audio analyzer that used this microcontroller was written. An audio signal was converted to digital, and subjected to the five digital filters via software. Then the magnitude of each center frequency was detected and displayed on an array of LED's.

The project demonstrated the feasibility of the software design. A microcontroller could be used to digitally sample a signal within the audio range and to subject it to digital signal processing. The filtering of such a signal was accomplished by means of software. The programmability of the DSP made it much more flexible than analog approaches to the filter design. Instead of using conventional method of filtering which uses components such as resisters, capacitors, and operational amplifiers, the incoming signal was digitally (and by means of software) sampled, filtered, and then the strength of each band was serially transferred and displayed on an array of LEDs. The performance was verified by sweeping a known signal and observing the results on the bar of LEDs. The implementation of DSP was fully accomplished

The project also effectively demonstrates how the correct micro-controller with proper support circuitry can greatly simplify a design. Where a variety of interfacing hardware is integrated into one chip, the estimated cost, space and the speed are greatly improved. This integration of chips into one and the programmability of the microcontroller clearly demonstrate the advantage of modern digital techniques over the analog method. The same microcontroller can be used to filter out other signals by making minor changes to the program without any hardware modification.

## AREAS FOR FURTHER DEVELOPMENT

In some applications it is required to design filters that have center frequencies higher than 10 kHz. In order to accomplish that, a program which takes fewer cycles to be executed must be developed. At the same time the program must maintain the routines that initialize the submodules and run digital signal processing instructions.

# APPENDIX A

# CALCULATION OF THE COEFFICIENTS

|           | FIRST BAND | FRACTIONS      | MULTIPLIED BY 32768 | HEX NUMBER    |

|-----------|------------|----------------|---------------------|---------------|

| FO        | 1.25E+02   | 125.00000      | 4095000             |               |

| FS        | 2.50E + 04 | 24950.00000    | 817561600           |               |

| 0         | 5.00E-01   | 0.50000        | 16384               |               |

| TETA      | 3.15E-02   | 0.03148        | 1031.500081         | `             |

| x .       | 3.15E-02   | 0.03148        | 1031.500081         |               |

| TAN(X/20) | 7 87E-03   | 0.00787        | 257.880344          | in the second |

| BETA      | 4.92E-01   | 0.49219        | 16128.12806         | 3F32          |

| GAMA      | 3.92E-01   | 0.99170        | 32496.02092         | 7F28          |

| ALFA      | 3.90E-03   | <i>3.00390</i> | 127.935972          | 66            |

|           | SECOND BAND | FRACTIONS   | MULTIPLIED BY 32768 | HEX NUMBER |

|-----------|-------------|-------------|---------------------|------------|

| FO        | 5 00E + 02  | 500.00000   | 16384000            |            |

| 5         | 2.50E + 04  | 24950.00000 | 817561600           |            |

| a         | 1.00E + 00  | 1.00000     | 32768               |            |

| TETA      | 1.26E-01    | 0.12592     | 4126.000324         |            |

| x         | 6 30E 02    | 0.06296     | 2063.000162         |            |

| TAN(X/20) | 3.15E-02    | 0.03149     | 1031.840927         |            |

| BETA      | 4 69E-01    | 0.46946     | 15383.33843         | ·3E68      |

| GAMA      | 9.62E-01    | 0.96179     | 31515.83981         | 7E3F       |

| ALFA      | 1.53E-02    | 0.01527     | 500.3307872         | СВ         |

| -         | THIRD BAND | FRACTIONS  | MULTIPLIED BY 32768 | HEX NUMBER |

|-----------|------------|------------|---------------------|------------|

| F0 .      | 1.00E + 03 | 1.00E + 03 | 32768000            |            |

| FS        | 2.50E + 04 | 2.50E + 04 | 817561600           |            |

| 0         | 1.50E+00   | 1.50E+00   | 49152               |            |

| TETA      | 2.52E-01   | 2.52E-01   | 8252.000647         | 4          |

| x         | 8.39E-02   | 8.39E-02   | 2750.666882         |            |

| TAN(X/20) | 6.30E-02   | 6.30E-02   | 2065.730181         |            |

| BETA      | 4.41E-01   | 4.41E-01   | 14438.34771         | 3866       |

| GAMA      | 9.11E-01   | 9.11E-01   | 29850.14251         | 749A       |

| ALFA      | 2.97E-02   | 2.97E-02   | 972.8261473         | зсс        |

#### IF X EXCEEDS 7 86E-01, THEN IT IS EQUAL TO 0.75398

|           | FOURTH BAND | FRACTIONS  | MULTIPLIED BY 32768 | HEX NUMBER |

|-----------|-------------|------------|---------------------|------------|

| FO        | 4.00E + 03  | 4.00E + 03 | 131072000           |            |

| FS        | 2.50E + 04  | 2.50E+04   | 817561600           |            |

| a         | 1.00E+00    | 1.00000    | 32768               |            |

| TETA      | 1.01E+00    | 1.00732    | 33008.00259         |            |

| x         | 5.04E-01    | 0.50366    | 16504.00129         |            |

| TAN(X/2Q) | 2.57E-01    | 0.25729    | 8430.986702         |            |

| BETA      | 2.92E-01    | 0.29169    | 9558.001333         | 2556       |

| GAMA      | 4.23E-01    | 0.42286    | 13856.26328         | 3620       |

| ALFA      | 1.04E-01    | 0.10416    | 3412.999333         | D54        |

| -         | FIFTH BAND | FRACTIONS  | MULTIPLIED BY 32768 | HEX NUMBER             |

|-----------|------------|------------|---------------------|------------------------|

| FO        | 1.00E + 04 | 1.00E + 04 | 327680000           |                        |

| FS        | 2.50E + 04 | 2.50E + 04 | 817561600           |                        |

| a         | 5.00E-01   | 0.50000    | 16384               |                        |

| TETA      | 2.52E + 00 | 2.51831    | 82520.00647         |                        |

| x         | 7.54E-01   | 0.75398    | 24706.41664         |                        |

| TAN(X/2Q) | 1.91E-01   | 0.19076    | 6250.811315         |                        |

| BETA      | 3.38E-01   | 0.33815    | 11080.41145         |                        |

| GAMA      | -6.81E-01  | -0.68055   | -22300.20051        | 2's Complement<br>A8E4 |

| ALFA      | 8.09E-02   | 0.08093    | 2651.794273         | A58                    |

## APPENDIX B

# COMPLETE LIST OF THE PROGRAM

| *Description : | This program executes a band pass DSP filter                     |

|----------------|------------------------------------------------------------------|

| *              | algorithm in real time.                                          |

| *              | The digital data is acquired with the on-chip                    |

| *              | analog to digital converter.                                     |

| *              | The sampling frequency is 25 kHz.                                |

| *              | Executes the function                                            |

| *              | $y(n) = 2\{\alpha[x(n)-x(n-2)] + \gamma y(n-1) - \beta y(n-2)\}$ |

| * M. tok E. du | The output of the 5 filters are analyzed for                     |

| * '            | their peak values and then encoded with a value                  |

| *              | to represent each peak on the LED bar array.                     |

| *              | These values are sent out to the LEDs via the                    |

| *              | QSPI.                                                            |

| *****          | ***************************************                          |

INCLUDE 'EQUATES.ASM'

;table of EQUates for ;common register addresses ;initialize reset vector

INCLUDE 'ORG00000.ASM'

Addresses of coefficients for the IIR Filters and initialization

| COEFB   | EQU | \$0280     | ;base addr of coefficients |

|---------|-----|------------|----------------------------|

| GAM_125 | EQU | COEFBS+\$0 | ;addr of the gamma coef    |

| BET_125 | EQU | COEFBS+\$2 | ;addr of the beta coef     |

| ALP_125 | EQU  | COEFBS+\$4  | ;addr of the alpha coef   |

|---------|------|-------------|---------------------------|

| GAM_500 | EQU  | COEFBS+\$6  | ;addr of the gamma coef   |

| BET_500 | EQU  | COEFBS+\$8  | ;addr of the beta coef    |

| ALP_500 | EQU  | COEFBS+\$A  | ;addr of the alpha coef   |

| GAM_1K  | EQU  | COEFBS+\$C  | ;addr of the gamma coef   |

| BET_1K  | EQU  | COEFBS+\$E  | ;addr of the beta coef    |

| ALP_1K  | EQU  | COEFBS+\$10 | ;addr of the alpha coef   |

| GAM_4K  | EQU  | COEFBS+\$12 | ;addr of the gamma coef   |

| BET_4K  | EQU  | COEFBS+\$14 | ;addr of the beta coef    |

| ALP_4K  | EQU  | COEFBS+\$16 | ;addr of the alpha coef   |

| GAM_10K | EQU  | COEFBS+\$18 | ;addr of the gamma coef   |

| BET_10K | EQU  | COEFBS+\$1A | ;addr of the beta coef    |

| ALP_10K | EQU  | COEFBS+\$1C | ;ddr of the alpha coef    |

|         | ORG  | \$F0280     |                           |

|         | dc.w | \$7F28      | ;125 Hz gamma coef, Q=0.5 |

|         | dc.w | \$3F32      | ;125 Hz beta coef, Q=0.5  |

|         | dc.w | \$66        | ;125 Hz alpha coef, Q=0.5 |

|         | dc.w | \$7E3F      | ;500 Hz gamma coef, Q=1.0 |

|         | dc.w | \$3E68      | ;500 Hz beta coef, Q=1.0  |

|         | dc.w | \$CB        | ;500 Hz alpha coef, Q=1.0 |

|         | dc.w | \$749A      | ;1k Hz gamma coef, Q=1.5  |

|         | dc.w | \$3866      | ;1k Hz beta coef, Q=1.5   |

|         | dc.w | \$3CC       | ;1k Hz alpha coef, Q=1.5  |

|         | dc.w | \$3620      | ;4k Hz gamma coef, Q=1.0  |

|         | dc.w | \$2556      | ;4k Hz beta coef, Q=1.0   |

|         | dc.w | \$D54       | ;4k Hz alpha coef,Q=1.0   |

|         | dc.w | \$A8E4      | ;10k Hz gamma coef, Q=0.5 |

|         |      |             |                           |

| dc.w | \$2B48 | ;10k Hz beta coef, $Q=0.5$ |

|------|--------|----------------------------|

| dc.w | \$A5B  | ;10k Hz alpha coef, Q=0.5  |

\*\*\*\*

Addresses of filter terms for the x(n) terms and initialization

| XTRMBS  | EQU  | \$02A0      | ;base addr of x(n) filter terms |

|---------|------|-------------|---------------------------------|

| XN1_125 | EQU  | XTRMBS+\$0  | ;x(n-1)                         |

| XN2_125 | EQU  | XTRMBS+\$2  | ;x(n-2)                         |

| XN1_500 | EQU  | XTRMBS+\$4  | ;x(n-1)                         |

| XN2_500 | EQU  | XTRMBS+\$6  | ;x(n-2)                         |

| XN1_1K  | EQU  | XTRMBS+\$8  | ;x(n-1)                         |

| XN2_1K  | EQU  | XTRMBS+\$A  | ;x(n-2)                         |

| XN1_4K  | EQU  | XTRMBS+\$C  | ;x(n-1)                         |

| XN2_4K  | EQU  | XTRMBS+\$E  | ;x(n-2)                         |

| XN1_10K | EQU  | XTRMBS+\$10 | ;x(n-1)                         |

| XN2_10K | EQU  | XTRMBS+\$12 | ;x(n-2)                         |

|         | ORG  | \$F02A0     |                                 |

|         | dc.w | \$0000      | ;125 Hz x(n-1)                  |