# Implementation of a Fuzzy Logic Controller via Cyclone II FPGA and Nios II Processor

by

Eric Michael Stauffer

Submitted in Partial Fulfillment of the Requirements

For the Degree of

Master of Science

In the

Electrical and Computer Engineering

Program

YOUNGSTOWN STATE UNIVERSITY

August, 2006

# Implementation of a Fuzzy Logic Controller via Cyclone II FPGA and Nios II Processor

#### Eric Michael Stauffer

I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies of this thesis as needed for scholarly research.

| Signature: | Ein Stauph                                   | 7/26/00           |

|------------|----------------------------------------------|-------------------|

|            | Eric Michael Stauffer, Student               | Date              |

|            |                                              |                   |

|            |                                              |                   |

| À          |                                              |                   |

| Approvals: |                                              |                   |

|            |                                              |                   |

|            |                                              | 7/26/06           |

|            | Dr. Faramarz Mossayebi, Thesis Advisor       | Date              |

|            | Malal.                                       |                   |

|            | CO CO war                                    | 7/26/2006<br>Date |

|            | Dr. Jalal Jalali, Committee Member           | Date              |

|            |                                              |                   |

|            | Cha                                          |                   |

|            | 1 Muno                                       | 26-July-06        |

|            | Dr. Philip Munro, Committee Member           | Date              |

|            | 0 /                                          |                   |

|            | Teller )/ (anu)                              | 1 August, 2006    |

|            | Peter J. Kasvinsky, Dean of Graduate Studies | Date              |

#### Abstract

Fuzzy control is an emerging control technique which allows an engineer to design a control system with only an operator's knowledge of the plant being controlled. FPGAs and soft processor cores allow engineers to rapidly prototype and modify systems such as controllers. The combination of these two emerging technologies is discussed in detail in this work. It is shown that the principals of fuzzy sets and fuzzy logic can be the basis of a control system implemented in FPGA hardware with a soft processor core. An Altera Cyclone II FPGA with a Nios II soft processor core is implemented to provide an empirical example of a fuzzy controlled system. The design process is detailed in a step-by-step fashion and a prototype is assembled and detailed. Experiments proving the validity of fuzzy control as a control scheme are designed and run and the results are provided. The experiments consists of a fuzzy system controlling the temperature of air inside of a confined space.

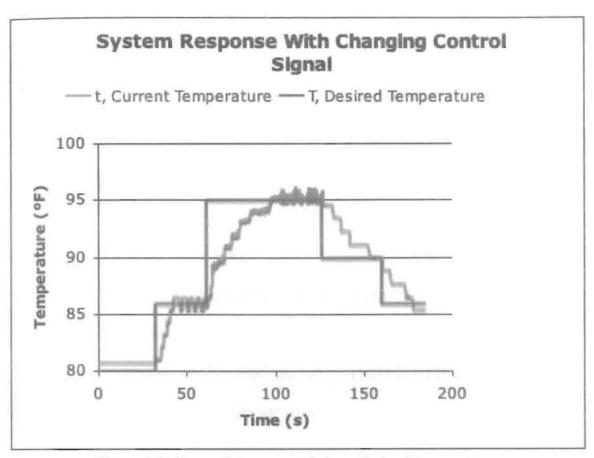

The results prove that fuzzy control is a viable control scheme and that the assertions about limited plant knowledge and ease of design are true. A temperature versus time plot is shown for the ambient temperature inside of a confined space in which a heating and exhaust system is controlled by a fuzzy-based controller.

# **Table of Contents**

| Chapter 11                                  |

|---------------------------------------------|

| 1.1 Motivation and Background1              |

| 1.2 History                                 |

| 1.3 Empirical Experiment                    |

| Chapter 25                                  |

| 2.1 Introduction to Fuzzy Sets              |

| 2.2 Membership Functions                    |

| Chapter 3                                   |

| 3.1 Introduction to Fuzzy Logic             |

| 3.2 Fuzzy Logic Operations                  |

| Chapter 4                                   |

| 4.1 Introduction to Fuzzy Control           |

| 4.2 Preliminary Design                      |

| 4.3 Rule Base Creation                      |

| 4.4 Input Processing                        |

| 4.5 Logic Implementation and Rule Inference |

| 4.6 Output Processing                       |

| Chapter 5                                   |

| 5.1 Motivation and Introduction             |

| 5.2 Controller Design, Step 1               |

| 5.3 Controller Design, Step 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5.4 Controller Design, Step 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 5.5 Controller Design, Step 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 5.6 Controller Design, Step 640                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 5.7 Controller Design, Step 743                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 5.8 Controller Design, Step 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 5.9 Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 5.10 Nios II Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 5.11 Experiment Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 5.12 Conclusions and Future Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Appendices53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Appendix A54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| A.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| A.2 Notation and Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Appendix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| B.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 2 2 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| B.2 Notation and Operations58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| B.2 Notation and Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| AND THE STATE OF T |  |

| Appendix C61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Appendix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| C.5 Relay Functions      | 79 |

|--------------------------|----|

| C.6 Temperature Readings | 81 |

| Appendix D               | 83 |

| D.1 Introduction         | 83 |

| D.2 Quartus II           | 83 |

| D.3 SOPC Builder         | 86 |

| D.4 Nios II IDE          | 87 |

| References               | 88 |

# List of Figures

| Figure 2.1  | Venn Diagram and Single Subset                               |

|-------------|--------------------------------------------------------------|

| Figure 2.2  | Venn Diagram and Two Subsets                                 |

| Figure 2.3  | Venn Diagram Representing A Union B                          |

| Figure 2.4  | Venn Diagram of A Intersection B                             |

| Figure 2.5  | Venn Diagram Representation of Tall/Short Example            |

| Figure 2.6  | Venn Diagram Representing a Fuzzy Set Boundary               |

| Figure 2.7  | Venn Diagram Representation of Three Elements in a Fuzzy Set |

| Figure 2.8  | Membership Function of Classical Set                         |

| Figure 2.9  | Simple Linear Membership Function                            |

| Figure 2.10 | Two Set Membership Function                                  |

| Figure 2.11 | Triangular Membership Function                               |

| Figure 2.12 | Trapezoidal Membership Function                              |

| Figure 2.13 | Two Trapezoidal Membership Functions                         |

| Figure 3.1  | Membership Function Defining Membership in Two Subsets       |

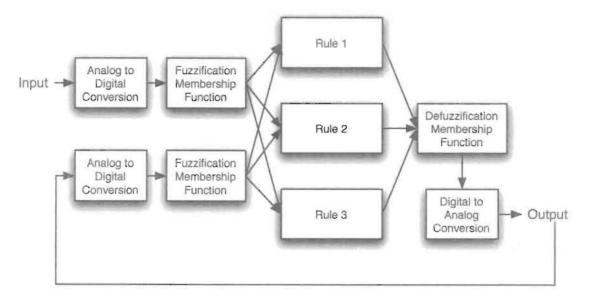

| Figure 4.1  | Sample Fuzzy Controller Block Diagram                        |

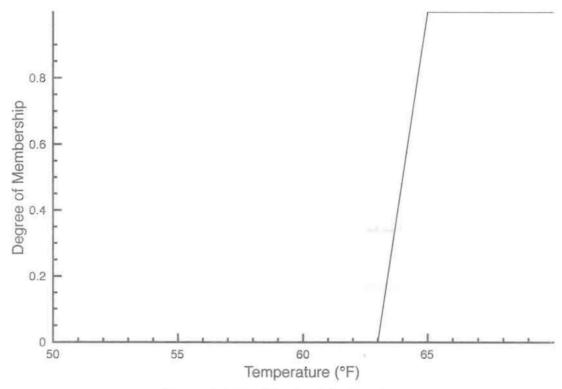

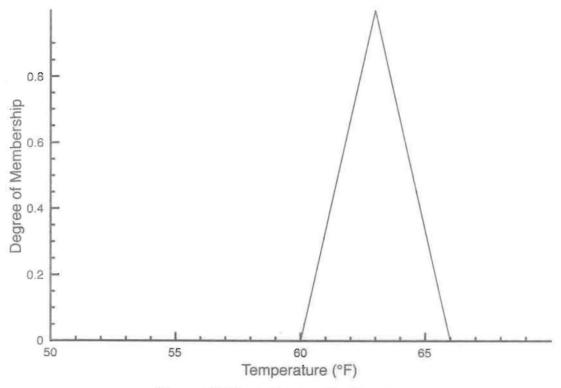

| Figure 5.1  | Hot Membership Function                                      |

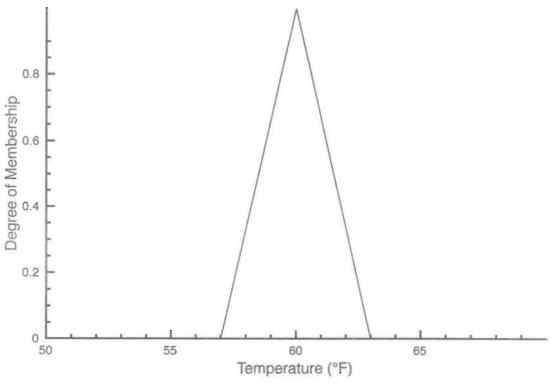

| Figure 5.2  | Warm Membership Function                                     |

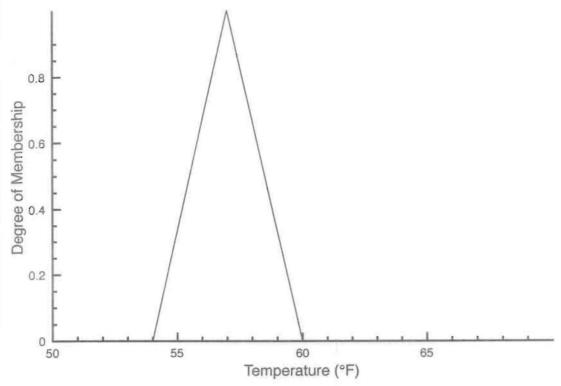

| Figure 5.3  | Neutral Membership Function                                  |

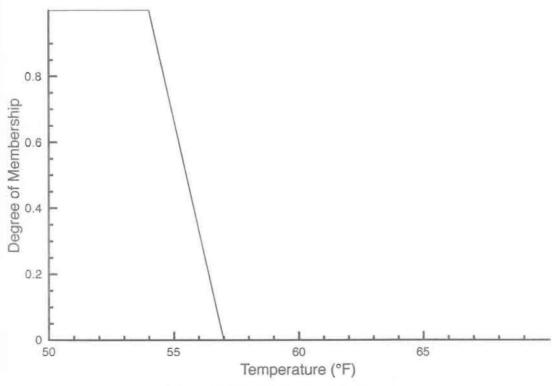

| Figure 5.4  | Cool Membership Function                                     |

| Figure 5.5  | Cold Membership Function                                     |

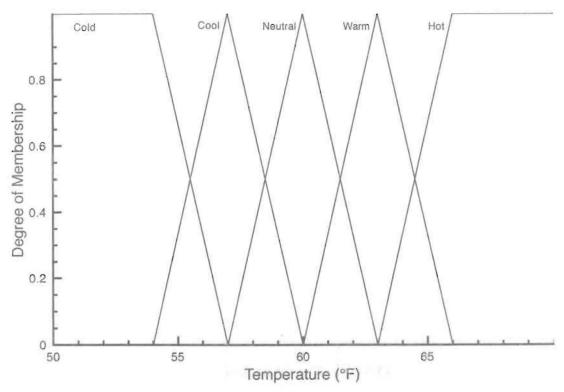

| Figure 5.6  | Temperature Membership Functions                 |

|-------------|--------------------------------------------------|

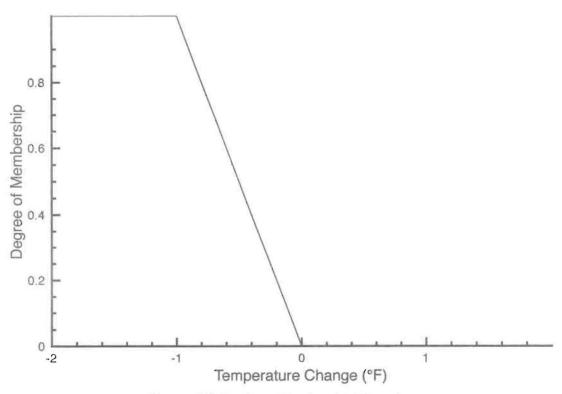

| Figure 5.7  | Cooling Membership Function                      |

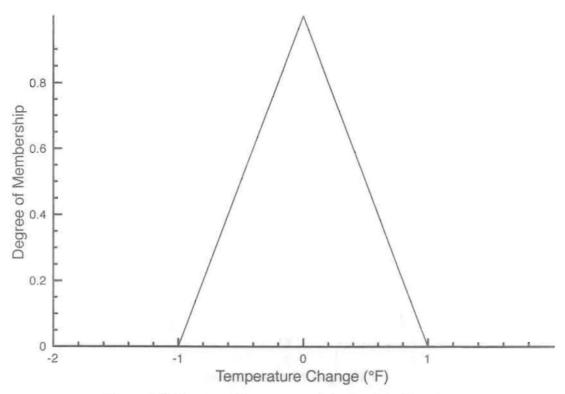

| Figure 5.8  | Constant Temperature Membership Function         |

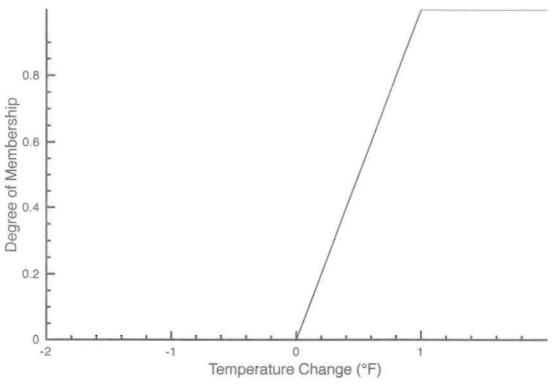

| Figure 5.9  | Warming Membership Function                      |

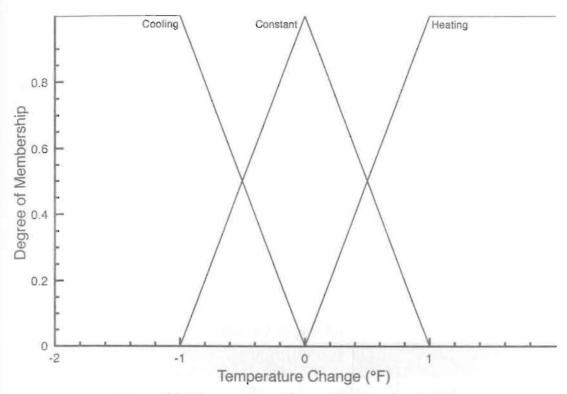

| Figure 5.10 | Temperature Change Membership Functions          |

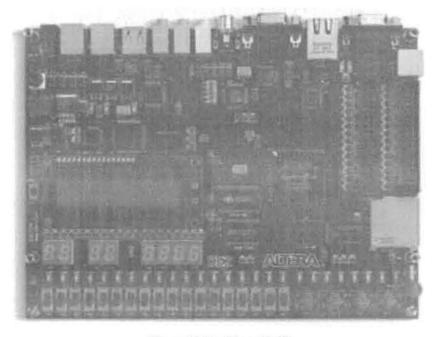

| Figure 5.11 | Altera DE2.                                      |

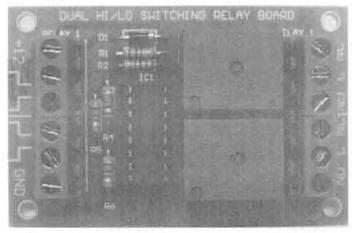

| Figure 5.12 | Carl's Electronics CK1619 Relay Board.           |

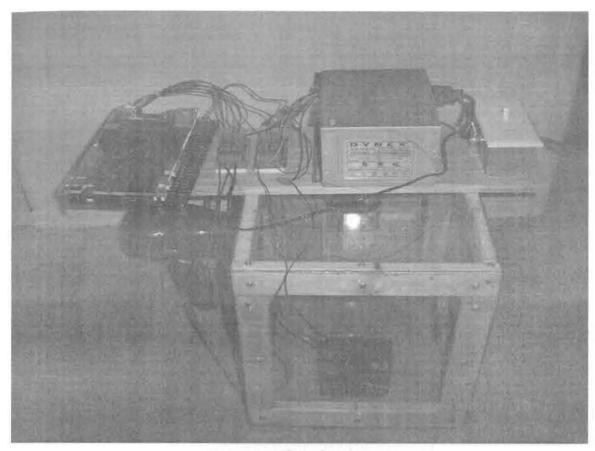

| Figure 5.13 | Complete System.                                 |

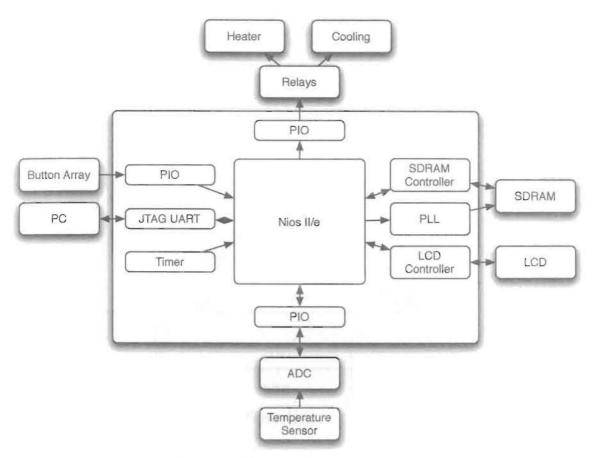

| Figure 5.14 | Micro-Controller Diagram.                        |

| Figure 5.15 | System Response at Various Desired Temperatures. |

# List of Tables

| Table 2.1 | Membership Values for Figure 2.8          |

|-----------|-------------------------------------------|

| Table 2.2 | Membership Values for Figure 2.9          |

| Table 2.3 | Membership Values for Figure 2.10         |

| Table 3.1 | Classical AND Function                    |

| Table 3.2 | Fuzzy AND Function                        |

| Table 3.3 | Classical OR Function                     |

| Table 3.4 | Fuzzy OR Function                         |

| Table 3.5 | Membership Values Derived From Figure 3.1 |

| Table 4.1 | Water Temperature Change Rule Matrix      |

| Table 5.1 | System Rule Base                          |

| Table B.1 | Conjunctive Truth Table                   |

| Table B.2 | Negation Truth Table                      |

| Table B.3 | Implicative Truth Table                   |

| Table B.4 | Equivalent Truth Table                    |

# List of Symbols

A, B, C, X, Y

Subsets of the Universe of Discourse.

a,b,c

Individual elements of the Universe of Discourse.

x

System output after defuzzification.

$\mu(i)$

Firing strength of individual rules.

$\alpha(i)$

Individual rule output.

İ

Current temperature.

T

Desired temperature.

dt

Temperature change per one sample period.

#### Chapter 1

#### Introduction

#### 1.1 Motivation and Background

Natural language and human thought patterns rely heavily on relative and imprecise terms to describe the world. Statements such as "It is warm outside today" are hard to model in computers and modern control systems. These statements lack precision and can contain terms with ambiguous meanings. Warm means one thing to one person and something completely different to someone else. Is there a boundary between what is hot and what is cold? How about what is hot and what is merely warm? To model a system with parameters such as these, the system must be described in precise and unambiguous terms unless a method exists for interpretation and manipulation of relative terms [1].

Assume an example in which all temperatures above 80°F are considered hot and all temperatures equal to or below 80°F are considered cold. This implies that a temperature of 80.0°F is cold and a temperature of 80.1°F is hot. The difference of 0.1°F would not be perceivable by a human being but would define membership in two entirely different sets. It would be more natural to say that a temperature of 80.0°F is 50% hot and 50% cold. There would be almost no difference between the interpretations of the two temperatures if this were the case.

Fuzzy sets allow partial set membership and allow for ambiguity in boundaries between members and nonmembers of a set. An element can be a partial member of one or more sets. Fuzzy sets infer fuzzy logic, in which operations are defined for logical elements that are partly true and partly false. Fuzzy logic and fuzzy sets infer fuzzy control, which is the design of control systems using fuzzy terms.

A properly defined control system can benefit from the ambiguity permitted by fuzzy rules. A control system based on fuzzy set membership and fuzzy logic can be designed with merely a superficial knowledge of the plant to be controlled. This allows for increased modularity and easier, less math-intensive design of controllers [2,3]. The most challenging part of designing a fuzzy controller is the fuzzification of the inputs and the defuzzification of the outputs. Fuzzification and defuzzification are achieved by defining and perfecting the rules of interpretation and membership functions for the system [1]. For example, consider a model of a shower. The input of the shower system is the current temperature of the water and the change in temperature per unit of time. The output of the system is a control signal for a set of solenoid-controlled valves which determine the mixture of the water and, subsequently, the temperature. This system can be modeled with fuzzy terms if the input is reinterpreted to be hot, warm, cool, cold, or any combination of the previous terms. The current temperature along with the temperature change per unit time can be used to determine a control signal. The fuzzy controller determines if the water should be colder or warmer based on the input and adjusts the output accordingly. The output is then converted to a control signal in a process called defuzzification. The end result is a control signal for each solenoid. The benefit is that the designer needs little information about the system to be controlled and

the resulting controller is modular and can be used in other similar systems with only minor modifications.

#### 1.2 History

The notion of fuzzy sets, fuzzy logic, and fuzzy control has been around for about forty years. In 1965 Professor Lotfi Zadeh of the University of California at Berkley wrote a paper titled *Fuzzy Sets* in the journal *Information and Control*. The paper presented and defined the concept of a fuzzy set as well as operations that can be performed on those sets. The first successful application of fuzzy control was not seen until 1975 when a fuzzy-controlled cement kiln came online in Denmark [4,5].

Fuzzy control suffered from a lack of popularity in the United States until recently because of the imprecise nature of the control scheme and a perceived relationship to artificial intelligence, which was not popular in the United States at the time [4]. There are many applications of fuzzy control available today and it is gaining in popularity as it becomes a more credible control method.

It must be noted that there are many areas of future research pertaining to fuzzy control. The questions of stability and optimality have yet to be answered to any degree of certainty.

## 1.3 Empirical Experiment

In order to present a practical example of the material covered in this work, an empirical experiment is designed and constructed. A model of a confined space in which temperature is to remain constant is constructed. The confined space is created in the form of a box containing one cubic foot of air. The air temperature is increased and

decreased with a heating element and cooling system which are housed within the cubic foot enclosure.

The fuzzy controller is designed and implemented on a Nios II microprocessing platform, part of an Altera Cyclone II FPGA. The FPGA and Nios II processor allow for easy reprogramming and are scalable to support larger designs. The schematics and source code for the experiment and the controller design are provided. The results of an experiment designed to show that the fuzzy controller is a viable control scheme are also presented.

#### 1.4 Organization

The first chapter of this paper presents an introduction and motivation for studying fuzzy control techniques as well as an introduction to the system whose design and optimization are detailed in Chapter 5. The second chapter introduces the concept of fuzzy sets and related mathematical functions. The third chapter deals with fuzzy logic and fuzzy-based logical operations. An introduction to fuzzy control schemes is provided in Chapter 4. The fifth chapter presents an empirical example of a fuzzy control system along with experimental results. Appendices provide background information and source code for the example system.

#### Chapter 2

#### **Fuzzy Sets**

#### 2.1 Introduction to Fuzzy Sets

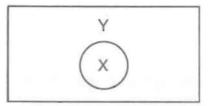

A classical set, as described in Appendix A, is defined as a grouping of elements with similar properties. All possible members define a universe of discourse. Every element of the universe of discourse is either a member of the subset or not a member of the subset. The Venn diagram in Figure 2.1 shows a subset of numbers (A) contained within a universe of discourse. The boundary is crisp and unambiguous and every element is defined as a member or a non-member. Figure 2.2 shows two sets (A and B), both subsets of the universe of discourse. The two sets do not contain any of the same elements. All elements of the universe of discourse are either a member of A, a member of B, or a member of neither. There are no members that belong to both A and B [6,7,8].

Figure 2.1 Venn Diagram and Single Subset.

Figure 2.2 Venn Diagram and Two Subsets.

If a subset, C, is defined such that it that contains all of the elements that are members of either subset A or subset B, then C is referred to as the union of subset A and subset B.

$$A \cup B = C \tag{2.1}$$

The shaded region of Figure 2.3 represents the subset C.

Figure 2.3 Venn Diagram Representing A Union B.

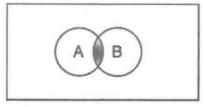

Figure 2.4 represents two sets (A and B) contained within the universe of discourse. The two sets are seen to overlap, representing a small subset of elements which are members of A as well as members of B. This small subset is referred to as the intersection of subset A and subset B.

$$A \cap B = C \tag{2.2}$$

The shaded region of Figure 2.4 represents the intersection of subset A and subset B. Elements in the shaded region are members of subset A and subset B.

Figure 2.4 Venn Diagram of A Intersection B.

Classical set theory makes a very clear distinction between membership and non membership in a subset (see Appendix A for a detailed introduction to classical set theory). Reality does not follow such crisp boundaries. For example, consider a universe of discourse consisting of all students in a class. Define two subsets  $\{X, Y\}$  where X is the subset of all students considered tall, and Y is the subset of all short students [9].

Defining the membership of the sets using classical logic would result in two subsets with no intersection. One subset would contain all people who are considered tall and the other would contain all people who are considered short. There would not be anyone that is considered both tall and short. Figure 2.5 represents this situation [9].

Figure 2.5 Venn Diagram Representation of Tall/Short Example.

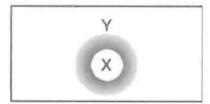

How does one classify people who are of exactly average height? Figure 2.6 shows what it would look like if the boundary were made less crisp and some ambiguity was allowed. The gradient shaded region represents a group of people who are partially tall as well as partially short.

Figure 2.6 Venn Diagram Representing a Fuzzy Set Boundary.

Figure 2.7 shows three possible elements  $\{a,b,c\}$  and their representative position in the universe of discourse. Element a is clearly outside the boundary and would therefore be considered short. Element c is clearly within the boundary and would

therefore be considered tall. Element b falls within the shaded border and is therefore not entirely a member of either set. The element is defined as partially contained within X and partially contained within Y. The relative percentage of membership is defined with a mathematical function called a membership function.

Figure 2.7 Venn Diagram Representation of Three Elements in a Fuzzy Set.

#### 2.2 Membership Functions

Set membership is defined with a mathematical function aptly named a membership function. Elements of a universe of discourse that are being grouped into subsets were traditionally either included or not included in the subset. If it is desired to make them partially included in the subset there must be a definition of the degree of membership. The membership function is used to make the conversion from classical, unambiguous set theory into fuzzy set theory. The creation of the membership function plays a very significant role in the performance of the fuzzy system. Membership functions must be carefully chosen and tuned appropriately to maximize efficiency and performance [1,10,11,12].

Membership functions are almost always represented graphically. The axis of abscissas represents all values in the specified universe of discourse. Generally, this axis should range from the lowest possible value to the highest possible value for any defined universe of discourse. The ordinate axis is a normalized representation of the degree of membership. It may be easier to think of the ordinate axis as a percentage of membership

as the values range from 0 to 1, inclusive. The function relates the element value to its respective membership degree.

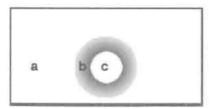

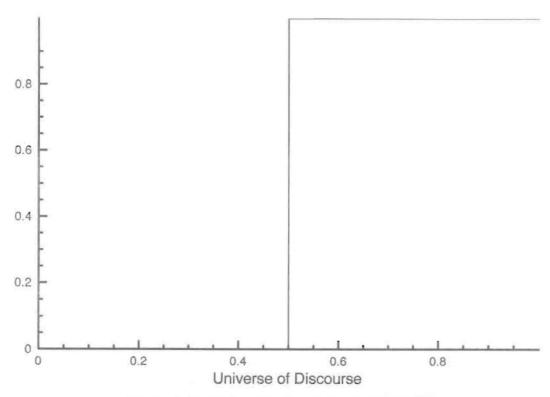

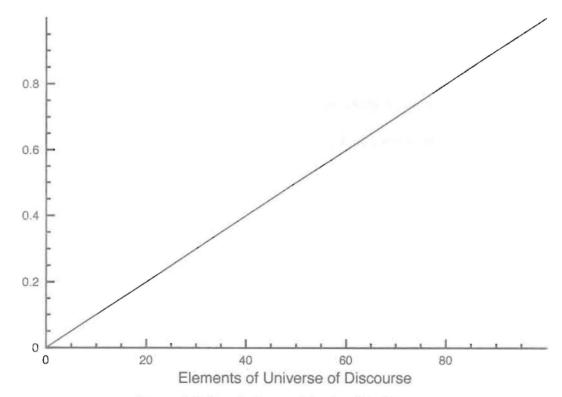

Figure 2.8 shows what a membership function would look like when applying classical set theory. The function does not allow for partial membership, the set includes all numbers greater than or equal to 0.5. In comparison, Figure 2.9 shows a sample of a trivial fuzzy membership function. The values corresponding to the membership functions in Figure 2.8 and Figure 2.9 are tabulated in Table 2.1 and Table 2.2, respectively.

Figure 2.8 Membership Function of Classical Set.

Table 2.1 Membership Values for Figure 2.8.

| Element | Membership |

|---------|------------|

| 0       | 0          |

| 0.499   | 0          |

| 0.500   | 1          |

Figure 2.9 Simple Linear Membership Function.

Table 2.2 Membership Values for Figure 2.9.

| Element | Membership |

|---------|------------|

| 0       | 0          |

| 20      | 0.2        |

| 1       | 1          |

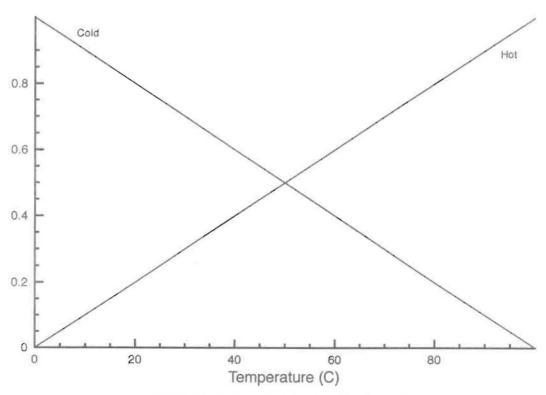

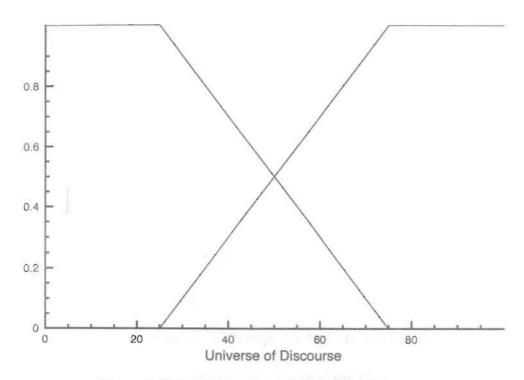

The example in Figure 2.9 is trivial and only defines membership in one subset. It is possible and usually desired to expand this to multiple subsets. An example of such membership functions is depicted in Figure 2.10 along with associated numerical values listed in Table 2.3. Each line represents a subset and the corresponding membership value for each element in that subset. Since classical rules no longer apply it is common and even desired to have an element be a member of multiple subsets. Consider the membership function in Figure 2.10 representing membership in two subsets {hot, cold}. The universe of discourse is comprised of all possible temperature readings. It can be noted that in this example the total membership of every element is equal to unity but this is merely a coincidence and is in no way required for a membership function.

Figure 2.10 Two Set Membership Function.

Table 2.3 Membership Values for Figure 2.10.

| Element | Hot Membership | Cold Membership |

|---------|----------------|-----------------|

| 0       | 0              | 1               |

| 25      | 0.25           | 0.75            |

| 75      | 0.75           | 0.25            |

| 100     | 1              | 0               |

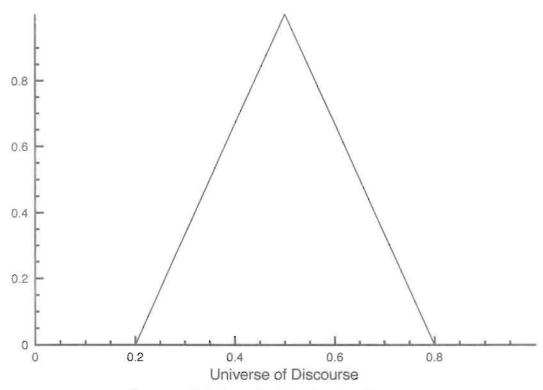

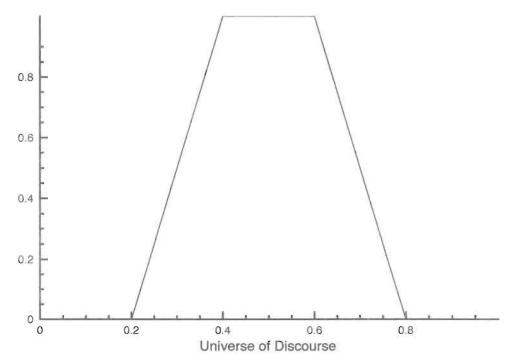

Membership functions can take many forms, depending largely on the system being modeled. The choice of the membership function is made by the engineer designing the system and has many consequences on the performance of the system. The consequences of such decisions are elaborated upon when discussing input fuzzification in Chapter 4. Some common forms of membership functions are shown in Figures 2.11-2.13. This list of functions is by no means inclusive and functions can be created for virtually any system [9]. Also, it is often desirable to combine membership functions depending on the system being modeled.

Figure 2.11 Triangular Membership Function.

Figure 2.12 Trapezoidal Membership Function.

Figure 2.13 Two Trapezoidal Membership Functions.

#### Chapter 3

#### Fuzzy Logic

#### 3.1 Introduction to Fuzzy Logic

Classical logic is concerned with deriving truth or falsity from propositions and combinations of propositions. The notation and operations performed on classical logic statements are described in more detail in Appendix B. A hallmark of classical logic is that every statement is either true or false. There can be no statements which are partly true or partly false, and certainly no statements that are equally true and false. This limitation is addressed with the introduction of fuzzy logic [1].

A parallel can be drawn between the relationship between classical and fuzzy sets and the relationship between classical and fuzzy logic. Consider a subset of the universe of discourse which consists of all elements which can be proven to be true. In classical set theory, each element is either a member or not a member of the truth subset. Changing the rules from classical to fuzzy subsets allows partial membership in the proven true subset as well as the not proven true subset. An element can now be either a full member of one subset or a partial member of both subsets. It is important to note that fuzzy logic fully complies with the rules of classical logic in both extreme cases, no membership and full membership (0 and 1).

The operations of fuzzy logic are described in the following section and the material is borrowed heavily from [9].

#### 3.2 Fuzzy Logic Operations

It was previously noted that in the completely true and completely false cases fuzzy logic follows the rules of classical logic. Consider the truth table in Table 3.1, which represents the truth table for a standard logical AND function. As expected, the statement A AND B is only true if A and B are both true. This classical logic conclusion is preserved if the function is reconsidered to be the minimum of A and B as in Table 3.2. In the extreme case where A and B are both completely true, the result is still completely true. However, the function now allows for partial membership and is no longer compliant with the rules of classical logic [1].

Table 3.1 Classical AND Function.

| A | В | A AND B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

Table 3.2 Fuzzy AND Function.

| A | В | A AND B  |

|---|---|----------|

| а | b | min(a,b) |

In a similar fashion the OR and NOT functions can be reconsidered as shown in Tables 3.3 and 3.4. The logical OR function is changed to a maximum function, which follows the rules of classical as well as fuzzy logic. The logical NOT function is

reconsidered as an algebraic (1 - A) function which also adheres to the classical as well as fuzzy rules.

Table 3.3 Classical OR Function.

| A | В | AORB | max(A,B) |

|---|---|------|----------|

| 0 | 0 | 0    | 0        |

| 0 | 1 | 1    | 1        |

| 1 | 0 | 1    | 1        |

| 1 | 1 | 1    | 1        |

Table 3.4 Fuzzy OR Function.

| A | NOTA | (1 - A) |

|---|------|---------|

| 0 | 1    | 1       |

| 1 | 0    | 0       |

The conversion of the three basic logical operators leads to a discussion on classical and fuzzy logical statements. A statement such as

if

$$X$$

is  $A$  then  $Y$  is  $B$  (3.1)

can be interpreted as a classical implication if A and B are subsets in the classical sense. However, if A and B are fuzzy subsets then the statement takes on a new meaning. If membership in A and B were defined using fuzzy subset theory then the elements would only have a degree of membership and the implication above now relates the degrees of membership. Once again, it is important to note that in the extreme case, the fuzzy rules apply to classical logic as well. For example, consider the statement above (3.1). If X has a degree of membership of 0.7 in A then the implication implies that Y has a 0.7

degree of membership in B. In other words, partial antecedents imply partial consequents

[6].

The antecedent can contain multiple terms, in which case they must be resolved to a single degree of membership using the techniques discussed earlier in this section.

Consider the following example.

Assume that the rules of a given system are:

if

$$x$$

is  $A$  AND  $y$  is  $B$  then  $z$  is  $C$  (3.2)

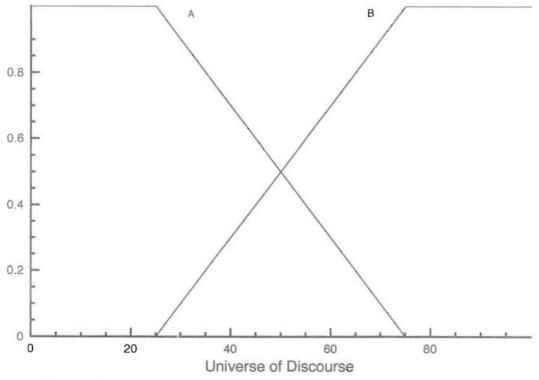

Also consider the membership function defined by Figure 3.1. The function defines membership in two subsets  $\{A,B\}$ . Table 3.5 lists the sampled values and their corresponding membership values. Since x is a 0.7 member of A and y is a 1.0 member of B then z is minimum(0.7, 1.0) = 0.7 member of C.

Figure 3.1 Membership Function Defining Membership in Two Subsets.

Table 3.5 Membership Values Derived From Figure 3.1.

|        | A   | В   |

|--------|-----|-----|

| x = 40 | 0.7 | 0.3 |

| y = 80 | 0   | 1   |

#### Chapter 4

#### **Fuzzy Control**

### 4.1 Introduction to Fuzzy Control

It was previously mentioned that fuzzy control systems can be designed with only a superficial knowledge of the plant to be controlled. Fuzzy control is ideal when a precise mathematical model of the plant does not exist or if the control process using traditional methods is too expensive in terms of required computational power. In these cases, it is often desirable to design a simple system based on rules governed by empirical data and observation [4].

There are six assumptions that an engineer must be willing to make before selecting a fuzzy controller based approach. The following six rules were inspired by Ross [1].

- The plant is observable and controllable. All state, input, and output variables are available for measurement or computation.

- 2. There is comprehensive operational knowledge of the plant to be controlled. A mathematical model is not required but knowledge of operation, consisting of operator knowledge and engineering common sense is required to devise a set of literary rules to define operation of the controller.

- The engineer assumes that a solution exists.

- 4. The fuzzy controller is be "good enough" to accomplish the desired result but may not be the optimal solution.

- The precision of the controller is limited and must be designed within an acceptable tolerance range. One objective of the fuzzy controller is to minimize computation and computing cost so an overly-precise system will negate this advantage.

- 6. There is no accepted methods of determining stability or optimality for fuzzy controllers. This is an area for further study. The designing engineer should thoroughly test the system for instability and inaccuracy before finalizing the design.

Once the decision to use a fuzzy controller is made there are several steps to follow in order to design and implement the controller. The steps, presented below, are borrowed from [1] and are the topic of discussion for the rest of this chapter.

- Identify all system variables. Inputs, outputs, and all state variables must be identified and defined.

- Identify and partition the universe of discourse into smaller, fuzzy subsets. Assign each subset a linguistic title for later use.

- 3. Create a membership function for each fuzzy subset.

- Create the rule base for the system by determining the relationship between the input fuzzy subsets and the output fuzzy subset.

- 5. Normalize the inputs to fall within the tolerance interval defined for the system.

- 6. Fuzzify the inputs.

- 7. Implement fuzzy logic to determine the output for each rule in the rule base.

- Combine the output of all rules based upon the aggregation method chosen for the system.

- 9. Defuzzify the outputs to produce a crisp output signal.

The procedure provided above works well for simple fuzzy systems and is discussed in greater detail in what follows. The design example presented in the next chapter also follows this design procedure.

#### 4.2 Preliminary Design

The design procedure from the previous section indicates that the first step in the design process is to identify variables and states. This step may seem trivial but it is important to consider the hardware that one will implement and choose sensors and other inputs accordingly. If the system does not have enough sensors it can not make accurate control decisions. Too many sensors will dramatically increase the complexity of the system and also the computational effort required to control the system. Therefore, balance must be struck and the optimal set of inputs and states must be defined.

As an example, consider the system presented in the next chapter. The system implements a fuzzy controller for a temperature-control process. At first glance, it may seem necessary to know the ambient temperature of the air outside of the box, however that would add a sensor input. This sensor input must be fuzzified and also contained in the rule base. It is much more reasonable to only measure the temperature of the confined space and also extract, from that data, the temperature change per unit time. Those two inputs would only require one sensor and would minimize the amount of computations required for the system to be controlled.

Choice of sensor is very important. Since the system will fuzzify the inputs it does not make good design sense to have only binary sensors as inputs because it would negate the primary advantage of the fuzzy controller; the fuzzy controller takes an analog input and uses the rules of the system to develop an analog output. Although the binary case is still able to be handled with a fuzzy controller it may be easier and less expensive to implement with combinational logic [1].

The second step of the design procedure consists of identifying and partitioning the universe of discourse. As discussed in Chapter 2, the universe of discourse consists of all possible input values for the system being designed. Careful consideration should be given to ensure that all possible values are accounted for. All values in the universe of discourse should be at least a partial member of one of the subsets to avoid the possibility of the controller producing an indeterminate output signal. The choice of subset title is up to the designing engineer but should be descriptive as it will be used to create the membership functions and the rule base that defines the system.

Each fuzzy subset will generate one curve on the membership function. The choice of the shape of the curve is to be made by the design engineer based on knowledge of how the system operates. The membership function curve for each fuzzy subset will be tuned to produce the most accurate output signal. The triangular shape is the most commonly used and can be properly tuned for most systems but there are other possibilities as discussed previously [9].