# A DIGITAL CIRCUIT DESIGN IMPLEMENTATION USING ABEL-HDL AND PROGRAMMABLE LOGIC DEVICES

by

Richard B. Alcorn

Submitted in Partial Fulfillment of the Requirements

for the Degree of

Master of Science in Engineering

in the

Electrical Engineering

Program

YOUNGSTOWN STATE UNIVERSITY

June, 1997

# A DIGITAL CIRCUIT DESIGN IMPLEMENTATION USING ABEL-HDL AND PROGRAMMABLE LOGIC DEVICES

# Richard B. Alcorn

I hereby release this thesis to the public. I understand this thesis will be housed at the Circulation Desk of the University library and will be available for public access. I also authorize the University or other individuals to make copies of this thesis as needed for scholarly research.

| Signature: | Roll R. alen                           | 5/26/97         |

|------------|----------------------------------------|-----------------|

|            | Student                                | Date            |

| Approvals: |                                        |                 |

|            | Salvature R. Pansing<br>Thesis Advisor | 5/26/97<br>Date |

|            | Robert & Touckey                       | 5-28-57<br>Date |

|            | Committee Member                       | 5/30/97<br>Date |

|            | Dean of Graduate Studies               | 6/2/97<br>Date  |

|            |                                        |                 |

## **ABSTRACT**

The purpose of this thesis is twofold. The first is to use ABEL-HDL design software and Programmable Logic Devices (PLD's) to implement the logic of a digital circuit in a more efficient manner than classic digital design techniques allow. The second is to give enough introductory details about PLD's and the ABEL design process that other students may use this thesis as a guide in learning to use ABEL and PLD's in their digital designs. The thesis explores some ABEL design techniques for programming PLD's and applies the concepts to reducing the total chip count of a digital circuit created by the author using 7400-series logic in a previous graduate course. The results of the experimental design implementation are discussed and ideas given for further study into the topic by future thesis students.

## **ACKNOWLEDGEMENTS**

Very special thanks go to Professor Samuel Skarote for being on my thesis committee, for being my thesis advisor up until his retirement in June 1996, and for all of his help and guidance, both academic and personal, throughout my undergraduate and graduate years at Youngstown State University. I apologize for not finishing this thesis before his retirement. I would also like to express my thanks to Dr. Salvatore Pansino for being my thesis advisor and to Dr. Robert Foulkes for being on my thesis committee. In addition, I wish to thank Makin and Associates, Inc. of Mayfield Village, Ohio for their generosity in giving me free samples of Lattice GAL26CV12 devices to use in my experimental circuit. Finally, credit should be given to William I. Fletcher of Utah State University for the origins of the experimental circuit discussed in this thesis. The concept appeared as a homework problem (# 7-2, pg. 516) in his textbook An Engineering Approach to Digital Design 1 and later appeared in revised form on a test given by Dr. Pansino in the EE825 Sequential Logic Circuit Analysis and Design class. I was inspired by the concept and turned it into a full-fledged design project in Prof. Skarote's EE932 Digital Systems Engineering II class.

# TABLE OF CONTENTS

|             |       |                                          | PAGE |

|-------------|-------|------------------------------------------|------|

| ABSTRACT    |       |                                          | iii  |

| ACKNOWLE    | EDGEN | MENTS                                    | iv   |

| TABLE OF C  | CONTE | ENTS                                     | v    |

| LIST OF FIG | URES  |                                          | vii  |

| CHAPTER     |       |                                          |      |

| I.          | INTR  | RODUCTION                                | 1    |

| II.         | AN C  | OVERVIEW OF PLD'S                        | 4    |

|             | 2.1   | Historical Background                    | 4    |

|             | 2.2   | Types of PLD's                           | 6    |

| III.        | AN C  | OVERVIEW OF ABEL-HDL                     | 16   |

|             | 3.1   | Program Features                         | 16   |

|             | 3.2   | Command Syntax                           | 17   |

|             | 3.3   | Source File Structures                   | 19   |

|             | 3.4   | ABEL Design Flow                         | 22   |

| IV.         | ORIC  | GINAL EXPERIMENTAL DESIGN IMPLEMENTATION | 24   |

|             | 4.1   | Design Concept                           | 24   |

|             | 4.2   | Game Controller                          | 26   |

|             | 4.3   | Output Controller                        | 27   |

|             | 4.4   | Timing Controller                        | 29   |

|             | 4.5   | Input Conditioner                        | 31   |

|            |             |                                       | PAGE |

|------------|-------------|---------------------------------------|------|

| V.         | ABEI        | L EXPERIMENTAL DESIGN IMPLEMENTATION  | 33   |

|            | 5.1         | Design Concept                        | 33   |

|            | 5.2         | GAMECON                               | 34   |

|            | 5.3         | OUTCON                                | 38   |

|            | 5.4         | TIMECON                               | 41   |

|            | 5.5         | INPUTCON                              | 47   |

|            | 5.6         | Additional Notes                      | 48   |

| VI.        | CON         | CLUSION                               | 50   |

|            | 6.1         | Project Results                       | 50   |

|            | 6.2         | Summary                               | 52   |

|            | 6.3         | Ideas for Future Research             | 53   |

| APPENDIX . | A.          | ABEL DESIGN PROCESS DOCUMENTATION     | 54   |

|            | <b>A</b> .1 | GAMECON Documentation                 | 54   |

|            | A.2         | OUTCON Documentation                  | 60   |

|            | A.3         | TIMECON Documentation                 | 65   |

|            | A.4         | INPUTCON Documentation                | 71   |

| APPENDIX   | В.          | MANUFACTURER DATA SHEET EXCERPTS      | 75   |

|            | <b>B</b> .1 | Lattice GAL16V8 Data Sheet Excerpts   | 76   |

|            | B.2         | Lattice GAL22V10 Data Sheet Excerpts  | 85   |

|            | B.3         | Lattice GAL26CV12 Data Sheet Excerpts | 90   |

| REFERENCE  | E <b>S</b>  |                                       | 95   |

# LIST OF FIGURES

| FIGU | RE                                                               | PAGE |

|------|------------------------------------------------------------------|------|

| 1.1  | Comparison of a 7400-series circuit and the PLD that replaces it | 2    |

| 2.1  | Example of a PROM device                                         | 7    |

| 2.2  | Example of a PLA device                                          | 8    |

| 2.3  | Example of a PLA device (F105) with registers and feedback       | 9    |

| 2.4  | Example of a PAL device                                          | 10   |

| 2.5  | Example of a combinatorial PAL (P16L8)                           | 11   |

| 2.6  | Example of a registered PAL (P16R4)                              | 12   |

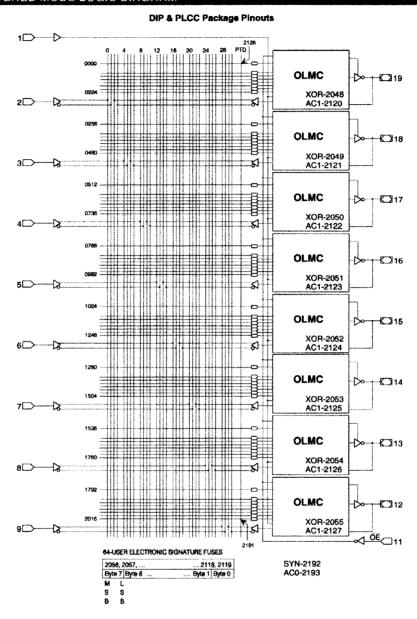

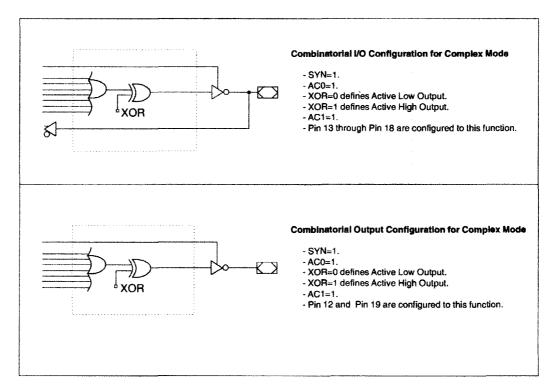

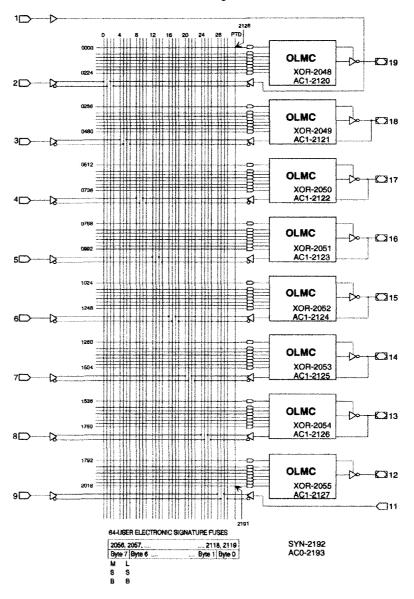

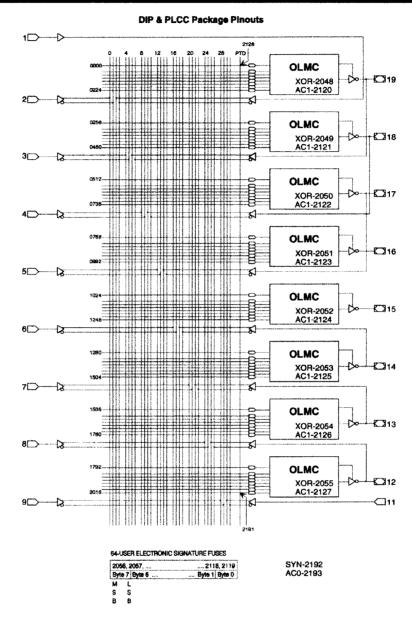

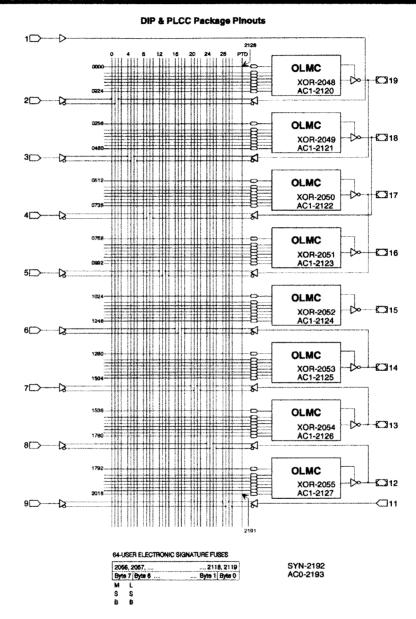

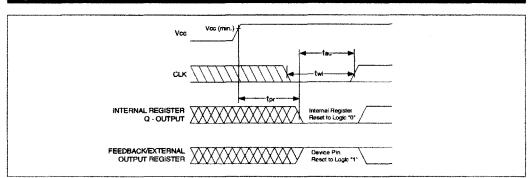

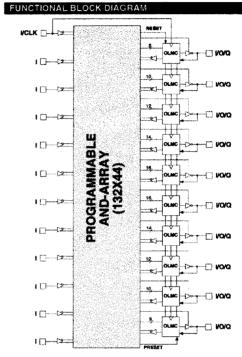

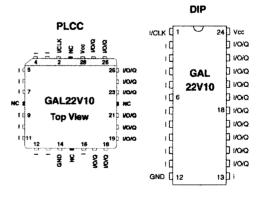

| 2.7  | Example of a macrocell PAL device (GAL22V10)                     | 13   |

| 2.8  | GAL22V10 macrocell configurations                                | 14   |

| 3.1  | Sample ABEL logic design source file                             | 20   |

| 3.2  | A sample ABEL Design Environment screen                          | 22   |

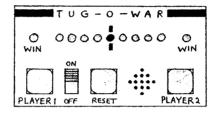

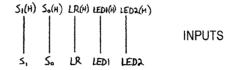

| 4.1  | Tug of War game concept                                          | 25   |

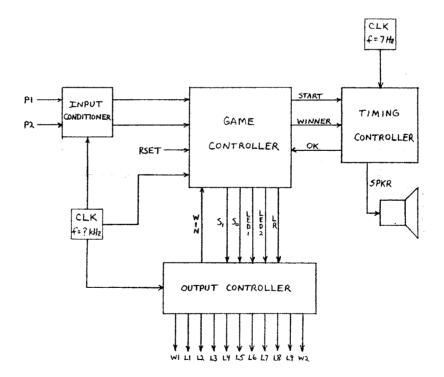

| 4.2  | Block diagram of original system design implementation           | 25   |

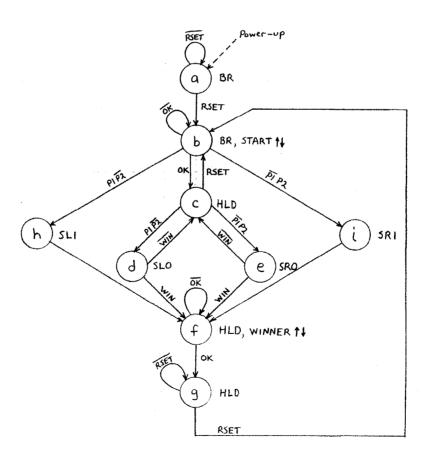

| 4.3  | State diagram of Game Controller circuit                         | 26   |

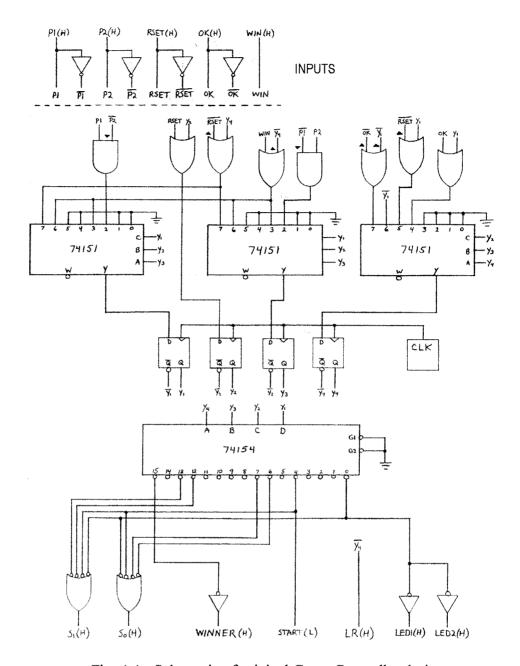

| 4.4  | Schematic of original Game Controller design                     | 27   |

| 4.5  | Schematic for original Output Controller circuit                 | 28   |

| 4.6  | State diagram for original Timing Controller design              | 29   |

| 4.7  | Schematic of original Timing Controller circuit                  | 30   |

| 4.8  | Timing and state diagrams for original Input Conditioner circuit | 31   |

| 4.9  | Schematic of original Input Conditioner circuit                  | 32   |

| FIGU | JRE                                           | PAGE |

|------|-----------------------------------------------|------|

| 5.1  | GAMECON source file                           | 35   |

| 5.2  | OUTCON source file                            | 39   |

| 5.3  | TIMECON state diagram                         | 42   |

| 5.4  | TIMECON source file                           | 43   |

| 5.5  | INPUTCON source file                          | 47   |

| 6.1  | Schematic of PLD implementation of Tug of War | 51   |

### **CHAPTER 1**

### INTRODUCTION

Major improvements have been made in the field of digital circuit design in the last 15 to 20 years. As many are aware, advancements have been made in chip fabrication techniques allowing greater operating speed, lower power consumption, and improved reliability. However, the most revolutionary improvement in digital design has been the types of devices in which designs may be implemented. One of the most popular of these is a class of devices known as Programmable Logic Devices (PLD's). PLD's and some programming techniques for using them in digital designs will be emphasized in this paper.

Every undergraduate Electrical Engineering student is exposed to digital design techniques during the course of his or her study. These digital design courses generally employ 7400-series TTL logic chips as the devices of choice for implementing designs. From an academic point of view, this makes sense in that these devices typically contain only a few logic gates or flip-flops per chip and are easily understood by newcomers to the subject of digital design. These devices are commonly available, inexpensive, require no special programming, and merely need to be powered and wired properly to work in a circuit. However, breadboarding and debugging anything more than a simple circuit can be extremely time-consuming and frustrating. The number of logic chips needed to implement the design can also become quite large. Power consumption and the physical size of the final circuit are also valid concerns. For these and other reasons industry has tended to shy away in most cases from using 7400-series logic for most digital circuit designs.

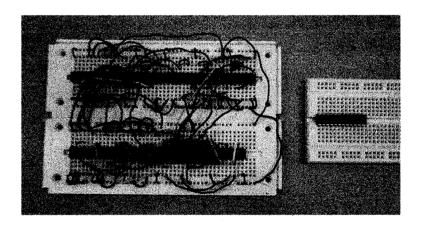

On the other hand, Programmable Logic Devices (PLD's) allow digital circuit designers to implement designs with just a few chips, the actual number depending on the complexity of the design and the types of devices used for implementation. Combinatorial or sequential designs may be programmed into a PLD by the user via a device programmer unit. The resultant device is able to perform the same logic functions that would've taken numerous 7400-series chips to accomplish using traditional design methods (Figure 1 shows an example of this). Breadboarding times drop enormously, and most debugging can be done at the design level rather than at the physical device and circuit level. The reduction in chip count also leads to reductions in power consumption, physical circuit size, and cost. For these reasons, programmable logic is now employed in many commercial and industrial digital circuit designs.

Fig. 1.1 - Comparison of a 7400-series circuit (left) and the PLD that replaces it (right)

The ABEL Hardware Description Language from Data I/O Corporation is used in this project for all PLD programming and in all of the programming examples and descriptions. It's a very powerful software package for programming PLD's, but it has a significant learning curve. To the best of the author's knowledge, the work done in this project goes much further into this subject than what any other YSU Electrical Engineering student has done thus far. Therefore, this project and paper may be useful as

a guide to other students who wish to use ABEL-HDL and PLD's in their designs. The lessons and techniques that were learned by the author and are presented here could save others some struggling and headaches and get them on the road to programming PLD's more quickly. This forms a secondary purpose of the thesis and is responsible for the order of appearance of the subjects presented.

The main purpose of this project is to investigate and test some methods of using ABEL-HDL design techniques and PLD's to reduce the chip count of a digital circuit. After an introduction to PLD types and their features (Chapter II), the ABEL-HDL design software is examined with respect to command types and program file structures (Chapter III). This knowledge is then applied to reduce the chip count in an experimental circuit designed and built by the author in a previous graduate digital design course, employing 7400-series design techniques and devices. Despite efforts to make the original design as efficient as possible, the final chip count totaled 31. In contrast, the final PLD implementation requires only 4 devices in order to duplicate the logic of the original circuit (plus a few chips used to isolate the PLD chips from possible harm). The original experimental circuit design is discussed in Chapter IV. This is then followed by the PLD experimental circuit design in Chapter V.

Finally, the project results are examined and some ideas for future research are given. During the course of this project, various problems or items of interest were encountered that could provide a student an opportunity for further study, but were deemed by the author to be outside the scope of this thesis project. These are presented in Chapter VI.

### **CHAPTER II**

#### AN OVERVIEW OF PLD'S

## 2.1 - Historical Background

Until the mid 1970's, digital circuit designers basically had two choices in how to physically implement their designs. The first method was to use off-the-shelf 7400-series devices to build their circuits. This technique had advantages such as low development costs, short design times, and the ability to build and test circuits without the need for specialized programming equipment. However, circuits constructed in this manner tend to be large in size and power consumption. The second method was to use mask-programmed devices. These were custom manufactured (often by photo-etching) devices produced by chip foundries that were designed to satisfy the logical functions specified by the customer's design. Generally, the equivalent logic of hundreds or thousands of gates can be implemented in one device package. Using these devices in designs leads to smaller circuit sizes along with reduced power requirements. However, design times for mask-programmed devices are usually long and development costs can be high. Also, elaborate and complicated testing procedures are often needed to evaluate the programmed devices. For these and other reasons, large production volumes of the end circuit are generally necessary in order to justify using these devices in digital designs. It was apparent that a desirable solution for digital circuit designers would be to have devices with relatively large equivalent gate densities, but also have the ability to be programmed by the designer. This would result in a best of both worlds situation: the

reduced circuit size afforded by mask-programmed devices, and the design flexibility of off-the-shelf devices.

The early 1970's saw the introduction of the first PROM (Programmable Read-Only Memory). It was soon found that these devices could be used to implement some simple logic functions as well as their intended data-storing function. These devices quickly became popular with designers. However, PROM's were limited in what types of logic functions they could implement.

The PLA (Programmable Logic Array) made it's appearance in the mid 1970's. This type of device allowed designers to program logic functions using classic SOP (Sum of Products) format. The PLA was originally just a combinatorial logic device. However, it did not take chip manufacturers long to add feedback paths and flip-flops, thus creating a class of PLA-based devices capable of implementing sequential logic as well.

PLD's finally caught on in popularity with digital designers after the introduction of the PAL (Programmable Array Logic) in the late 1970's. These devices also feature SOP logic implementation and come in combinatorial and registered forms. However, they forfeit some of the user-programmability of the PLA in favor of device speed and simplicity. Regardless, PAL-type devices have grown to be one of the most popular PLD types in use today. They have grown to include many advanced features that can be controlled by the designer. CMOS versions have also been introduced. These devices may be erased electrically and reprogrammed by the designer, making the design and debugging process more efficient and cost-effective.

Universal programming software became readily available in the early 1980's and quickly found a home on personal computers. ABEL-HDL from Data I/O Corporation was one of the first full-featured design software packages and is still an industry standard today. Other software packages are also commonly used in industry, an example of which is CUPL (Common Universal tool for Programmable Logic) from Logical Devices. It was initially developed at about the same time ABEL-HDL was being

developed. Many other software packages exist which tend to offer fewer design features. Device manufacturers also occasionally offer design software that is oriented toward their particular brand of devices.

The last major advancement in programmable logic occurred in the mid-1980's with the introduction of the FPGA (Field Programmable Gate Array). With an equivalent gate density in the thousands and performance rivaling that of mask-programmed devices, this type of device was a radical departure from PLD's. FPGA's are made up of many LCA's (Logic Cell Array) along with signal routing lines. The LCA essentially consists of a small number of gates that can be programmed to implement a simple logic function. These LCA's are then connected by the user with programmable signal routes. This arrangement leads to greater design flexibility than PLD's can offer, but also more complex methods of programming. Except for the fact that they are programmable devices, FPGA's are so different in design from PLD's that they may be considered to be a family of devices outside the realm of PLD's. For this reason, the author chose not to focus attention on them.

## 2.2 - Types of PLD's

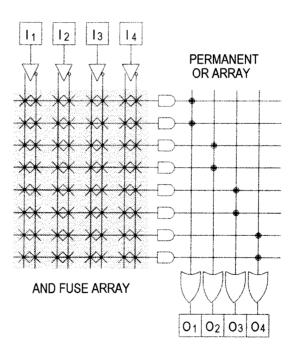

The device structures of PROM's, PLA's, and PAL's each contain programmable fuse arrays that are used by the designer to program the desired logic functions into the device. Array connections that are not needed for the design logic have their respective fuses blown. Fuses are left intact for array connections that are necessary for the programmed logic functions. Each of the three types of PLD have AND and OR arrays that are used to implement logic in SOP form. What distinguishes them from each other is which arrays can be programmed by the user and which ones have permanent connections.

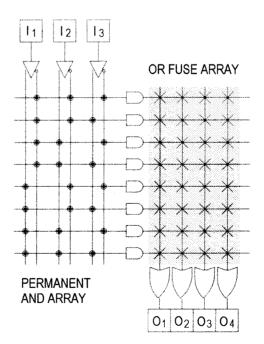

The PROM (see Fig. 2.1) has a fixed AND array that provides all of the possible input product terms. The OR array has fused connection points and can be programmed by the user. Any output in a PROM can be the sum of any or all of the outputs from the AND array. This arrangement is adequate for uses such as address decoders or data storage. SOP logic functions can also be implemented and sequential logic is a possibility, but external storage registers are needed. These uses for PROM's are rather inefficient, however. Every combination of inputs is available in the AND array in a PROM, but very rarely are all of these product terms used in a logic function. Therefore, much of the device resources go to waste. Also, since all product terms are available for a given number of inputs, each additional input doubles the number of terms in the AND array (# of terms =  $2^n$ , where n = # of inputs). This increases the physical size and complexity of the device and tends to put a practical limit on the number of inputs available.

Fig. 2.1 - Example of a PROM device

PLA devices (see Fig. 2.2) are the most flexible type of PLD. They have both AND and OR fuse arrays that may be programmed by the designer. The AND array resources are more limited than in PROM's and it is impossible to have every possible product term represented. This reduces the physical size of the device, but it forces the designer to perform some minimization of the design logic to be implemented. As in PROM's, any output can be the sum of any or all of the product terms in the AND array. This allows for product sharing in the outputs and can lead to more efficient use of device resources. However, while PLA devices are very flexible for design implementations, they are limited in speed due to the need for signals to propagate through two fuse arrays. Figure 2.3 shows an example of a PLA type of device that includes registers and feedbacks.

Fig. 2.2 - Example of a PLA device

Fig. 2.3 - Example of a PLA device (F105) with registers and feedback

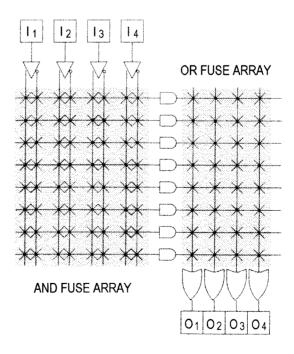

PAL devices (see Fig. 2.4) have fused AND arrays like in the PLA, but have fixed OR arrays. Generally, only one OR gate is assigned to each output pin. The product terms associated with one OR gate are not available to the other OR gates in the array, thus making product sharing all but impossible. In addition, a limited number of product terms are available in the AND array. Therefore, logic minimization is very

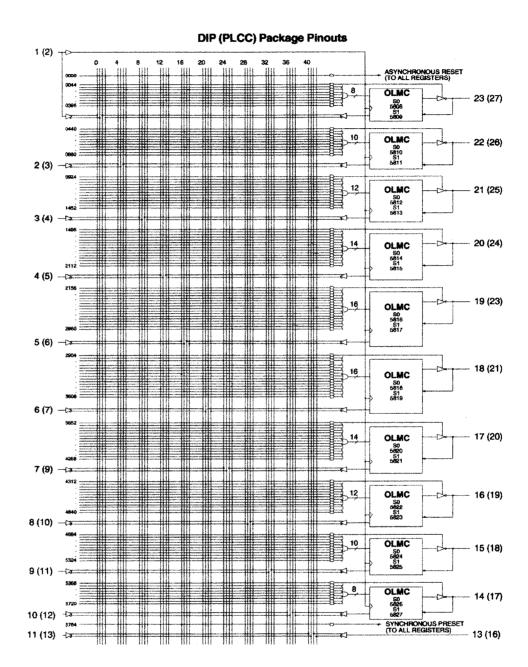

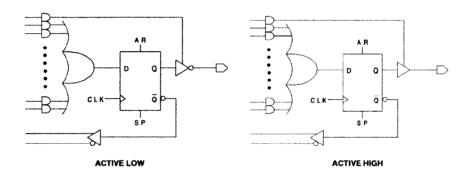

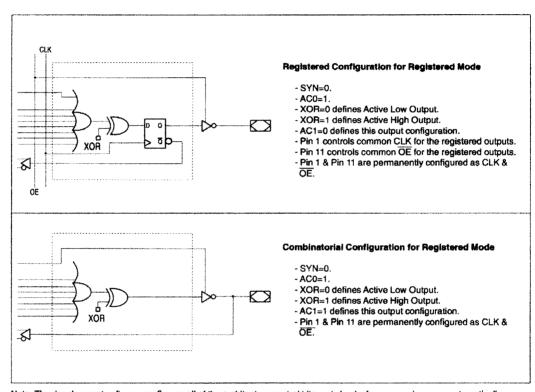

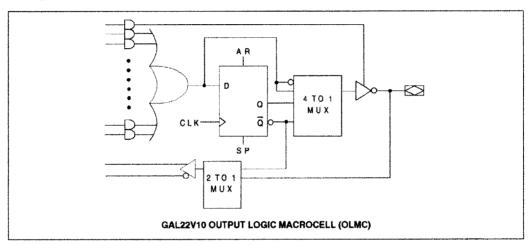

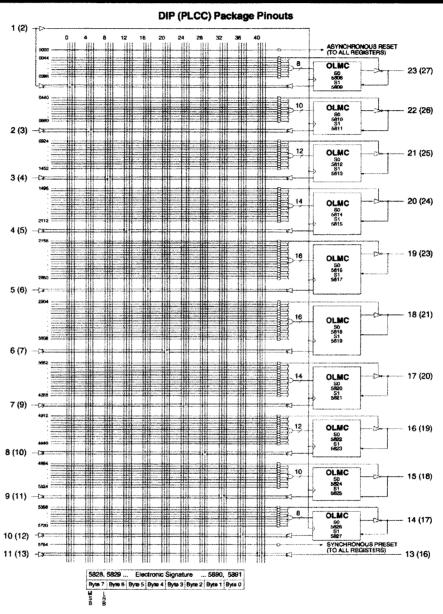

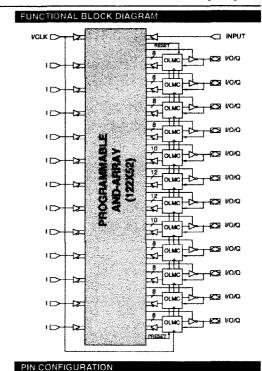

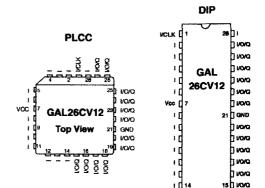

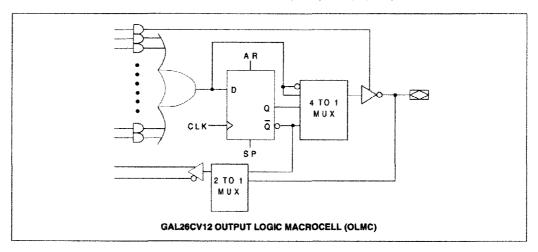

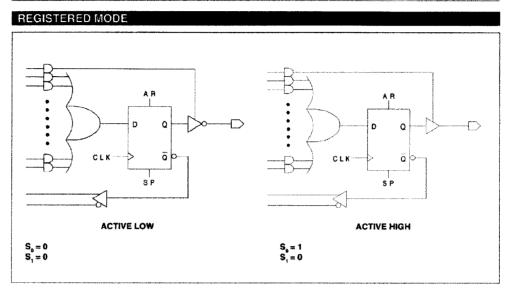

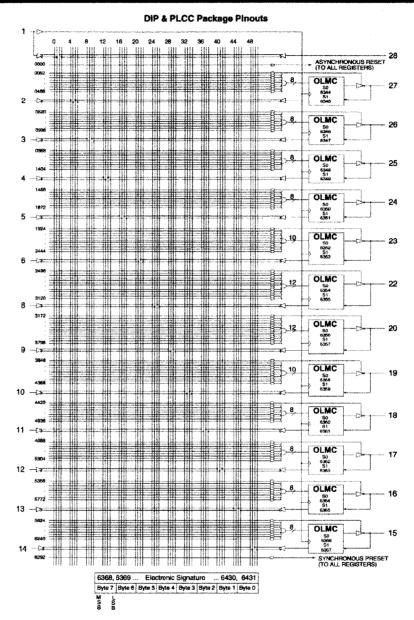

important when using PAL devices. These devices have a speed advantage over PLA's, though, since signals only need to propagate through one fuse array. Figure 2.5 shows an example of a combinatorial PAL. A example of a registered PAL is shown in Fig. 2.6. More advanced PAL devices feature output macrocells. These macrocells are configurable by the designer to form combinatorial or registered output configurations with programmable output polarities. These devices with macrocells are extremely flexible and can often directly replace many other types of PAL with just one device. An example of a macrocell-type PAL is shown in Fig. 2.7. The possible macrocell configurations for that device are depicted in Fig. 2.8.

Fig. 2.4 - Example of a PAL device

Fig. 2.5 - Example of a combinatorial PAL (P16L8)

Fig. 2.6 - Example of a registered PAL (P16R4)

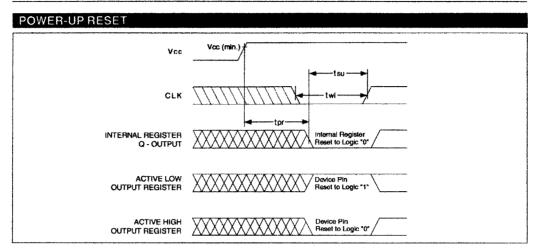

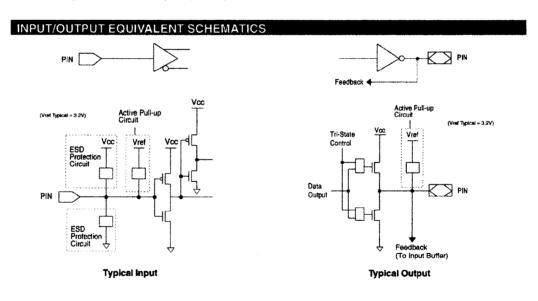

Fig. 2.7 - Example of a macrocell PAL device (GAL22V10)

# GAL22V10 OUTPUT LOGIC MACROCELL (OLMC)

# REGISTERED MODES

# COMBINATORIAL MODES

Fig. 2.8 - GAL22V10 macrocell configurations

This only scratches the surface of the number of PLD types that are available. Those readers who are interested in more information on which types of PLD's exist (including FPGA's) and the history of their development are referred to Practical Design Using Programmable Logic<sup>2</sup> by David Pellerin and Michael Holley. This book proved to be an invaluable resource to the author in preparing this paper. The Data I/O Logic Diagram Package<sup>4</sup> manual (a companion to the ABEL manuals) is also a good reference. It contains detailed schematics of over 200 PLD's.

## **CHAPTER III**

## AN OVERVIEW OF ABEL-HDL

## 3.1 - Program Features

ABEL-HDL is a powerful software package that allows the digital designer to implement designs in PLD's using familiar techniques such as Boolean equations, truth tables, and state diagrams. Using a text editor such as MS-DOS Edit or ABEL's built-in editor, the designer enters the description of the logic to be implemented. The description can be quite specific, even to the point of defining actual fuse assignments, if the end device for implementation is known. However, ABEL also allows the designer to describe the design logic in very generic terms without specifying an end device. ABEL then has the ability to determine (along with an optional set of criteria defined by the user) which devices are capable of implementing the design logic. A variety of logic minimization algorithms are built into the program and can be used to simplify the design logic. Extensive simulation capabilities exist in for determining the validity of the design logic at multiple stages of the ABEL design process. Finally, once the design logic has been "fitted" into a particular device, a fuse data file may be created for downloading to a device programmer unit.

The version of ABEL-HDL used by the author in this project is ABEL 4.10 (Version 4.03 was used initially, but was later upgraded to 4.10). It was released in 1991 or 1992 and runs under MS-DOS. The latest release is ABEL 6. It runs under Microsoft Windows and offers many graphical add-on utilities such as the StateCAD Graphical Design Entry program (allows graphical state diagram design entry) and Waveform

Viewer (allows simulation results to be displayed in familiar timing chart form). However, the same program structures and command syntaxes exist as in ABEL 4 for DOS. Therefore, the design examples depicted in this project are still valid. In fact, the DOS version of ABEL still exists under a new title: ABEL-PLD. Data I/O offers it as an entry-level means of programming PLD's. However, it is not capable of using the graphics utilities and other advanced features of ABEL 6.

## 3.2 - Command Syntax

ABEL uses a set of symbols for Boolean operators that is different from those introduced in classical digital design courses. These are used throughout this paper and in the design examples and are summarized in Table 3.1.

TABLE 3.1

ABEL BOOLEAN OPERATORS

| Symbol | Description   |

|--------|---------------|

| !      | NOT           |

| &      | AND           |

| #      | OR            |

| \$     | Exclusive OR  |

| !\$    | Exclusive NOR |

Assignment operators are used to assign values to an output. These are used when writing equations. Separate symbols are used for combinatorial or registered outputs. Using a registered assignment operator in describing the logic for an output indicates that the output will take on the evaluated value of that logic at the next clock cycle. Assignment operators are shown in Table 3.2.

TABLE 3.2

ABEL ASSIGNMENT OPERATORS

| Symbol | Description                     |

|--------|---------------------------------|

| =      | combinatorial output assignment |

| :=     | registered output assignment    |

Relational operators are used for comparing two items in an expression. They are primarily employed for conditional decision-making in state diagrams, but can also be used in equations. These are listed in Table 3.3. They are straight-forward except for the symbol for the 'equal' condition. The usage of two '=' symbols was necessary in order to differentiate the condition of 'equal' from the combinatorial assignment operator.

TABLE 3.3

ABEL RELATIONAL OPERATORS

| Symbol | Description           |  |

|--------|-----------------------|--|

| ==     | equal                 |  |

| !=     | not equal             |  |

| <      | less than             |  |

| <=     | less than or equal    |  |

| >      | greater than          |  |

| >=     | greater than or equal |  |

ABEL allows signals, either inputs or outputs, to be grouped into sets. This allows some simplification for the designer in writing the design logic. An example would be in the case of state variables. Say there are four state variables in the design, y1 through y4. If the design logic requires the comparing of state values, it would simplify things if the state variable were grouped into a set. For example:

State\_Value =

$$[y1,y2,y3,y4]$$

Then, instead of writing logic that compares the value of each state variable individually, the designer may compare the value of the set as a whole. For example:

ABEL also allows numeric values to be expressed in bases other than ten.

Base ten is assumed whenever a number is used. If the designer wishes to express a numeric value in a different base, a base operator prefix must be used. These are shown in Table 3.4.

TABLE 3.4

ABEL BASE OPERATOR PREFIXES

| Base System | Prefix    |

|-------------|-----------|

| binary      | ^b        |

| octal       | ^o        |

| decimal     | ^d        |

| hexadecimal | <b>^h</b> |

Using these base prefixes, the state value in the above example could also be expressed in another base, say binary:

These descriptions of command syntax that have been given are by no means exhaustive, but are sufficient for understanding the design examples to follow in this paper. If further syntax-related information is desired, the reader is referred to the ABEL User Manual.<sup>3</sup>

## 3.3 - Source File Structures

A digital logic design that is implemented in ABEL must conform to a standard file format. There are a number of required structures in an ABEL source file. However, there are also a number of optional items that the designer may include to simplify or clarify the design. A sample ABEL source file is shown in Fig. 3.1. It's part of the experimental circuit that will be discussed later. At the moment, it will serve to demonstrate the structures, both required and optional, of an ABEL file.

```

module

inputcon

'Input Conditioner, Tug-o-war Game'

title

declarations

inputcon device 'p16v8as';

CLK

pin 1;

P1 IN

pin 2;

P2_IN

pin 3;

Y1

pin 17;

¥2

pin 16;

YЗ

pin 15;

Y4

pin 14;

P1 OUT

pin 19;

P2_OUT

pin 18;

equations

Y1 = (P1_IN & Y1.pin) # (CLK & Y2.pin);

Y2 = (!CLK & P1_IN) # (P1_IN & Y2.pin) # (CLK & Y2.pin);

P1_OUT = (P1_IN & !Y2.pin) # (!CLK & P1_IN & !Y1.pin);

Y3 = (P2 \text{ IN & } Y3.pin) \# (CLK & Y4.pin);

Y4 = (!CLK & P2_IN) # (P2_IN & Y4.pin) # (CLK & Y4.pin);

P2 OUT = (P2 IN & !Y4.pin) # (!CLK & P2 IN & !Y3.pin);

test vectors

'Pulse catcher for P1'

( [ CLK, P1 IN ] -> [ P1_OUT ] )

[ 0,

0 ] -> [ 0 ];

Ο,

1 ] -> [ 1 ];

1,

1

] -> [ 0 ];

1,

1 ] -> [0];

1 ] -> [ 0 ];

ο,

] -> [ 0 ];

Ο,

1

1,

1

] -> [ 0 ];

0

1,

0 ] -> [0];

Ο,

Ο,

1,

0 ] -> [ 0 ];

] -> [ 1 ];

] -> [ 1 ];

1,

Ο,

1

Ο,

1 ] -> [ 1 ];

1 ] -> [ 0 ];

1 ] -> [ 0 ];

1,

1,

Ο,

1 ] -> [ 0 ];

ο,

0 ] -> [ 0 ];

1.

end

```

Fig. 3.1 - Sample ABEL logic design source file

The first few lines at the top of the file form a Header. The Header is a required structure, but includes optional elements as well. The 'module' statement is required. It defines the beginning of the source file and gives the module a name. In this example, the module name is 'inputcon'. An optional title may be given to the module. It

is indicated with the 'title' statement. This statement is not acted on by the ABEL compiler, but it does allow the title to show up in the documentation produced by ABEL.

Next comes the Declarations structure. This area of the file is reserved for indicating details such as device type, signal-to-pin assignments, signal attributes, and user-defined constants and sets. The 'declarations' statement is not a required element. ABEL assumes that any statements following the Header and preceding the Logic Structure(s) (equations, truth\_table, and state\_diagram) are indeed declarations. In this example, the 'device' statement is used to declare the PLD intended to be used and the 'pin' statement is used to declare signal-to-pin assignments. If a generic approach is being taken in the design process, the device line and the pin numbers may be eliminated. ABEL can be made to find devices that the module will 'fit' into and automatically assign pin numbers to the defined input/output signals.

Following the Declarations are the Logic Structures. These portions of the source file define the design logic. The descriptions may be equations, truth tables, or state diagrams. At least one of these Logic Structures are required in a module, but it's also valid in many situations to have more than one type in the same source file. A Logic Structure begins with a required keyword. These keywords are 'equations', 'truth\_table', and 'state diagram'. The Logic Structure used in the example source file is equations.

After the Logic Structures, the designer may include a set of Test Vectors. This structure is optional, but it is highly advisable that it be used. It allows the designer to verify that the design logic functions as intended. This structure begins with the 'test\_vectors' keyword. The designer then writes a set of vectors that tell ABEL how particular outputs behave when subjected to certain input stimuli. Using these test vectors, it is possible to describe all of the functional behavior of the design logic. Once the ABEL source file has been compiled, the resulting compiled logic may be simulated through the use of the test vectors. The input portion of the vectors are used to stimulate the compiled logic and the results are compared to the output portion of the vectors.

ABEL alerts the designer to any discrepancies between the expected output values and the values determined by the simulation. This is a great aid to the designer in debugging a logic design.

Finally, the module is terminated with the 'end' keyword. This is a required structure. It's optional for the module name to follow the 'end' keyword, but it's rarely used in practice.

## 3.4 - ABEL Design Flow

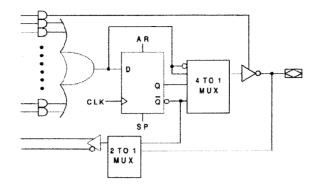

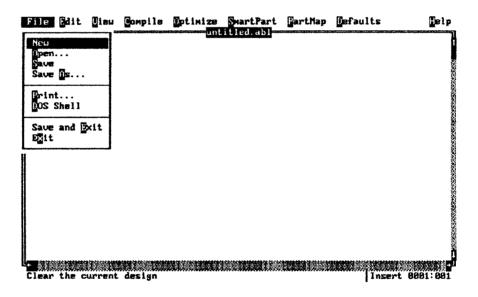

All processing of an ABEL source file takes place in the ABEL Design Environment. Upon typing 'ABEL4' at the DOS prompt, the ABEL Design Environment screen appears. A sample screen is shown in Fig. 3.2.

Fig. 3.2 - A sample ABEL Design Environment screen

The ABEL source file may be created in the built-in screen editor or created externally. Either way, once it is loaded into the ABEL Design Environment, it then may be compiled via commands in the 'Compile' pull-down menu. If the source file includes test vectors, they then may be simulated (also from the 'Compile' menu). If errors occur

in the compilation or simulation processes, they may be seen using commands from the 'View' menu. The 'View' menu also allows the designer to view documentation produced by other ABEL processes.

Having been compiled, the source file then is optimized. There are a number of logic minimization options available in the 'Optimize' menu. The optimized source file may then be simulated (also in the 'Optimize' menu).

The optimized file is then 'fitted' into a device. This is accomplished from the 'SmartPart' menu. If the design is generic in nature, the Device Database may be searched for PLD's in which the design is capable of being implemented. If a device-specific design is being used, the device is already known. Either way, the source file may be fitted into the device and the results simulated. The signal-to-pin assignments may also be calculated by ABEL at this time, if they have not already been assigned in the source file.

Once the source file is fitted into a device, a JEDEC fuse file is created. The options for doing this are found in the 'PartMap' menu. This fuse file may then also be simulated. The resulting <filename>.jed file should then be copied onto a 3-1/2" disk to be read by the Unisite programmer. This JEDEC file contains the actual fuse data for the physical process of programming the PLD with the design logic.

The above directions are meant to be only an introduction into the ABEL design process. For further information, the reader is again referred to the ABEL User Manual.<sup>3</sup>

#### **CHAPTER IV**

### ORIGINAL EXPERIMENTAL DESIGN IMPLEMENTATION

## 4.1 - Design Concept

The ABEL design examples that will be discussed are derived from a digital circuit designed and built by the author in a graduate digital logic design course during the summer of 1992. 7400-series devices were used in the design implementation. Every effort was made to limit the total chip count, but in spite of these efforts, the final tally came to 31 chips.

The circuit was designed to be a 'Tug of War' game. The concept is depicted in Fig. 4.1. The 'rope' consisted of nine red LED's arranged in a row. A lit LED indicated the 'knot' position on the rope. A green LED on either end of the rope indicated the respective winner of the game. A game was started by pressing the RESET button. A time delay of about 1.5 seconds occurred and then a piezo buzzer sounded to signal both players to begin pushing their respective buttons. They would continue to push their buttons until the knot was 'pulled' to their respective winner LED. The piezo buzzer would then sound three times to indicate that a win condition occurred. The game then waited in this state until the RESET button was pressed again and another game would start. In addition, there were two more features. First, all LED's would be lit at power up to test that they were functioning. Also, if a player would push his button prior to the 'GO' signal from the buzzer, it was considered cheating and the other player would automatically win. The final circuit was tested and functioned as intended.

A block diagram of the system design is shown in Fig. 4.2. The system consisted of four main circuits: the Game Controller, Output Controller, Timing Controller, and Input Conditioner.

Fig. 4.1 - Tug of War game concept

Fig. 4.2 - Block diagram of original system design implementation

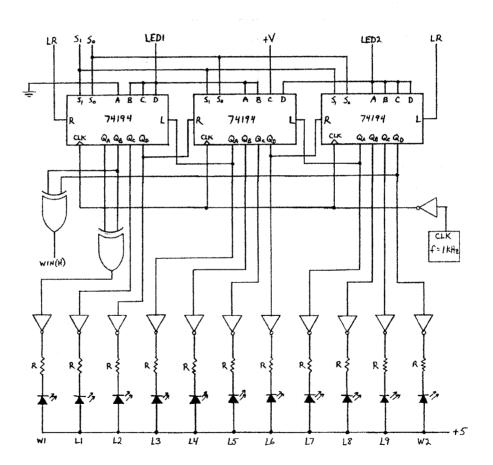

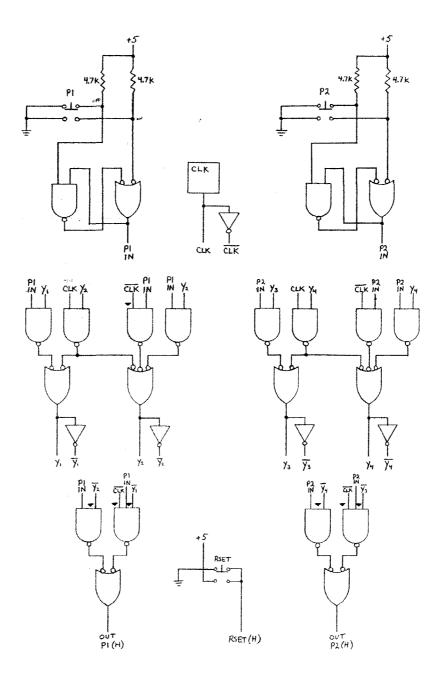

## 4.2 - Game Controller

The Game Controller managed all of the game rules and course of play. It would issue signals to the Output Controller shift registers to dictate LED 'movement' and to the Timing Controller to indicate that a time delay or a winner signal should be started. Communications with the Output Controller were handled synchronously. However, because the Timing Controller operated at a much slower clock frequency than the Game Controller, communications with it were accomplished through asynchronous handshaking. The Game Controller design itself was implemented as a Moore-type sequential circuit. The state diagram is shown in Fig. 4.3 and the circuit schematic is depicted in Fig. 4.4. It may also be interesting to note that the 7400-series circuit seen in Fig. 1.1 is the actual original Game Controller circuit.

Fig. 4.3 - State diagram of Game Controller circuit

Fig. 4.4 - Schematic of original Game Controller design

# 4.3 - Output Controller

The Output Controller was in charge of controlling the status of the LED's and alerting the Game Controller when a win condition had occurred. The circuit (see Fig. 4.5) was composed primarily of three 4-bit universal shift registers connected in series.

The LED signals came directly from the shift register outputs. The shift and broadside

load signals and data bits came from the Game Controller. In order to get win status information back to the Game Controller in a synchronous manner, the shift registers were made to clock on the falling edge of the system clock pulse (note inverter on clock signal). This ensured that no signal lag occurred.

Fig. 4.5 - Schematic for original Output Controller circuit

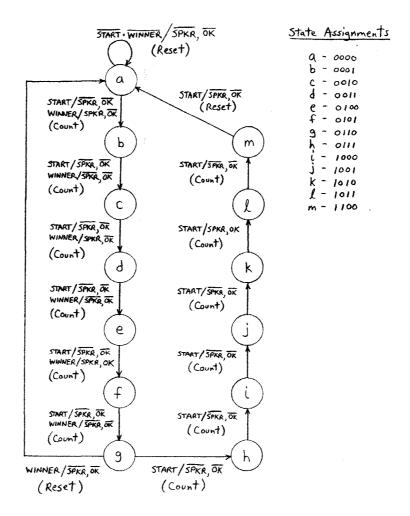

## 4.4 - Timing Controller

The Timing Controller took care of all timing routine and sound effect duties. The circuit was built around a 4-bit binary counter clocked at a very slow pace (approximately 5-10 Hz). This difference in clock speeds (the system clock frequency was set to about 1-5 kHz) mandated that the timing functions be relegated to a separate circuit and that communications between it and the Game Controller be asynchronous in nature. The Timing Controller design was implemented as a Mealy-type synchronous circuit, using the counter outputs as state registers. The state diagram is shown in Fig. 4.6 and the circuit schematic is depicted in Fig. 4.7.

Fig. 4.6 - State diagram for original Timing Controller design

Fig. 4.7 - Schematic of original Timing Controller circuit

The 7493 4-bit counter counts when its control inputs (R1 and R2) are held low and asynchronously resets the count outputs to zero when the control inputs are high. This feature was used in the design to enable the START time delay to be interrupted upon a player cheating. The counter would then immediately (i.e. asynchronously) reset to state 'a' and the WINNER routine could be performed.

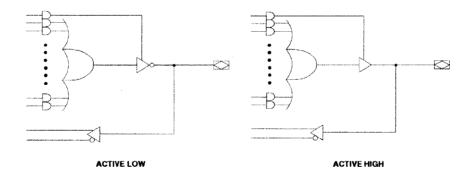

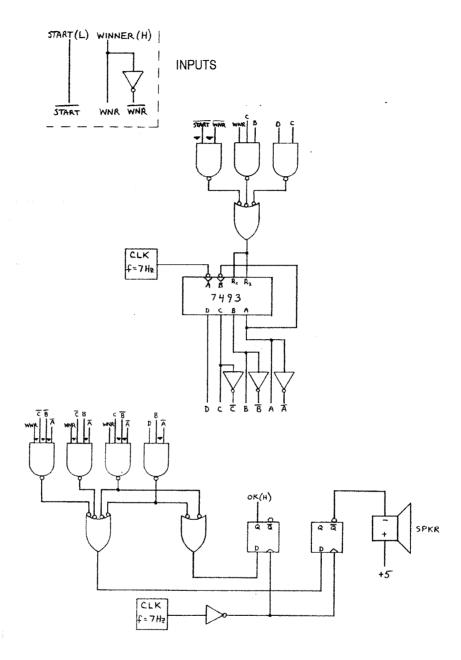

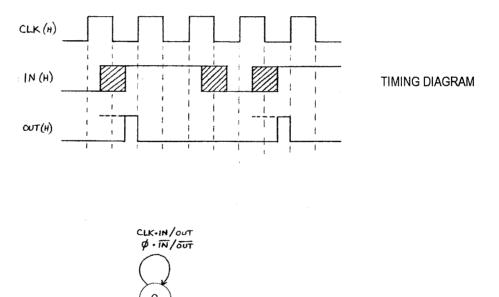

# 4.5 - Input Conditioner

The Input Conditioner was needed due to the asynchronous nature of the signals from the player pushbuttons. The pulses from the pushbuttons needed to be captured and synchronized with the system clock so that they could be serviced by the Game Controller. It was also desired that the pulses be turned into one-shots in order to prevent a player from being lazy and simply hold his button down. These conditions made it a logical choice to implement the design as an asynchronous sequential circuit that had the system clock signal as one of its inputs. Some cross-coupled NAND's and pull-up resistors were also employed to debounce the pushbuttons. The timing and state diagrams are shown in Fig. 4.8 and the circuit schematic in Fig. 4.9.

Fig. 4.8 - Timing and state diagrams for original Input Conditioner circuit

CLK . IN/OUT

CLK . IN / OUT

CIK. IN /OUT

CLK. Ø/OUT

CLK · IN/OUT

STATE DIAGRAM

Fig. 4.9 - Schematic of original Input Conditioner circuit

#### **CHAPTER V**

#### ABEL EXPERIMENTAL DESIGN IMPLEMENTATION

### 5.1 - Design Concept

The main objective for the ABEL implementation of the Tug of War game circuit was to maintain the functionality of the original circuit while only using one PLD for each of the four system components (i.e. Game Controller, Output Controller, Timing Controller, and Input Conditioner). Two deviations from this plan were made, however. First, it was necessary to make some changes in the signals between the Game Controller and the Output Controller. This was due to device limitations and will be discussed in more detail. Secondly, the decision was made to separate the debouncing circuitry from the Input Conditioner and the LED output inverters from the Output Controller. The reasoning for this was to isolate the logic portions (i.e. the PLD's) from the input/output circuits and protect them from any possible harm. Quad NAND and hex inverter chips are cheap and plentiful and can be replaced easily if damaged. PLD's are more expensive and generally are not stocked at consumer electronics stores, necessitating ordering from catalogs.

ABEL 4, being DOS-based, only supports up to eight character length filenames. Therefore, the filenames (and module names) for the Game Controller, Output Controller, Timing Controller, and Input Conditioner became GAMECON, OUTCON, TIMECON, and INPUTCON, respectively.

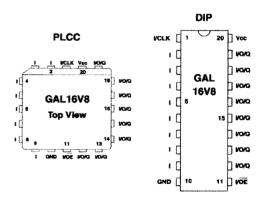

Macrocell-type PAL devices were used for all four of the system components.

This resulted in great flexibility in terms of the availability of equivalent device architectures because of the configurable nature of the macrocells. In particular GAL

devices from Lattice Semiconductor Corporation were used. These are CMOS devices and are electrically erasable and reprogrammable. This feature reduced the number of chips needed for experimentation since they could be reused if the logic programmed into them did not function as intended. Manufacturer data sheets for these devices are included in Appendix B.

#### 5.2 - GAMECON

The GAMECON module (see Fig. 5.1) was programmed as a Moore-type sequential circuit just as the original Game Controller had been designed. The state assignments and state transitions remain true to the original design specifications. Three separate modifications were made to the input/output signals, though. The LED1 and LED2 outputs from the original circuit were combined into one named LED. LED1 and LED2 are identical logically and were only separated in the first place because of fanout concerns. These concerns don't exist inside the PLD. Secondly, the WIN input to the original circuit was eliminated and both W1 and W2 from the Output Controller were brought in instead. Therefore, the win status determination would be made in the logic of the GAMECON module rather than in the OUTCON module. This was done because of resource restrictions in the device used for the OUTCON design that will be explained later. Finally, an output named CLOCK was created. This signal consists only of an inversion of the CLK input. It was also necessary for use in the OUTCON design for reasons that will be explained later.

There are a number of items in the GAMECON file that need to be introduced. First, in the Declarations section, the reader will notice the use of the 'istype' statement. This statement is used to tell ABEL what type of attribute should be assigned to a given output. For example, S1 is defined to have the output attribute of a 'buffer' (i.e. positive logic). Register output attributes were assigned to y1 through y4. If this had not been

```

Module

gamecon

Title

'Game Controller, Tug-o-war Game'

Declarations

gamecon device 'p26cv12';

CLK

pin 1;

pin 2;

P1

P2

pin 3;

RSET

pin 4;

pin 8;

OK

W1

pin 9;

pin 10;

W2

S1

pin 27 istype 'buffer';

pin 26 istype 'buffer';

S0

WINNER

pin 17 istype 'buffer';

pin 18 istype 'buffer';

START

pin 25 istype 'buffer';

LR

pin 24 istype 'buffer';

LED

pin 23,22,20,19 istype 'reg';

y1,y2,y3,y4

CLOCK

pin 16 istype 'buffer';

Stval = [y1, y2, y3, y4];

a = [0,0,0,0];

b = [0,1,0,0];

c = [0,1,0,1];

d = [1,1,0,1];

e = [0,1,1,1];

f = [1,1,1,1];

g = [1,1,1,0];

h = [1,1,0,0];

i = [0,1,1,0];

Equations

Stval.clk = CLK;

CLOCK = !CLK;

State Diagram Stval

state a: S1 = 1;

s0 = 1;

LED = 1;

If RSET then b else a;

state b: S1 = 1;

s0 = 1;

LED = 0;

START = 1;

If (P1 & !P2) then h

Else

If (!P1 & P2) then i

Else

If OK then c

Else b;

state c: S1 = 0;

SO = 0;

If (P1 & !P2) then d

Else

If (!P1 & P2) then e

Else

If RSET then b

Else c;

```

Fig. 5.1 - GAMECON source file

```

state d: S1 = 1;

50 = 0;

LR = 0;

If W1 then f else c;

state e: S1 = 0;

s0 = 1;

LR = 0;

If W2 then f else c;

state f: S1 = 0;

50 = 0;

WINNER = 1;

If OK then g else f;

state g: S1 = 0;

S0 = 0:

If RSET then b else g;

state h: S1 = 1;

s0 = 0;

LR = 1;

Goto f:

state i: S1 = 0;

S0 = 1:

LR = 1;

Goto f;

Test vectors 'Test !CLOCK'

( [ CTK ] -> [ CTOCK ] )

1 ];

0 ];

[ 0 ] -> [

[ 1 ] -> [

Test vectors 'power-up and reset/start routine'

( [CLK, P1,P2,RSET,OK ] \rightarrow [ Stval,S1,S0,LED,START ] )

a , 1, 1, 1 , 0 ];

a , 1, 1, 1 , 0 ];

[.c.,.x.,.x., 0 ,.x.] -> [

[.c.,.x.,.x., 0 ,.x.] -> [

b, 1, 1, 0, 1 ];

b, 1, 1, 0, 1 ];

c, 0, 0, .x., 0 ];

[.c.,.x.,.x., 1 ,.x.] -> [

[.c., 0 , 0 ,.x., 0 ] -> [

[.c., 0 , 0 ,.x., 1 ] -> [

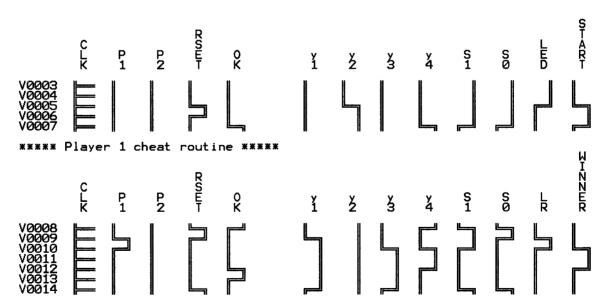

Test vectors 'Player 1 cheat routine'

( [ CLK, P1,P2,RSET,OK ] \rightarrow [ Stval,S1,S0,LR,WINNER ] )

[ .c., 0 , 0, 1 ,.x.] -> [ b , 1, 1,.x., 0 [ .c., 1 , 0, .x., x.] -> [ h , 1, 0, 1 , 0

1;

1;

[.c.,.x.,.x.,.x.,.x.] \rightarrow [

f , 0, 0,.x., 1

];

f, 0, 0, x., 1

g, 0, 0, x., 0

g. 0 0, x., 0

[.c.,.x.,.x.,.x.,0] \rightarrow [

1:

[.c.,.x.,.x.,.x., 1] \rightarrow [

];

g, 0, 0, x, 0

b, 1, 1, x, 0

[ .c.,.x.,.x., 0 ,.x.] -> [

];

[.c.,.x.,.x., 1,.x.] \rightarrow [

Test vectors 'Player 2 cheat routine'

( [ CLK, P1, P2, RSET, OK ] -> [ Stval, S1, S0, LR, WINNER ] )

[ .c., 0 , 0, .x., 0 ] \rightarrow [ b , 1, 1, .x., 0 ];

i , 0, 1, 1 , 0

f , 0, 0, x., 1

[ .c., 0, 1, .x., .x.] \rightarrow [

1;

[.c.,.x.,.x.,.x.] \rightarrow [

1;

g , 0, 0, x., 0

[ .c.,.x.,.x., 1 ] -> [

];

[.c.,.x.,.x., 1,.x.] \rightarrow [b, 1, 1,.x., 0]

1;

```

Fig. 5.1 (cont'd.) - GAMECON source file

```

Test vectors 'Normal competition'

( [ CLK, P1, P2, RSET, OK, W1, W2 ] -> [ Stval, S1, S0, LR ] )

[ .c., 0 , 0, .x., 1 ,.x.,.x.] \rightarrow [ c , 0, 0,.x.];

[ .c., 0 , 0, 0 ,.x.,.x.,.x.] -> [ .c., 0 , 0, 1 ,.x.,.x.,.x.] -> [

c , 0, 0,.x.];

b , 1, 1, .x.];

c , 0, 0,.x.];

[ .c., 0 , 0, .x., 1 ,.x.,.x.] \rightarrow [

, 0, 0,.x.];

.c., 1 , 1, 0 ,.x.,.x.,.x.] -> [

С

.c., 1 , 0, .x.,.x.,.x.,.x.] -> [

d

, 0, 0,.x.];

[.c.,.x.,.x.,.x.,0,0] \rightarrow [

C

, 0, 1, 0 ];

.c., 0 , 1 , x., x., x., x. x.] \rightarrow [

е

.c., .x., .x., .x., .x., 0, 0] \rightarrow [

[ .c., 1 , 0 , x., x., x., x.] -> [

đ

[.c.,.x.,.x.,.x.,1,0] \rightarrow [

£

, 0, 0, x.1;

[.c.,.x.,.x.,.x., 1,.x.,.x.] \rightarrow [

α

[.c.,.x.,.x., 1,.x.,.x.,.x.] \rightarrow [

, 0, 0,.x.];

[ .c., 0 , 0 ,.x., 1 ,.x.,.x.] -> [

, 0, 1, 0 ];

[ .c., 0 , 1 ,.x.,.x.,.x.,.x.] -> [

е

[\ .c.,.x.,.x.,.x.,.x.,\ 0\ ,\ 1\ ]\ ->\ [

end

```

Fig. 5.1 (cont'd.) - GAMECON source file

done, ABEL may have assumed y1 through y4 to be combinatorial outputs. Also, in the Declarations section, notice the use of a set named 'Stval' that includes all four of the state variables. Below that is a list of defined set constants 'a' through 'i' that cover all of the state values in the circuit. The set and set constants were useful in simplifying the writing of the state diagram section of the source file.

Secondly, in the Equations section, the reader will notice the use of a 'dot extension' in describing the clock source for the 'Stval' registers. Dot extensions are used to accurately describe register and feedback signals and clear up any potential ambiguities. For example, the registers used for 'Stval' have attributes such as register input (.D), register output (.Q), register clock input (.clk), asynchronous reset (.AR), synchronous preset (.SP), etc. Without specifying a dot extension for 'Stval' in an equation involving it, ABEL would be clueless in many cases as to which part of the registers it should be addressing with that equation.

Next, the reader is for the first time introduced to an example of a State\_Diagram structure. Immediately following the State\_Diagram keyword are the state variables for the state diagram. In this case, the set 'Stval' is used as a shortcut. The set constants that were defined previously are also used in the individual state definitions in

the state diagram. It's also interesting to note that the syntax for the branching logic is strikingly similar to BASIC or FORTRAN.

Lastly, the Test\_Vectors section deserves some attention. When writing test vectors to simulate the actions of a state machine, it is necessary to write them such that the simulation begins in the power-up or initial state. The following vectors should then step the state machine through its states just as the normal operational flow will occur. It is not possible to skip states while doing this. At this time, also note the use of the special constants '.c.' (clocked input; low-high-low) and '.x.' (don't care) in the vectors.

ABEL generates reports at every step of the design process. These include simulation results, compiled equations, device resource allocations, etc. These are included for GAMECON and the other system component designs in Appendix A.

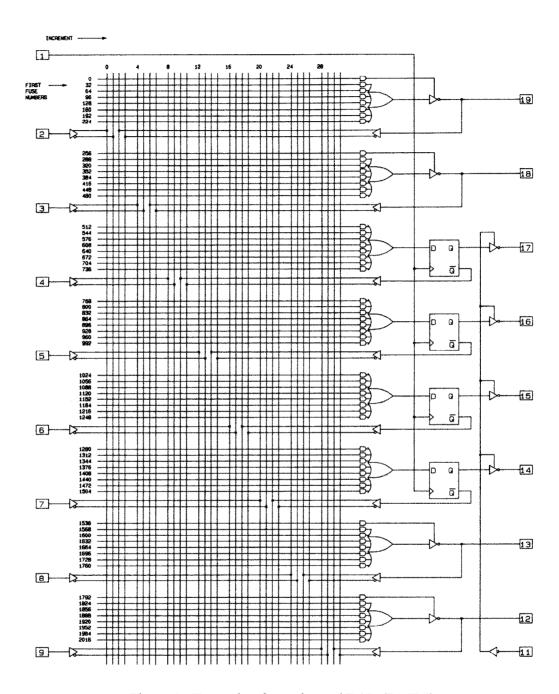

### **5.3 - OUTCON**

In programming the OUTCON module (see Fig. 5.2), a different approach was taken. Since this was not a state machine, the state diagram method of description was of no use. In addition, a truth table description would be highly impractical. The only recourse was to use equations to describe the design logic.

A couple of set definitions were made in the Declarations section that are worth noting prior to discussing the equations. First, the two shift register control signals were put in a set named 'Select'. Second, all of the LED outputs were grouped into a set named 'OutLED'. The 'OutLED' set was created to simplify the equations that had to do with broadside load conditions since all of the LED outputs could be set properly in the same equation.

Also of note in the Declarations section is the CLOCK input signal. This signal is the inverted system clock pulse output from the GAMECON module. Referring back to the original Output Controller design, the shift registers needed to be clocked on the

```

Module

Outcon

Title

'Output Controller, Tug-o-war Game'

Declarations

Outcon device 'P26CV12';

CLOCK

pin 1;

pin 2,3;

S1,S0

pin 4;

LR

LED

pin 5;

W1,L1,L2,L3,L4,L5,L6,L7,L8,L9,W2

pin 27,26,25,24,23,22,20,19,18,17,16 istype

'buffer';

Select = [S1,S0];

OutLED = [W1,L1..L9,W2];

Equations

OutLED.CLK = CLOCK:

When (Select = 0) then OutLED := OutLED.fb;

When (Select = 1) & (LR = 0) then W2 := L9.fb;

When (Select = 1) & (LR = 0) then L9 := L8.fb;

When (Select = 1) & (LR = 0) then L8 := L7.fb;

When (Select == 1) & (LR == 0) then L7 := L6.fb;

When (Select = 1) & (LR = 0) then L6 := L5.fb;

When (Select == 1) & (LR == 0) then L5 := L4.fb;

When (Select == 1) & (LR == 0) then L4 := L3.fb;

When (Select = 1) & (LR = 0) then L3 := L2.fb;

When (Select = 1) & (LR = 0) then L2 := L1.fb;

When (Select = 1) & (LR = 0) then L1 := W1.fb;

When (Select = 1) & (LR = 0) then W1 := 0;

When (Select = 2) & (LR = 0) then W1 := L1.fb;

When (Select = 2) & (LR = 0) then L1 := L2.fb;

When (Select = 2) & (LR = 0) then L2 := L3.fb;

When (Select = 2) & (LR = 0) then L3 := L4.fb;

When (Select = 2) & (LR = 0) then L4 := L5.fb;

When (Select = 2) & (LR = 0) then L5 := L6.fb;

When (Select = 2) & (LR = 0) then L6 := L7.fb;

When (Select = 2) & (LR = 0) then L7 := L8.fb;

When (Select = 2) & (LR = 0) then L8 := L9.fb;

When (Select \Longrightarrow 2) & (LR \Longrightarrow 0) then L9 := W2.fb;

When (Select == 2) & (LR == 0) then W2 := 0;

When (Select = 1) & (LR = 1) then OutLED := [1,0,0,0,0,0,1,0,0,0,0];

When (Select = 2) & (LR = 1) then OutLED := [0,0,0,0,1,0,0,0,0,1];

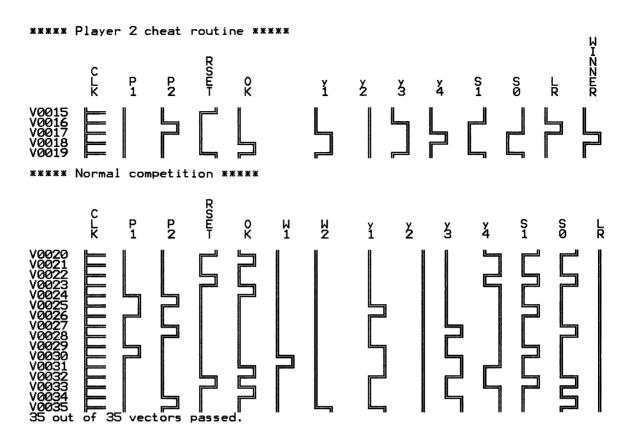

Test vectors

'Broadside load and hold operation'

( [CLOCK,S1,S0, LR,LED] -> [ W1,L1,L2,L3,L4,L5,L6,L7,L8,L9,W2 ] )

[ .C. , 1, 1, .X., 1 ] -> [ 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1];

[ .C. , 0, 0, .X., 1 ] -> [ 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1];

[.C., 1, 1, x, 0] \rightarrow [0, 0, 0, 0, 0, 1, 0, 0, 0, 0];

```

Fig. 5.2 - OUTCON source file

falling-edge of the system clock pulse in order to return the win status results to the Game Controller by the next rising-edge of the clock. Unfortunately, the GAL26CV12 (and most PLD's for that matter) does not allow signal inversion on the signal lines leading to the clock inputs on the registers. This necessitated feeding the clock input pin on the

```

Test vectors

'Shift zeros right and then left'

( [CLOCK, S1, S0, LR, LED] -> [ W1, L1, L2, L3, L4, L5, L6, L7, L8, L9, W2 ] )

[ .C. , 1, 1, .x., 0 ] -> [ 0, 0, 0, 0, 0, 1, 0, 0, 0, 0, 0

[ .C. , 0, 1, 0 , .x.] -> [ 0, 0, 0, 0, 0, 0, 1, 0, 0, 0, 0

[ .C. , 0, 1, 0 ,.X.] -> [ 0, 0, 0, 0, 0, 0, 0, 1, 0, 0, 0];

[ .C. , 0, 1, 0 ,.X.] -> [

0, 0, 0, 0, 0, 0, 0, 0, 1, 0, 0 ];

[ .C. , 0, 1, 0 ,.x.] -> [

0, 0, 0, 0, 0, 0, 0, 0, 1, 0

[ .C. , 0, 1, 0 ,.X.] -> [

0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1];

[ .C. , 1, 0, 0 ,.X.] -> [

0, 0, 0, 0, 0, 0, 0, 0, 0,

[ .C. , 1, 0, 0 , x.] -> [

0, 0, 0, 0, 0, 0, 0, 0, 1, 0,

[ .C. , 1, 0, 0 ,.X.] -> [

0, 0, 0, 0, 0, 0, 0, 1, 0, 0, 0 ];

[ .C. , 1, 0, 0 , x.] -> [

0, 0, 0, 0, 0, 0, 1, 0, 0,

[ .C. , 1, 0, 0 ,.X.] -> [

0, 0, 0, 0, 0, 1,

0, 0, 0, 0,

[ .C. , 1, 0, 0 ,.X.] -> [

0, 0, 0, 0, 1, 0, 0, 0, 0, 0, 0

[ .C. , 1, 0, 0 ,.x.] -> [

0, 0, 0, 1, 0, 0, 0, 0, 0,

[ .C. , 1, 0, 0 ,.X.] -> [

0, 0, 1, 0, 0, 0, 0, 0, 0, 0,

[.c., 1, 0, 0, .x.] \rightarrow [ 0, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0];

[.C., 1, 0, 0, .X.] \rightarrow [ 1, 0, 0, 0, 0, 0, 0, 0, 0, 0];

Test vectors

'Shift 1 left'

( [CLOCK, S1, S0, LR, LED] -> [ W1, L1, L2, L3, L4, L5, L6, L7, L8, L9, W2 ] )

[ .c. , 1, 1, x., 0 ] \rightarrow [ 0, 0, 0, 0, 0, 1, 0, 0, 0, 0];

[.C., 1, 0, 1, .X.] \rightarrow [0, 0, 0, 0, 1, 0, 0, 0, 0, 1];

'Shift 1 right'

Test vectors

( [CLOCK, S1, S0, LR, LED] -> [ W1, L1, L2, L3, L4, L5, L6, L7, L8, L9, W2 ] )

[.c., 1, 1,.x., 0] -> [ 0, 0, 0, 0, 0, 1, 0, 0, 0, 0];

[.C., 0, 1, 1,.X.] \rightarrow [ 1, 0, 0, 0, 0, 0, 1, 0, 0, 0];

End

```

Fig. 5.2 (cont'd.) - OUTCON source file

26CV12 with the defined CLOCK output from the GAMECON device in order to simulate a falling-edge clock trigger.

The Equations section includes a rather large number of equations. Since ABEL doesn't have a mathematical or logical operator for shifting bits in a defined set such as 'OutLED', it was necessary to write an equation for each LED output in the set for both the left and right shift operations. This was a rather inelegant, brute-force method of accomplishing shift operations, but it worked. On a side note, the '.fb' dot extension probably was not necessary in the LED outputs. The use of the registered assignment operator in the equations probably should have indicated to ABEL that the LED signals involved in the equation logic were registered feedbacks (it never hurts to be prepared, though).

With regards to the previously mentioned elimination of the WIN output and subsequent usage of both W1 and W2 as signals back to GAMECON, this was not the intent in the first attempt at the OUTCON module design. WIN had been defined as an output of OUTCON and used the same logic as in the Output Controller design:

$$WIN = W1 \$ W2$$

However, while attempting to 'fit' the OUTCON module into the 26CV12 device, ABEL indicated that this logic could not be assigned due to the fact that the 26CV12 has no resources available for exclusive-OR functions. The logical alternative would have been to use the SOP equivalent of the equation:

$$WIN = (W1 \& !W2) # (!W1 \& W2)$$

Unfortunately, adding this equation to the design logic resulted in a "too many feedbacks used" error message for the W1 and W2 outputs. This was due to feedback resource limitations in the 26CV12 device. In the end, the W1 and W2 outputs were each routed to the GAMECON module as inputs and both designs interacted fine.

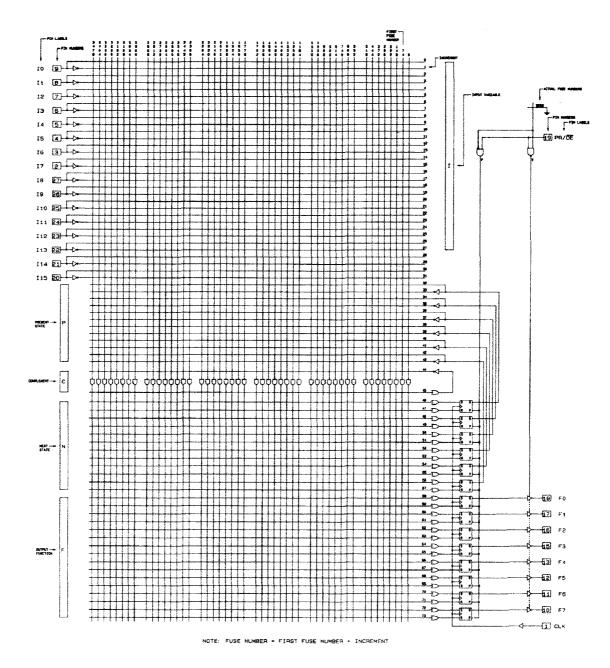

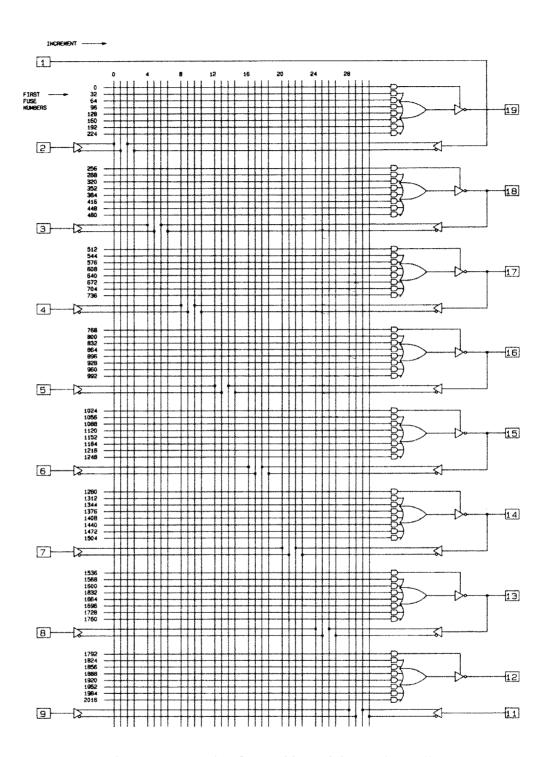

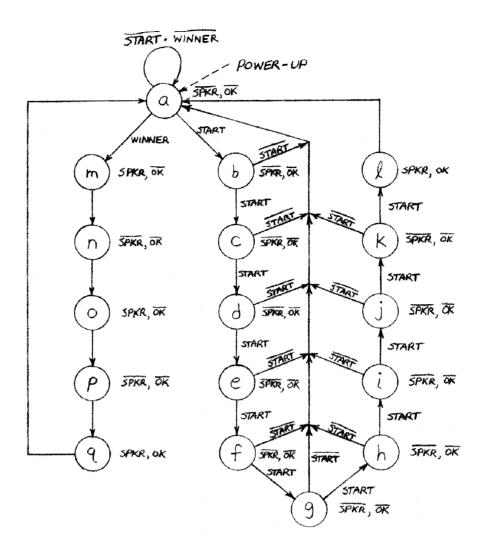

## 5.4 - TIMECON

The design for the TIMECON module differs from the original Timing Controller design, yet the functionality remains the same. TIMECON is implemented as a Moore-type sequential design (see Fig. 5.3), whereas the Timing Controller was a Mealy-type design. The decision to use a Mealy implementation in the Timing Controller was forced by the fact that the 4-bit binary counter used as state variables could not be branched. States could only be sequenced in numerical order. This necessitated the

Fig. 5.3 - TIMECON state diagram

sharing of states for differing output conditions, thus a Mealy design was needed. This constraint does not exist in PLD's, so more flexibility was available in the design for TIMECON. Using a Moore design enabled the START and WINNER routines to be separated, thus eliminating the need for an asynchronous reset of the registers upon an interruption of the START time delay routine (i.e. when a player cheats) as was used in the Timing Controller design. In the TIMECON design, when an START routine interruption occurred, the next state transition was a synchronous one to state 'a'. This situation made it much easier to write test vectors that accurately described the behavior of the design. The ABEL source file for TIMECON is shown in Fig. 5.4.

```

Module

timecon

'Timing Controller - Tug-o-War Game'

Title

Declarations

timecon device 'p22v10';

CLK

pin 1;

pin 2;

START

WINNER

pin 3;

y1,y2,y3,y4,y5

pin 21,20,19,18,17 istype 'reg';

OK

pin 22 istype 'buffer';

pin 16 istype 'buffer';

SPKR

Stval = [y1, y2, y3, y4, y5];

a = [0,0,0,0,0];

b = [0,0,0,0,1];

c = [0,0,0,1,1];

d = [0,0,0,1,0];

e = [0,0,1,1,0];

f = [0,1,1,1,0];

g = [1,1,1,1,0];

h = [1,1,0,1,0];

i = [0,1,0,1,0];

j = [0,1,0,1,1];

k = [0,1,0,0,1];

1 = [0,1,0,0,0];

m = [0,0,1,0,0];

n = [0,1,1,0,0];

o = [1,1,1,0,0];

p = [1,0,1,0,0];

q = [1,0,0,0,0];

Equations

Stval.clk = CLK;

State Diagram

Stval

state a: SPKR = 0;

OK = 0;

If START then b

Else

If WINNER then m

Else a;

state b: SPKR = 0;

OK = 0;

If START then c

Else a;

state c: SPKR = 0;

OK = 0;

If START then d

Else a;

state d: SPKR = 0;

OK = 0;

If START then e

Else a;

state e: SPKR = 0;

OK = 0;

If START then f

Else a;

```

Fig. 5.4 - TIMECON source file

```

state f: SPKR = 0;

OK = 0;

If START then q

Else a;

state g: SPKR = 0;

OK = 0;

If START then h

Rise a:

state h:

SPKR = 0;

OK = 0:

If START then i

Else a;

state i: SPKR = 0;

OK = 0;

If START then j

Else a;

state j: SPKR = 0;

OK = 0;

If START then k

Else a:

state k: SPKR = 0;

OK = 0:

If START then 1

Else a;

state 1: SPKR = 1;

OK = 1;

Goto a:

state m: SPKR = 1;

OK = 0:

Goto n;

state n: SPKR = 0;

OK = 0;

Goto o;

state o: SPKR = 1;

OK = 0;

Goto p;

state p: SPKR = 0;

OK = 0;

Goto q;

state q:

SPKR = 1;

OK = 1;

Goto a;

```

Fig. 5.4 (cont'd.) - TIMECON source file

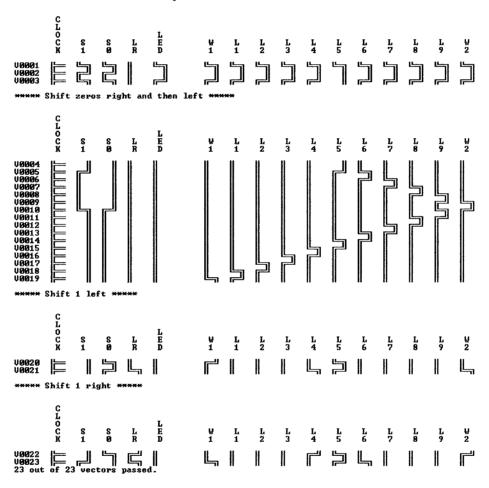

The source file is rather straightforward and follows the state diagram in Fig. 5.3. As in GAMECON, the state variables are grouped into a set named 'Stval' and set constants are defined for the individual state values. The test vectors are perhaps the most interesting feature of the TIMECON source file. The vectors for the 'Interruptions of start loop' are quite large in number. This was necessary due to the fact that the vectors

```

Test Vectors 'power-up, normal start loop'

( [CLK, START, WINNER] -> [Stval, SPKR, OK] )

[.c., 0 , 0 ] -> [ a , 0 , 0 ];

[.c., 0 ,

0 ] -> [ a

0 , 0 ];

[.c., 1 , [.c., 1 ,

0 1 -> [ b , 0 , 0 ];

0 ] -> [ c , 0 , 0 ];

[.c., 1 ,

0 ] -> [ d , 0 , 0 ];

[.c., 1 , [.c., 1 ,

0 ] -> [ e , 0 , 0 ];

0 ] -> [ f , 0 , 0 ];

[.c., 1 ,

0 ] -> [

g , 0 , 0 ];

[.c., 1 ,

0 ] -> [ h , 0 , 0 ];

0 ] -> [ i , 0 , 0 ];

] -> [

0 , 0 ];

0 ] -> [ j ,

[.c., 1 ,

0 , 0 ];

[.c., 1 , [.c., 1 ,

0 ] \rightarrow [k , 0, 0];

0

] -> [

1

1 , 1 ];

[.c., .x.,

.x.] -> [

Test Vectors 'Normal winner loop'

( [CLK, START, WINNER] -> [Stval, SPKR, OK] )

[.c., 0 , 1 ] -> [ m , 1 , 0 ];

[.c., .x. ,

x. ] \rightarrow [n, 0, 0];

[.c., .x. , .x. ] \rightarrow [ o , 1 , 0 ];

[.c., .x. , .x.] \rightarrow [ p , 0 , 0 ];

[.c., .x.,

.x.] -> [

1 , 1 ];

q,

[.c., .x., .x.] \rightarrow [ a , 0 , 0 ];

Test Vectors 'Interruptions of start loop'

( [CLK, START, WINNER] -> [Stval, SPKR, OK] )

[.c., 1 , 0 ] \rightarrow [ b , 0 , 0 ];

.x. ] -> [ a , 0 , 0 ];

0 ] -> [ b , 0 , 0 ];

[.c., 0 ,

[.c., 1 ,

0,0];

0 ] -> [ c , 0 , 0 ];

[.c., 1 ,

[.c., 0 , .x.] -> [ a , 0 , 0 ];

[.c., 1 , 0 ] -> [ b , 0 , 0 ];

[.c.,

0 , 0 ];

0 ] -> [ c , 0 , 0 ];

[.c., 1 ,

0 ] -> [ d , 0 , 0 ];

[.c., 1 ,

ο,

a ,

[.c.,

.x.] -> [

0,0

[.c., 1 ,

0 ] -> [ b

, 0,0];

0 ] -> [ c , 0 , 0 ];

[.c., 1 ,

1 ,

] -> [

0

đ

, 0,0

[.c.,

0 ] -> [ e , 0 , 0 ];

[.c.,

1 ,

[.c., 0 ,

a , 0 , 0 ];

.x.] -> [

1 ,

0

] -> [

b

, 0,0

[.c.,

[.c., 1 ,

1 <- [ 0

C

, 0,0];

[.c., 1 ,

0 ] -> [ d , 0 , 0 ];

1 ,

1 ,

0 1 -> [ e , 0 , 0 ];

0 1 -> [ f , 0 , 0 ];

[.c.,

[.c.,

.x. ] -> [ a ,

[.c., 0 ,

0 , 0 ];

1 ,

, 0,0];

[.c.,

0

] -> [

b

0 ] -> [

1,

, 0,0];

[.c.,

C

[.c., 1 ,

0 ] -> [

d , 0 , 0 ];

[.c.,

1 ,

0

] -> [

e , 0 , 0 ];

0 ] -> [

[.c.,

1,

£

, 0,0];

[.c., 1 ,

0 ] -> [ g ,

0 , 0 ];

[.c., 0 ,

.x.] -> [

a , 0 , 0 ];

0 ] -> [

1 ,

[.c.,

b

, 0,0];

[.c., 1 ,

0 ] -> [

0 1 -> [ d

0 1 -> [

, 0,0];

1 ,

[.c.,

, 0,0];

[.c.,

0 , 0 ];

[.c., 1 ,

0 ] -> [

0 , 0 ];

0 ] -> [ g , 0 , 0 ];

0 ] -> [ h , 0 , 0 ];

[.c., 1 ,

[.c.,

1

0 , 0 ];

[.c., 0 ,

.x.] -> [ a ,

```

Fig. 5.4 (cont'd.) - TIMECON source file

```

[.c., 1 ,

] -> [ b

[.c., 1 ,

] -> [

0

0];

0

C

[.c.,

1 ,

] -> [

d

0

0

0 ] -> [

[.c., 1 ,

ο,

0

e

[.c., 1 ,

0 ] -> [

£

0

0];

[.c., 1 , [.c., 1 ,

] -> [

g

0 ] -> [

h

[.c., 1 ,

0 ] -> [

[.c., 0 ,

.x. ] -> [

a

0

0

j -> [

0

b

0

[.c., 1 ,

[.c., 1 ,

0 ] -> [

1,

] -> [

[.c.,

0

đ

0

0

[.c.,

1

0

] -> [

e

0

0

[.c., 1 ,

] -> [

-> [

[.c.,

1 ,

0

0

0

g

1,

[.c.,

0

] -> [

h

0

0

[.c., 1 ,

] -> [

-> [

1,

[.c.,

0

j

0

0

ο,

[.c.,

. x .

1 ->

a

0

0

[.c., 1 ,

ι

-> [

1,

0

C

0

0

[.c.,

0

] ->

đ

[.c.,

1

[

0

0

[.c., 1 ,

] -> [

1 ,

] -> [

[.c.,

0

£

0

0

0

] ->

[.c.,

1

[

g

0

[.c., 1 ,

] -> [

1,

-> [

[.c.,

0

i

0

0

1 -> [

1,

0

[.c.,

0

[.c., 1 ,

] -> [

ο,

.x. ] -> [

[.c.,

а

0

0

1,

[.c.,

0

] -> [

ъ

0

[.c., 1 ,

] -> [

C

[.c.,

1 ,

0

] -> [

đ

0

0

[.c.,

1

0

] ->

e

0

0

[.c., 1 ,

] -> [

f

[.c., 1 , [.c., 1 ,

0

j -> [

O

g

0

] ->

h

0

] -> [

i

[.c., 1 ,

0

j -> [

0

j

0

[.c., 1 , [.c., 1 ,

0

] ->

k

0

0

1 , 1 ];

0

] -> [

1

.x.] -> [ a

[.c., .x. ,

```

end

Fig. 5.4 (cont'd.) - TIMECON source file

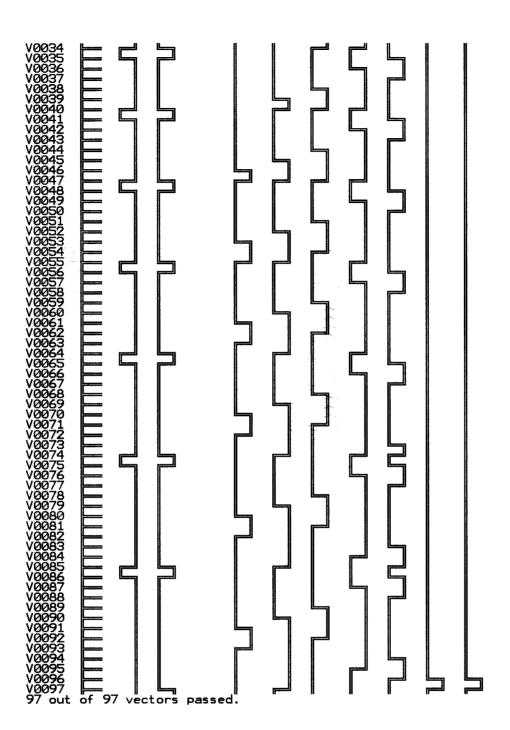

must step through all of the states leading up to the target state. Since the START routine can possibly be interrupted in any state from 'b' to 'k', it was necessary to simulate a reset from each of these states. Every time an interruption occurred and the circuit reset to state 'a', it was necessary to begin stepping through all of the preceding states in order to reach the next state to be simulated as being interrupted. This is a prime example of how tedious writing test vectors can sometimes be. This set of vectors (nearly 100 in number) probably took longer to write than the logic portion of the file.

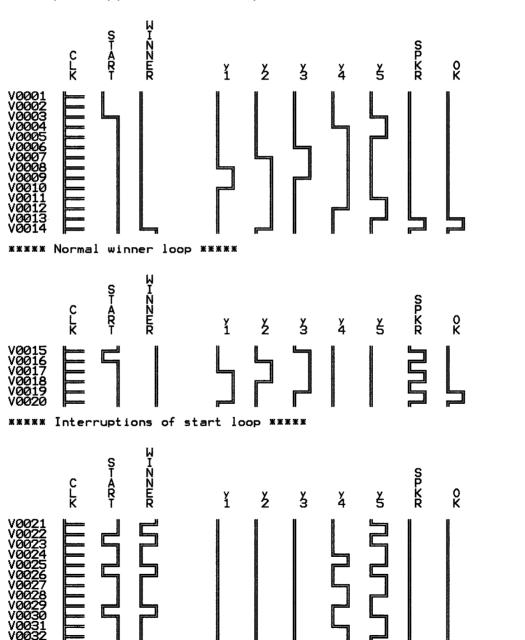

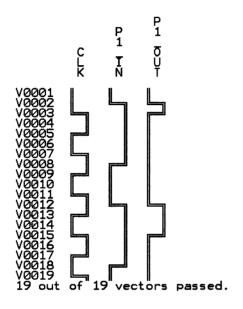

### 5.5 - INPUTCON

The design for the INPUTCON module followed exactly the design and functionality of the original Input Conditioner circuit. Not only were the inputs and outputs identical to the original circuit, but the equations used to describe the logic in the ABEL source file (see Fig. 5.5) were exactly the same as those that made up the asynchronous sequential logic in the original circuit.

```

module

inputcon

title

'Input Conditioner, Tug-o-war Game'

declarations

inputcon device 'p16v8as';

CLK

pin 1;

pin 2;

P1 IN

P2 IN

pin 3;

Y1

pin 17;

pin 16;

¥2

Y3

pin 15;

pin 14;

pin 19;

P1 OUT

P2 OUT

pin 18;

equations

Y1 = (P1 IN & Y1.pin) # (CLK & Y2.pin);

Y2 = (!CLK & P1 IN) # (P1 IN & Y2.pin) # (CLK & Y2.pin);

P1_OUT = (P1_IN & !Y2.pin) # (!CLK & P1_IN & !Y1.pin);

Y3 = (P2 \text{ IN } \& Y3.pin) \# (CLK \& Y4.pin);

Y4 = (!CLK & P2_IN) # (P2_IN & Y4.pin) # (CLK & Y4.pin);

P2_OUT = (P2_IN & !Y4.pin) # (!CLK & P2_IN & !Y3.pin);

test_vectors

'Pulse catcher for P1'

( [ CLK, P1_IN ] -> [ P1_OUT ] )

[ 0, \overline{0} ] \rightarrow [ 0\overline{1};

[ 0,

1 ] -> [ 1 ];

] -> [ 0 ];

[ 1,

1

] -> [ 0 ];

1,

1

Ο,

] -> [ 0 ];

] -> [ 0 ];

Ο,

[

1

] -> [ 0 ];

1,

1

] -> [ 0 ];

[

1,

] -> [ 0 ];

Ο,

[

0

] -> [ 0 ];

Ο,

0

1,

] -> [ 0 ];

[

1,

] -> [ 1 ];

[

1

Ο,

1

] -> [ 1 ];

[

Ο,

[1];

] -> [ 0 ];

1,

1

[

] -> [ 0 ];

1,

1

[ 0,

] -> [ 0 ];

Ο,

] -> [ 0 ];

0

[

[

1,

0

end

```

Fig. 5.5 - INPUTCON source file

Equations were used to describe the logic instead of a state diagram structure due to the asynchronous sequential behavior of the design. During the course of the author's research, no evidence was found that ABEL will allow a state diagram structure to describe an asynchronous design. It apparently assumes a registered design when a state diagram logic structure is used in a source file. In any event, combinatorial feedback equations were used to describe the sequential logic of the design, as is evident from the usage of the combinatorial output assignment operator '=' and the '.pin' feedback dot extension.

The reader will also notice that test vectors only exist for the player 1 (P1\_OUT) equations. The equations that determine P2\_OUT are identical to those for P1\_OUT except for the substitution of P2\_IN for P1\_IN. Therefore, it was easier to simply change the test vector heading signals for P1 to P2 and re-simulate the vectors rather than typing an additional set of them.

### 5.6 - Additional Notes

Truth tables were considered for describing design logic at various points in the design process of each of the four modules. However, in each case, it was eventually decided that this was too inefficient a method. In the GAMECON and TIMECON modules synchronous sequential designs were used. Although these may be implemented in truth table form, the state diagram method of description is more intuitive since the sequential design process basically begins by drawing a state diagram. In the case of OUTCON, there were a large number of inputs involved (including feedback signals) and the truth table would soon have become unwieldy. Finally, in the case of INPUTCON, the equation method of logic description made so much sense in that the equations already existed from the original 7400-series design. It would have required more effort to investigate using a truth table implementation.

In addition, Mealy-type synchronous sequential design methods were not used in any of the four module designs. However, the state diagram structure in ABEL does support the Mealy form of state machine logic. The overall format of a Mealy state diagram in ABEL is similar to that of a Moore design with one exception. The fact that outputs are assigned during the state transition rather than upon arriving in a state (as in a Moore design) is accommodated with the 'with…endwith' statements. For example:

If START then c with [SPKR,OK] := [0,0]; endwith;

The 'with...endwith' statements ensure that the outputs-are decoded at the proper time and do not lag by a clock cycle.

If the reader is interested in using truth tables or Mealy-type sequential logic in his design, he is referred again to the ABEL User Manual<sup>3</sup> and Practical Design Using Programmable Logic.<sup>2</sup> These references have numerous design examples of both techniques.

#### **CHAPTER VI**

### **CONCLUSION**

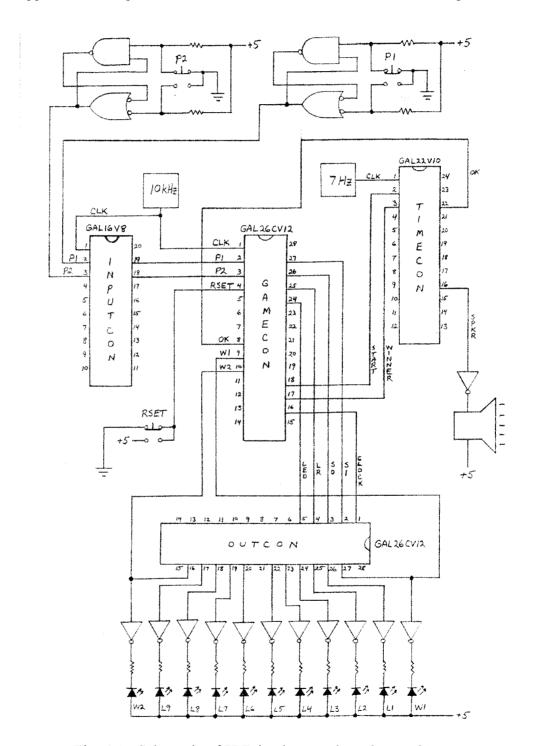

## 6.1 - Project Results

The circuit schematic for the PLD implementation of the Tug of War game is shown in Fig. 6.1. Now, go back and compare this to Fig. 4.2. The reader will notice a striking similarity between the block diagram of the original 7400-series system design and the schematic of the PLD system design. Each system component (block) corresponds to a single PLD, as was the project intent. This graphically demonstrates one of the strongest advantages of using PLD's in a digital circuit design: the conceptual design in many cases may be directly translated into a hardware design.

Once assembled and tested, it was determined by the author that the entire system, with all of its components, was functioning properly. The author even went as far as to drag a couple of students from an adjacent laboratory to witness this fact. They played a few rounds of the game and were satisfied with its operations.

The final device count, including the Quad-NAND and Hex-Inverter chips, was 7. This is versus a total chip count of 31 in the original 7400-series design. That equates to a reduction factor of over 4 to 1. If the input debouncing and output buffering logic had been implemented in their respective PLD's, the total device count would stand at 4, for a reduction of nearly 8 to 1. This would probably be the effective limit for least chip count while using these types of devices (PAL's) in implementing this design. While the individual module designs could have been more complex and still fit into their respective PLD's (many product terms went unused on all 4 devices), only one module may be programmed into a particular device. Also, the small number of outputs on a given PLD

effectively limit the logic that can be assigned to a module and still fit into the device. Therefore, a 1 to 1 correspondence between each of the system components and PLD would appear to be the practical limit for device count limitation in this design.

Fig. 6.1 - Schematic of PLD implementation of Tug of War

### 6.2 - Summary

Programmable Logic Devices are a valuable resource to the digital system designer. When they made their appearance in the 1970's, they finally enabled the designer to implement efficient and practical digital designs without the need to rely on the response time of a chip manufacturer in designing a mask-programmed device. Design and debug times, as well as physical circuit dimensions, were drastically reduced.

With the advent of the PC in the early to mid 1980's, universal PLD programming software became widely available. Sophisticated programming languages such as ABEL-HDL, along with commercially available universal programmer units, allowed the designer to design, program, and test PLD-based digital designs at his desk, enjoying previously unknown levels of flexibility in the design process.

Using ABEL-HDL, the digital designer is capable of turning design concepts such as Boolean equations, truth tables, and state diagrams directly into hardware implementations. A specific target device does not even need to be identified when the design process is begun. ABEL has the ability to take a generic design and determine which device architectures it will fit into. However, the designer may also use hardware-specific terms in the logic descriptions to tailor a design to a particular device, if so desired.

In order to demonstrate the concepts above, an example of the process of designing a digital system with PLD's was conducted by the author. Using ABEL design techniques, the logic of a previously constructed 7400-series digital circuit was implemented more efficiently using a smaller number of chips.