# MODELING, ANALYSIS, SIMULATION AND MEASUREMENTS OF A FLY-BACK MULTI-LOOP CONTROL SWITCHING MODE POWER SUPPLY

by

Crown-Sen Shieh

Submitted in Partial Fulfillment of the Requirements

for the Degree of

Master of Science in Engineering

in the

Program

Electrical Engineering

Prof Samuel J. Skarote 7/30/86

Advisor Date

Saly M. Hothkisa July 31, 1986

Dean of the Graduate School Date

YOUNGSTOWN STATE UNIVERSITY

August, 1986

#### ABSTRACT

MODELING, ANALYSIS, SIMULATION AND MEASUREMENTS

OF A FLY-BACK MULTI-LOOP CONTROL SWITCHING MODE POWER SUPPLY

Crown-Sen Shieh

Master of Science in Engineering Youngstown State University , 1986

Modeling, analysis, simulation and the measurements of a fly-back switching mode power supply employing multiple loop control are presented. The objectives are to examine the small-signal dynamic performances and to provide an adequate measurement method for the fly-back switching mode power supply which is operated in continuous MMF mode at a constant frequency.

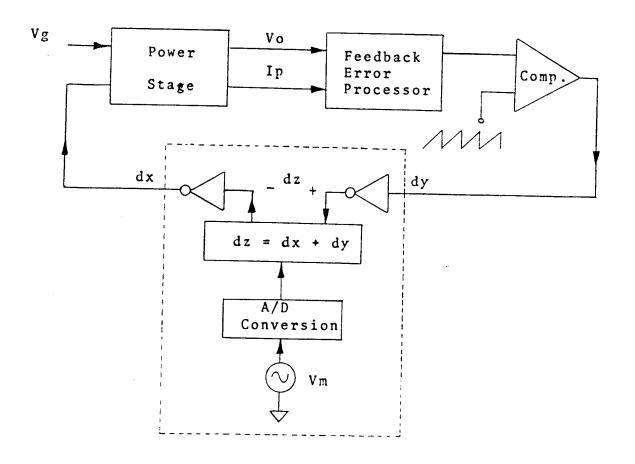

To gain insights to the performance characteristics of the power supply, the power supply is modeled according to the three basic functional blocks: fly-back power stage, error processor, and pulse width modulator. After the small-signal model of each block are assembled, the audio-susceptibility, output impedance, and system loop gain characteristics are simulated. Finally, an adequate measurement method, digital modulation technique, is introduced and the experimental verifications of the system loop gain are presented.

| 4.3.2 Derivation of Coefficients $c_1$ and $d_1$                           | 45  |

|----------------------------------------------------------------------------|-----|

| 5. SIMULATION                                                              | 48  |

| 5.1 Introduction                                                           | 48  |

| 5.2 Simulations of Audio-susceptibility and Output Impedance               | 49  |

| 5.2.1 Equation Formulations                                                | 50  |

| 5.2.2 Simulation Results of Audio-susceptibility and Output Impedance      | 53  |

| 5.3 The System Loop Gain Characteristics                                   | 56  |

| 6. MEASUREMENT                                                             | 60  |

| 6.1 Loop Gain Measurement and Analog Modulation Technique                  | 60  |

| 6.2 Consideration of Loop Gain Measurement in Switching Power Supply       | 62  |

| 6.3 Digital Modulation Technique                                           | 62  |

| 6.3.1 The Digital Modulator                                                | 63  |

| 6.3.2 The Digital Demodulator                                              | 67  |

| 6.4 Loop Gain Measurement with Digital Modulation Technique                | 70  |

| 6.4.1 Determination of T Without Amplifier                                 | 71  |

| 6.4.2 Determination of T With Amplifier                                    | 74  |

| 6.5 Results of Loop Gain Measurements                                      | 76  |

| 7. CONCLUSION                                                              | 79  |

| APPENDIX A. Derivations of State-space Equations                           | 81  |

| APPENDIX B. Derivations of Transfer Functions for Fly-<br>Back Power Stage | 85  |

| APPENDIX C. Data Provision of Simulation and Computer Simulation Program   | 91  |

| REFERENCES                                                                 | 101 |

·

r

•

; (

N.

.

## LIST OF SYMBOLS

| SYMBOL                            | DEFINITION                                                |

|-----------------------------------|-----------------------------------------------------------|

| A/D                               | Analog to digital converter                               |

| A(s)                              | Open-loop gain of an operational amplifier                |

| Ax, Ay                            | Gains                                                     |

| С                                 | Control output                                            |

| c <sub>1</sub> - c <sub>3</sub>   | Capacitors or capacitance                                 |

| d(t)                              | Instantaneous value of the duty cycle                     |

| ã(t)                              | Time-varying component of the duty cycle                  |

| D                                 | Steady state value of the duty cycle                      |

| D '                               | D' = 1 - D                                                |

| dх                                | Digital forward signal in the loop gain measurement       |

| dx*                               | Delayed digital forward signal for measurement            |

| dу                                | Digital returned signal in the loop gain measurement      |

| dy*                               | Delayed digital returned signal for measurement           |

| dy <sub>A</sub> , dy <sub>B</sub> | Push-pull inputs to the digital modulator                 |

| dz                                | Injected digital disturbance in the loop gain measurement |

| E                                 | Error output                                              |

| EP                                | Error processor                                           |

| Er                                | Reference voltage source                                  |

| ESR                               | Equivalent series resistance of a capacitor               |

| $^{\mathrm{F}}\mathrm{_{C}}$      | Transfer function of the current feedback loop            |

| F <sub>D1</sub> , F <sub>D2</sub> | Elements of dynamic matrix related to duty cycle          |

| F <sub>M</sub>                    | Transfer function of the pulse width modulator            |

| $^{\rm F}{ m V}$                  | Transfer function of the voltage feedback loop            |

G Forward path gain Audio-susceptibility characteristics  $G_{\mathbf{A}}$ GO Circuit parameter Η Feedback path gain  $i_0(t)$ Small-signal component of the output current  $i_0(t)$ Instantaneous value of the output current Instantaneous value of the current in the primary i<sub>p</sub>(t) winding of a inductor  $\tilde{i}_{p}(t)$ Small-signal component of ip  $i_s(t)$ Instantaneous value of the current in the secondary winding of a inductor K Constant KCL Kirchoff's current law Kirchoff's voltage law KVL  $L_{\triangleright}$ Inductance LISA Computer program package, Linear System Analysis, developed by IBM  $L_{\mathbf{p}}$ Primary inductance Secondary inductance  $L_{S}$ LSI Large scale integration MMF Magnetomotive force MOSFET Metal oxide semiconductor field effect transistor Turns ratio of a current transformer n Turns of the primary windings  $N_{P}$ Turns of the secondary windings  $N_{S}$ PWM Pulse width modulation R Reference input Resistors or equivalent resistance  $R_N$ ,  $R_{\odot}$

ESR of a capacitor

$R_{C}$

Load resistor  $R_{T_{\bullet}}$  $R_{\mathbf{p}}$ DC resistance in the primary winding of a inductor DC resistance in the secondary winding of an  $R_{S}$ inductor Load resistor of a current transformer RSW Slopes SN, SF Т System loop gain  $T_{\text{off}}$ ,  $T_{\text{F1}}$  Turn-off interval Turn-on interval Ton Period  $_{\mathbf{q}}^{\mathbf{T}}$ U Input vector (steady state) Input vector <u>u</u> Small-signal voltage at node A and node B respective to common Instantaneous value of the capacitor voltage  $v_c(t)$  $v_i(t)$ Instantaneous value of the input voltage  $v_i(t)$ Small-signal component of the input voltage DC component of the input voltage Vi V DC output voltage  $\tilde{v}_{o}(t)$ Small-signal component of the output voltage Voltage induced in the secondary winding of an  $v_s(t)$ inductor Voltage output in a current transformer with load  $v_{sw}(t)$ resistor  $v_{t}(t)$ Threshold voltage Output voltage of the error processor  $v_x(t)$ ٧x Analog forward signal in the loop gain measurement Analog returned signal Vу in the loop gain measurement ٧z Injected analog disturbance in the loop gain

measurement

| w <sub>n</sub>        | Circuit parameter or natural frequency              |

|-----------------------|-----------------------------------------------------|

| <u>x</u>              | State variable                                      |

| <u>x</u>              | Time-varying component of x                         |

| <u>x</u>              | dx/dt                                               |

| $\frac{\tilde{x}}{x}$ | dx/dt                                               |

| <u>y</u>              | Output vector                                       |

| $z_{X}$ , $z_{Y}$     | Impedance                                           |

| $z_0$                 | Output impedance                                    |

| ф                     | Magnetic flux                                       |

| ζ                     | Circuit parameter or damping factor                 |

| Δ                     | Characteristic equation of the fly-back power stage |

## LIST OF FIGURES

| FIGURE |                                                                                                                                                          | PAGE |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

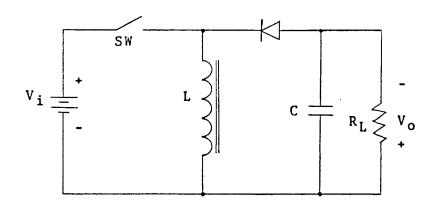

| 1.     | Basic Configuration of a Fly-back DC/DC Coverter                                                                                                         | 2    |

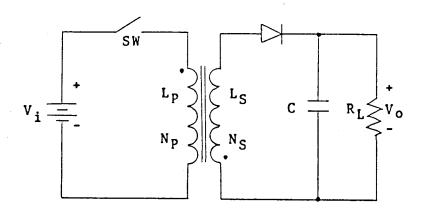

| 2.     | Transformer Coupled Version of a Fly-back DC/DC Converter                                                                                                | 2    |

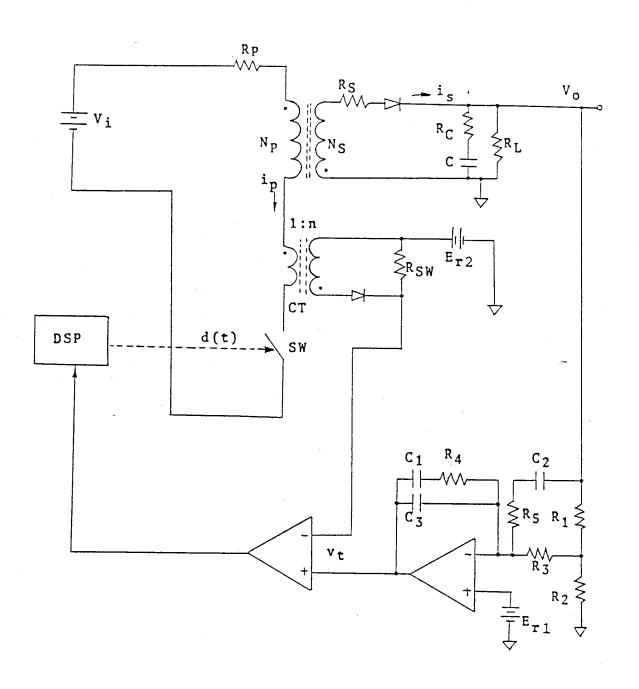

| 3.     | Circuit Schematic of a Two-loop Control Fly-back Switching Mode Power Supply                                                                             | 5    |

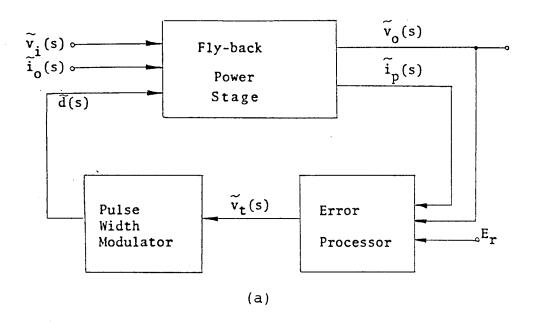

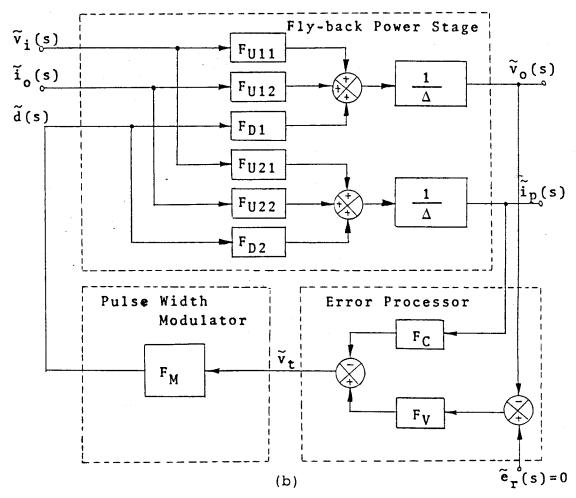

| 4.     | Two-loop Control Fly-back Switching Mode Power Supply. (a) Simplified Functional Blocks, (b) Small-signal Model                                          | 6    |

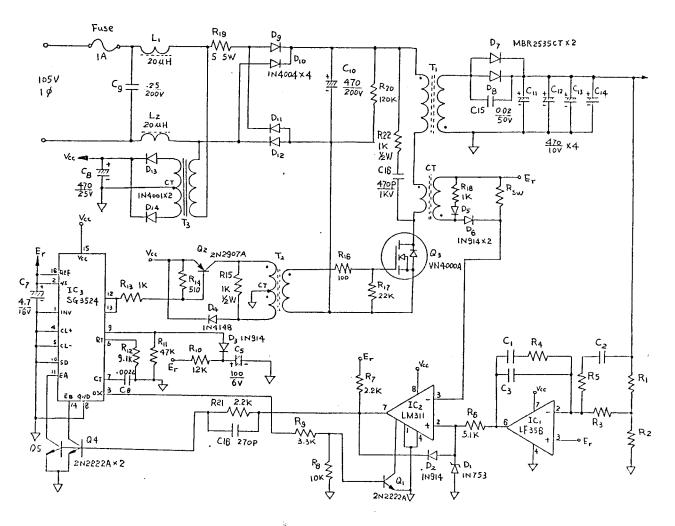

| 5.     | Complete Schematic Diagram of a Fly-back, Multi-<br>ple Loop Control, Switching Mode Power Supply.                                                       | 9    |

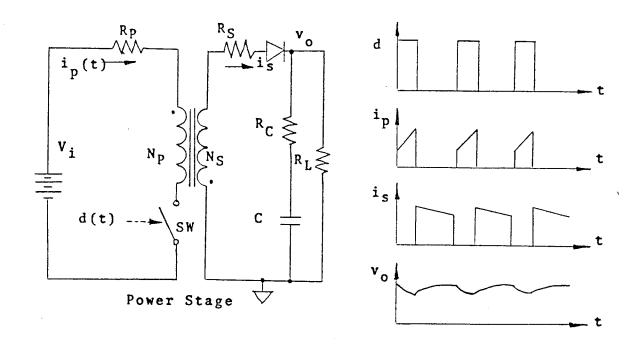

| 6.     | DC/DC Two-winding Fly-back Converter                                                                                                                     | 11   |

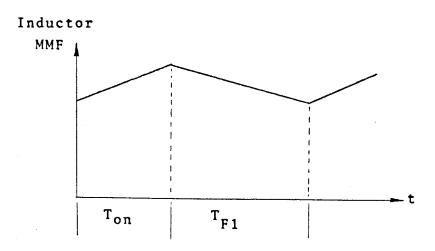

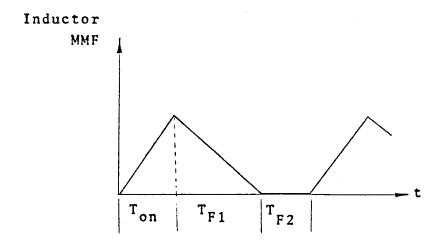

| 7.     | MMF in Continuous Operation Mode                                                                                                                         | 12   |

| 8.     | MMF in Discontinuous Operation Mode                                                                                                                      | 12   |

| 9.     | Two-winding Fly-back Power Stage (a) Two Winding Fly-back Power Stage. (b) Equivalent Circuit Model During Ton. (c) Equivalent Circuit Model During Toff | 20   |

| 10.    | Block Diagram of Fly-back Power Stage                                                                                                                    | 27   |

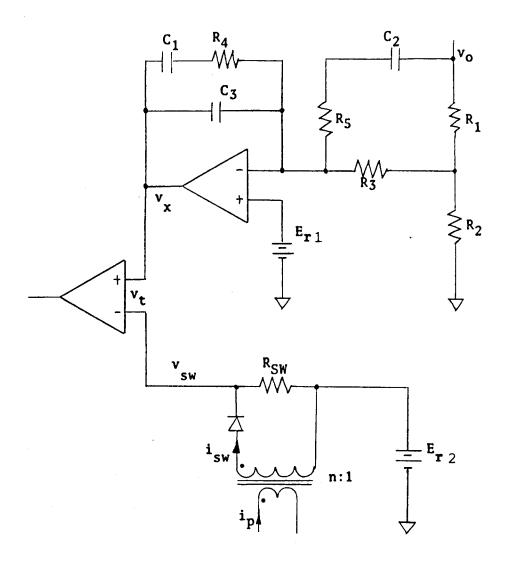

| 11.    | Error Processor                                                                                                                                          | 29   |

| 12.    | Equivalent Analytical Circuit of an Error Processor                                                                                                      | 31   |

| 13.    | Error Processor Block Diagram                                                                                                                            | 34   |

| 14.    | Pulse Width Modulator Without Disturbance                                                                                                                | 36   |

| 15.    | Unperturbed Analytical Pulse Width Modulator Waveforms                                                                                                   | 38   |

| 16.    | Perturbed Analytical Pulse Width Modulator Wave-forms                                                                                                    | 40   |

| 17.    | Pulse Width Modulator Block                                                                                                                              | 47   |

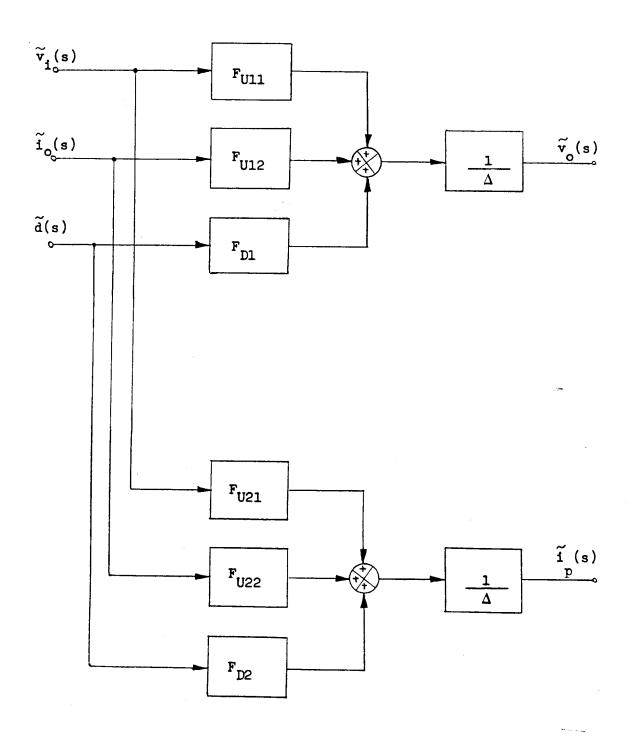

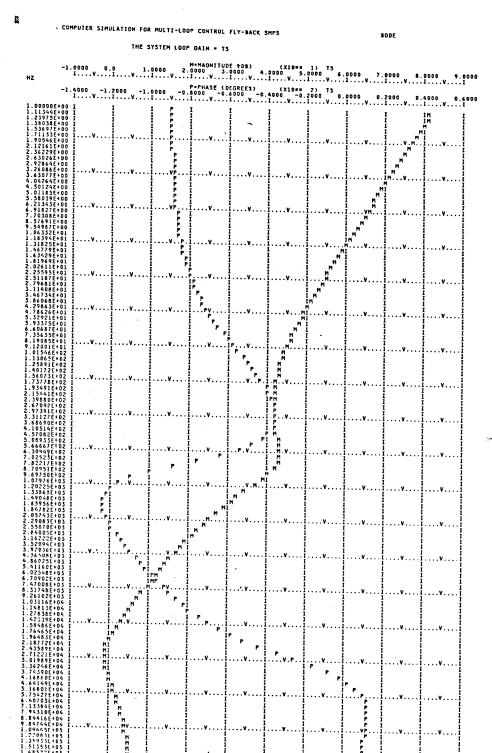

| 18.    | Small-signal Block Diagram of a Fly-back Switch-ing Mode Power Supply                                                                                    | 51   |

| 19.    | Bode Plot for Audio-susceptibility                                                                                                                       | 54   |

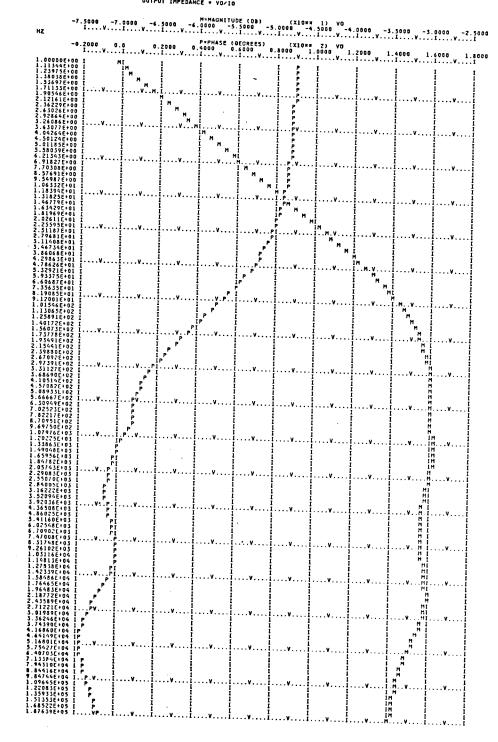

| 20. | Bode Plot for Output Impedance                                                                          | 55 |

|-----|---------------------------------------------------------------------------------------------------------|----|

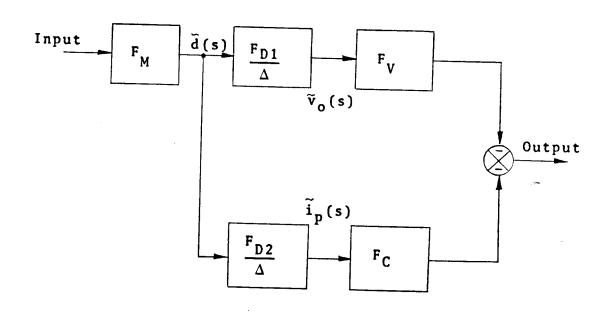

| 21. | Block Diagram for The System Loop Gain                                                                  | 57 |

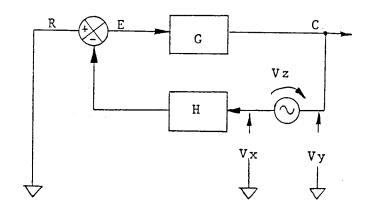

| 22. | Bode Plot for The System Loop Gain                                                                      | 59 |

| 23. | Conventional Analog Modulation Scheme                                                                   | 61 |

| 24. | Digital Modulation Scheme                                                                               | 63 |

| 25. | Schematic of The Digital Modulator                                                                      | 64 |

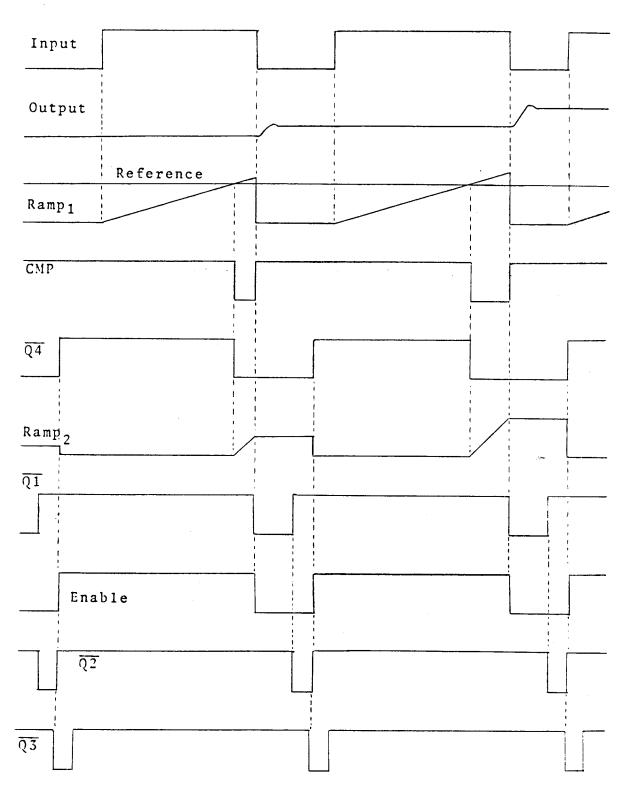

| 26. | Waveforms in The Circuit Schematic of Fig. 25                                                           | 65 |

| 27. | Schematic of The Digital Demodulator                                                                    | 68 |

| 28. | Waveforms in The Circuit Schematic of Fig. 27                                                           | 69 |

| 29. | Application of The Digital Modulation Technique for Loop Gain Measurement with a Switching Power Supply | 71 |

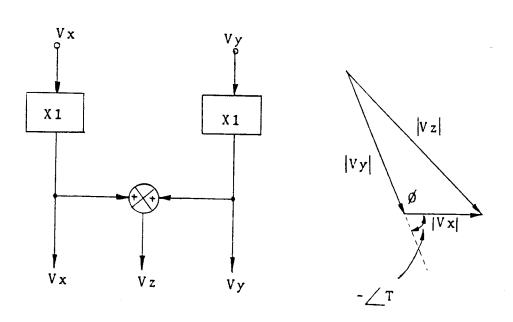

| 30. | Determination of T, by The Measurement of The Three Magnitude $ Vx $ , $ Vy $ and $ Vz $                | 72 |

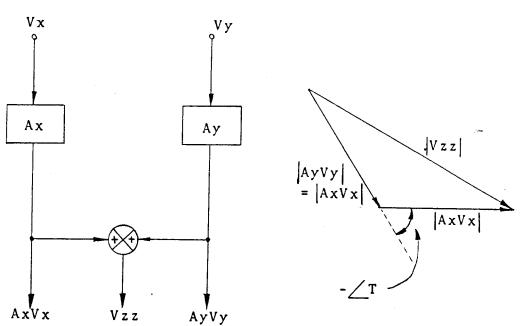

| 31. | Determination of $\angle$ T by The Measurement of The Scaled Magnitude $ AxVx  =  AyVy $ and $ Vzz $    | 75 |

| 32. | Measurement and Simulation Bode Plot of The System Loop Gain                                            | 78 |

#### CHAPTER 1

#### INTRODUCTION

Switching mode power supplies [1] have gained widespread use recently. Because of their high efficiency, small size and weight, they are replacing the conventional linear power supply in both industrial applications and consumer products. To reduce the size, weight and power dissipation of LSI equipments, particularly in microprocessor based units and television, most designers are turning to switching mode power supplies. Increased volume production, particularly of semiconductors and special magnetic material, have reduced the price of switching mode power supply to the point that their advantages are now available to all users.

Fundamentally, the switching mode power supply is a DC/DC converter. The basic fly-back configuration of a DC/DC converter is shown in Figure 1. The energy exchange takes place in the fly-back DC/DC converter in the following While the switch is closed, a current flows fashion. through the inductor, L, and stores the energy in the magnetic field. As the switch is open, the stored energy in magnetic field is discharged into the capacitor and the load resistor, transforming energy from the input to the The transformer coupled version of the basic flyback configuration is shown in Figure 2. This version provides several important advantages, particularly in

applications where primary power is 120VAC or 230VAC. First, the transformer provides input/output isolation required for off-line power supplies and removes the polarity restriction of the input/output in Figure 1. Also, multiple outputs at various voltage are easily obtained with multiple secondary windings.

Figure 1. Basic Configuration of a Fly-back DC/DC Converter

Figure 2. Transformer Coupled Version of a Fly-back DC/DC Converter

Due to the finite flux capacity of the inductive element, a DC/DC converter must be oscillatory in nature.

The oscillation is achieved by cyclically operating the power switch of the converter in the conduction and the non-conduction state. Consequently, the converter control system must be able to accept an analog signal obtained from the sensing circuit and reference and convert it into discrete time intervals for controlling the conduction and non-conduction of the power switch. The electrical performance characteristics of interest to a converter designer include stability as well as the converter output response to a step and sinusoidal disturbances, both from the line and the load.

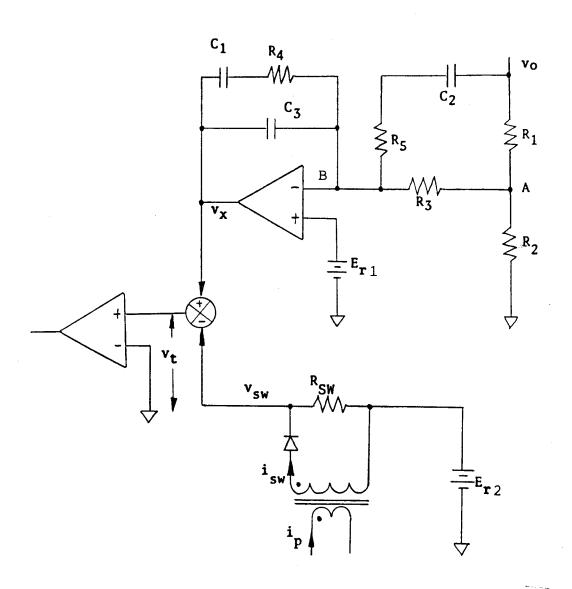

The conventional single loop control power supply senses the capacitor state variable in the form of an output capacitor voltage to serve as the control signal. Illustrated in Figure 3 is a fly-back switching power supply employing multiple loop control. In addition to the capacitor voltage sensing loop, a second loop sensing the inductor current is present. The total sensing of the states associated with the LC section provides the power supply with excellent static and dynamic stabilities. In addition, the frequency response shaping can become grossly ineffective due to variations of power or control component parameters resulting from tolerance, environments, aging and operating condition.

In Figure 3, the control is implemented by sensing the following quantities: the output voltage of the converter,  $\mathbf{v}_0$ , or the output capacitor voltage, and the instantaneous current through the power switch,  $\mathbf{i}_p$ , or the

inductor current. The duty cycle signal is terminated by the threshold detector when the switching current ascends and intersects the floating threshold voltage,  $v_x$ , which is determined by subtracting  $v_o$  from the reference voltage,  $E_r$ . This threshold detector thus provides inherent transistor peak current protection and limits the electrical stresses in power components as well.

Presented in this thesis are the modeling, analysis, simulation, and measurement of the above described system in Figure 3, which contains three basic functional blocks: a fly-back power stage, an error processor, and a pulse width modulator. The modeling and analysis approaches applied to each block are listed below:

- (1) Fly-back power stage: State space averaging technique [2] and state space representation are used to develop the model of three inputs with two outputs for the fly-back power stage. After perturbation, linearization and the Laplace transformation are taken, a small-signal model and a set of transfer functions are obtained.

- (2) Error processor: Deriving the input/output model of error processor by KCL is straightforward.

- (3) Pulse width modulator: The describing function technique [3] and Fourier series are used to derive the model of the pulse width modulator.

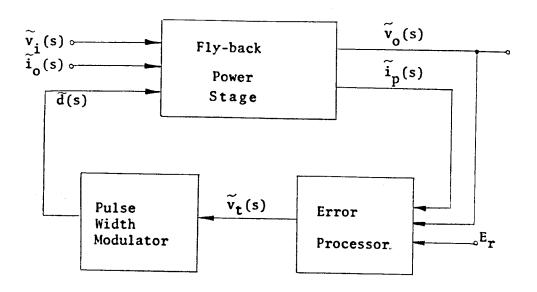

The small-signal model of Figure 3 is derived as shown in Figure 4. The small-signal model has the following features:

Figure 3. Circuit Schematic of a Two-loop Control Fly-back Switching Mode Power Supply

Figure 4. Two-loop Control Fly-back Switching Mode Power Supply. (a) Simplified Functional Blocks, (b) Small-signal Model

(a) The fly-back power stage has three inputs and two outputs. The three inputs are:

> Line disturbance  $\tilde{v}_i$ Load disturbance  $\tilde{i}_0$

Duty cycle disturbance d

The two outputs are:

The output voltage  $\tilde{v}_{_{\mbox{\scriptsize O}}}$

The switching current  $\tilde{i}_p$

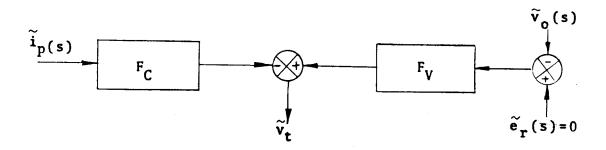

- (b) The error processor senses the two modulation signals,  $\tilde{i}_p$  and  $\tilde{v}_o$ . The transfer function  $F_V$  represents the gain of the voltage control loop and compensation network. The  $F_C$  represents the gain of the current control loop.

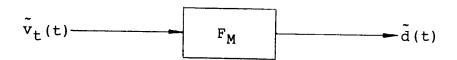

- (c) The pulse width modulator is represented by a  $\hbox{"single-input single-output" model, $F_M$.}$

Employing the above described small-signal model, one can readily examine the following performance characteristics:

(1) The system loop gain characteristics

$$T = -\frac{1}{\Delta} - F_{M} (F_{V}F_{D1} + F_{C}F_{D2})$$

(1)

The system loop gain characteristics T is used to examine the relative stability of the system.

- (2) The audio-susceptibility characteristics  $G_{A} = \tilde{v}_{O}/\tilde{v}_{1}$

- (3) The output impedance characteristics  $Z_0 = \tilde{v}_0/\tilde{i}_0$

Although the above described small-signal model is a linear system, examining the performance characteristics without a computer becomes a tedious and time consuming

task. Therefore, computer simulation or the study of the dynamic response of mathematical models using the electronic computer has become a standard tool in engineering. Many computer program packages designed to solve linear equations and transfer functions are now available. Among those packages for such an approach is the "LISA 360 A Program for Linear System Analysis (LISA 360)" [4], a well-known computer program package developed by IBM. The LISA 360 program package can be used to compute the following solutions:

- (a) Pole and zero locations

- (b) Time response to a step or a sinusoidal inputs

- (c) Bode response over a range of frequencies

- (d) Sensitivity of a function to component variations at a given frequency

From computer simulation, the information about performance characteristics of this power supply can be obtained.

Finally, a real circuit shown in Figure 5 has been constructed for demonstration purposes. Also, a digital modulation scheme for loop gain measurements is presented. The measurements of the system loop gains of the actual circuit were performed to verify the small-signal model.

Figure 5. Complete Schematic Diagram of a Fly-back, Multiple Loop Control, Switching Mode Power Supply

#### CHAPTER 2

## CURRENT-FEEDBACK FLY-BACK POWER STAGE MODEL

## 2.1 Power Circuit Description

The function of the power supply is to process and transfer electric power from an unregulated input  $V_i$  to a regulated output  $V_o$ . Fundamentally, the power stage of a power supply is a DC/DC converter. The output voltage of the two-winding fly-back converter as shown in Figure 6 can be either greater than or less than the input voltage, depending on the duty cycle of the switch and the turns ratio of the storage inductor. The magnetically-coupled windings, provided by the energy-storage inductor, allows for input/output isolation and multiple outputs. In addition, proper choice of the inductor's turns ratio also can alleviate the difficulty of implementing the extreme duty cycle condition due to wide ranges of input and output voltages.

The energy exchange takes place in the power stage in the following fashion. The state of the duty cycle d(t) determines the instantaneous position of the switch. The high level state of the signal d(t) indicates conduction, and the low-level state determines the off-time, or off-state, of the power switch. During  $T_{\rm on}$  a voltage approximately equal to  $V_{\rm i}(t)$  (neglecting the losses due to the parasitic resistance in the primary windings) is established across  $N_{\rm p}$  which causes a current  $i_{\rm p}(t)$  to increase as illustrated in Figure 6.

Figure 6. DC/DC Two-winding Fly-back Converter

Simultaneously, a voltage  $V_{\rm S}(t)$  is induced across  $N_{\rm S}$  by transformer action, but no current conduction takes place because of the reverse biased diode. As the off-time,  $T_{\rm off}$  is initiated, the energy associated with  $N_{\rm P}$  is transferred to  $N_{\rm S}$  by an ampere-turn redistribution. As a result, the current  $i_{\rm P}(t)$  is reduced to zero and  $i_{\rm S}(t)$  is forced to a magnitude needed to maintain a continuous MMF flow through the inductor. The output voltage in Figure 6 is kept nearly constant due to the large capacitive filter at the output which absorbs the pulsating current  $i_{\rm S}(t)$  and delivers an almost DC current,  $i_{\rm O}$ , to the load.

## 2.2 Analytical Implementation

The nondissipative, switched DC/DC converter is nonlinear in nature. The basic DC/DC voltage conversion is achieved by repetitive switching between a number of linear networks consisting of switches and diodes. The number of linear networks in one switching cycle is determined by the mode of operation of the inductor's magnetomotive force, MMF. If the MMF is continuous as shown in Figure 7, the power stage model has two linear networks. For a

Figure 7. MMF in Continuous Operation Mode

Figure 8. MMF in Discontinuous Operation Mode

discontinuous inductor MMF operation as shown in Figure 8, the power stage model has three linear networks

Each linear circuit model is described by a set of linear state space equations. For the current feedback fly-back power stage, the state variables are customarily the magnetic flux,  $\phi$ , and the capacitor voltage,  $v_c$ . The total number of storage elements determines the order of the system.

## 2.2.1 State Space Averaging Technique

To derive a linear model for the power stage, the averaging technique is used. Employing the continuous operation mode, the power stage is modeled by two intervals of operation,  $T_{\rm on}$  and  $T_{\rm F1}$ , respectively.

The principle of the average method is to replace the state description of the two linear circuits by a single state-space description which represents the approximate behavior of the system through one cycle of operation. Taking the average of both intervals and summing the results yields the following linear equation for a continuous system:

$$\dot{x} = d (A1 x + B1 u) + d' (A2 x + B2 u)$$

(4)

$$\underline{y} = d (C1 \underline{x} + E1 \underline{u}) + d' (C2 \underline{x} + E2 \underline{u})$$

(5)

$$d = \frac{T_{on}}{T_{p}}$$

$$d' = \frac{T_{F1}}{T_{p}}$$

where  $T_{\text{p}}$  is the period of the switching cycle.

The basic requirement for the average method is that the effective filter corner frequency of the switching converter must be much lower than the switching frequency.

The linear time-varying equations can be rewritten in the following form:

$$\dot{\underline{x}} = A \underline{x} + B \underline{u} \tag{6}$$

$$\underline{\underline{Y}} = C \underline{\underline{x}} + E \underline{\underline{u}} \tag{7}$$

where A = d A1 + d' A2, B = d B1 + d' B2, C = d C1 + d' C2E = d E1 + d' E2.

#### 2.2.2 Perturbation

To study the small-signal behavior, the time-varying equations are perturbed. The introduction of input variations and duty cycle variations in turn perturb the output and state vectors. The perturbed input vectors are:

$$\underline{\underline{u}} = \underline{\underline{U}} + \underline{\underline{u}}$$

$\underline{\underline{d}} = \underline{\underline{D}} + \underline{\underline{d}}$

where U and D are the steady-state values. These perturbations in turn lead to the following equations:

$$\underline{x} = \underline{x} + \underline{x}$$

$\underline{x} = \underline{x}$   $\underline{y} = \underline{y} + \underline{y}$

where  $\underline{X}$  and  $\underline{Y}$  are the steady-state values.

Let  $f(\underline{x},\underline{u},d) = \underline{x} = A \underline{x} + B \underline{u}$ , and recall Taylor's series:

$$f(\underline{x},\underline{u},d) = f(\underline{X},\underline{U},D) + f_{\underline{X}}(\underline{X},\underline{U},D) \tilde{x} + f_{\underline{u}}(\underline{X},\underline{U},D) \tilde{u} +$$

$$f_{\underline{d}}(\underline{X},\underline{U},D) \tilde{d} + 1/2 [f_{\underline{X}\underline{X}}(\underline{X},\underline{U},D) \tilde{x}^{2} +$$

$$f_{\underline{u}\underline{u}}(\underline{X},\underline{U},D) \tilde{u}^{2} + f_{\underline{d}\underline{d}}(\underline{X},\underline{U},D) \tilde{d}^{2} +$$

$$2f_{\underline{X}\underline{u}}(\underline{X},\underline{D},U) \tilde{x} \tilde{u} + 2f_{\underline{u}\underline{d}}(\underline{X},\underline{U},D) \tilde{u} \tilde{d} +$$

$$2f_{\underline{X}\underline{d}}(\underline{X},\underline{U},D) \tilde{x} \tilde{d} ] + \text{high order terms}$$

$$(8)$$

Comparing equation (4) to equation (8), we note that  $f_{xx}$ ,  $f_{uu}$ ,  $f_{dd}$ , and  $f_{xu}$  are zero. The basic equation for the model becomes:

$$\underline{x} = \underline{A}\underline{X} + \underline{B}\underline{U} + \underline{A} \ \underline{x} + \underline{B} \ \underline{u} + [(\underline{A}1 - \underline{A}2)\underline{X} + (\underline{B}1 - \underline{B}2)\underline{U}]\underline{d} +$$

[ (A1 - A2 )

$$\frac{x}{x}$$

+ (B1 - B2 )  $\frac{u}{u}$  ] d (9)

With the corresponding perturbations substituted into the output equation, the output equation becomes:

$$\underline{Y} + \underline{Y} = C\underline{X} + E\underline{U} + C\underline{X} + E\underline{U} + [(C1 - C2)\underline{X} + (E1 - E2)\underline{U}]\underline{d} + [(C1 - C2)\underline{X} + (E1 - E2)\underline{U}]\underline{d} + (10)$$

The perturbed state-space description is nonlinear owing to the presence of the product of two time-dependent quantities  $\underline{x}$  and d.

#### 2.2.3 Linearization

Since the ac variations are very small in magnitude compared to their steady-state value, the following small-signal approximations can be made:

$$\frac{\tilde{u}}{-\frac{1}{U}}$$

<< 1;  $\frac{\tilde{x}}{-\frac{1}{X}}$  << 1;  $\frac{\tilde{y}}{-\frac{1}{Y}}$  << 1

Using the above approximations, the nonlinear second order terms in both the basic model and the output equations can be neglected, resulting in a system of linear equations. Separating the steady-state (dc) and dymanic (ac) parts, the final equations representing the state space model are ascertained. The equations based on the steady-state (dc) model follow:

$$\underline{X} = -A \quad \underline{BU}$$

$$\underline{Y} = C\underline{X} + \underline{EU} = C \quad (-A \quad \underline{BU}) + \underline{EU} = (E - CA \quad \underline{B}) \quad \underline{U}$$

$$(12)$$

For the linear dynamic case:

$$\frac{\dot{z}}{\dot{x}} = A\dot{x} + B\dot{u} + [(A1 - A2)\dot{x} + (B1 - B2)\dot{u}]\dot{d}$$

$$\frac{\ddot{y}}{\dot{y}} = C\dot{x} + E\dot{u} + [(C1 - C2)\dot{x} + (E1 - E2)\dot{u}]\dot{d}$$

(13)

# 2.2.4 Transfer Function For Small-Signal Analysis

For the small-signal analysis, there are particular input/output relations needed to construct the basic

building blocks that are necessary to describe the power stage completely.

In order to find the input/output transfer function, one assumes the duty-cycle variation is zero. Then, the previous linear equations can be simplified as follows:

$$\underline{x} = Ax + Bu ; \underline{y} = Cx + Eu$$

(15)

Taking the Laplace transformation of the above equations, the following relations are obtained:

$$sx(s) - x(0) = Ax(s) + Bu(s)$$

(16)

Let  $\frac{\tilde{x}}{(0)} = 0$ , then

$$\underline{x}(s) = [sI - A] B\underline{u}(s)$$

$$(17)$$

$$\underline{y}(s) = C [sI - A] B\underline{u}(s) + E\underline{u}(s)$$

$$= [C(sI - A) B + E] \underline{u}(s)$$

(18)

In order to find the duty cycle/output transfer function, one assumes the input variation is zero. Then, the linear dymanic equations become:

$$\underline{Y} = C\underline{x} + [(C1 - C2)\underline{X} + (E1 - E2)\underline{U}]d$$

(20)

Taking the Laplace transformation of the above equations, the following relations are obtained:

$$s\underline{x}(s) - \underline{x}(0) = A\underline{x}(s) + [(A1 - A2)\underline{x} + (B1 - B2)\underline{u}]\underline{d}(s)$$

$\underline{y}(s) = C\underline{x}(s) + [(C1 - C2)\underline{x} + (E1 - E2)\underline{u}]\underline{d}(s)$

(21)

Let  $\underline{x}(0) = 0$ , and the resulting state-variable  $\underline{x}$  to duty-cycle modulation  $\underline{a}$  and output  $\underline{y}$  to duty-cycle modulation  $\underline{a}$  are:

$$\frac{x(s)}{-\frac{1}{d(s)}} = (sI - A) \begin{bmatrix} (A1 - A2)X + (B1 - B2)U \end{bmatrix}$$

(23)

$$\frac{y(s)}{-\frac{1}{d}(s)} = C (sI - A) [ (A1 - A2)X + (B1 - B2)U ] + [ (C1 - C2)X + (E1 - E2)U ]$$

These transfer functions will be used as building blocks to construct the power stage transfer functions presented in the following sections.

#### 2.3 Power Stage Model

The objective of the power stage model is to develop a group of transfer functions that describe the low frequency behavior of the switching circuit. The model is comprised of three inputs and two outputs. The three inputs are the supply voltage,  $v_i$ , the output current,  $i_0$ , and the duty-cycle, d. The two outputs are the output voltage,  $v_0$ ,

and the switching current, ip.

For the two winding fly-back power stage shown in Figure 9 (a), two equivalent linear circuit models for the continuous operation mode are shown in Figure 9 (b) and (c). The power stage model contains an ideal switch and a diode. The storage inductor is composed of a primary winding and a secondary winding with inductance  $L_p$  and  $L_s$  respectively. Also described by the model is the winding resistance,  $R_p$  and  $R_s$ . The output filter is represented by a capacitance and an equivalent series resistance,  $R_c$ . A current source,  $i_o$ , is employed to represent a disturbance injected into the converter from the load.

The power stage contains two energy storage elements; therefore, the state variables for both linear equivalent circuits are the magnetic flux,  $\phi$ , and the capacitor voltage,  $v_{\rm C}$ . The magnetic flux links the primary and secondary windings together.

During the interval  $T_{\mbox{on}}$ , the power stage is described by the following equations:

$$\dot{\underline{x}} = A1 \underline{x} + B1 \underline{u}$$

$\underline{y} = C1 \underline{x} + E1 \underline{u}$

(25)

where

$$x = [ \phi \ v_C ]^T$$

,  $u = [ v_i \ i_O ]^T$  ,  $y = [ v_o \ i_D ]^T$

$$C1 = \begin{bmatrix} R_{L} \\ 0 & ---- \\ R_{C} + R_{L} \\ N_{P} \\ ---- & 0 \\ L_{P} \end{bmatrix} \qquad E1 = \begin{bmatrix} 0 & R_{C} / / R_{L} \\ 0 & 0 \end{bmatrix}$$

Figure 9. Two Winding Fly-back Power stage (a) Two Winding Fly-back Power Stage. (b) Equivalent Circuit Model During  $T_{\hbox{on}}$ . (c) Equivalent Circuit Model During  $T_{\hbox{off}}$

During the interval  $\mathbf{T}_{F1}$  the power stage is described by the following equations:

$$\dot{\underline{x}} = A2 \underline{x} + B2 \underline{u} \qquad \underline{y} = C2 \underline{x} + E2 \underline{u} \qquad (26)$$

where

$$A2 = \begin{bmatrix} R_{S} + (R_{C}//R_{L}) & R_{L} & 1 \\ ----- & ---- & ---- \\ L_{S} & R_{C}+R_{L} & N_{S} \\ R_{L} & N_{S} & -1 & 1 \\ ----- & ---- & ---- \\ R_{C}+R_{L} & L_{S}C & R_{C}+R_{L} & C \end{bmatrix}$$

$$B2 = \begin{bmatrix} 0 & -R_{C}//R_{L} & -\frac{1}{N_{S}} \\ R_{C} & 1 \\ 0 & -\frac{1}{R_{C}+R_{L}} & C \end{bmatrix}$$

$$E2 = \begin{bmatrix} 0 & R_{C}//R_{L} \\ 0 & 0 \end{bmatrix}$$

Appendix A shows the derivation of equations (25) and (26) representing the two equivalent linear models used to describe the power stage during the times  $T_{\rm on}$  and  $T_{\rm F1}$ .

#### 2.3.1 Average Model

Continuing the process to characterize the small-signal model needed to describe the dymanic behavior, the average model for the power stage is:

$$\dot{\mathbf{x}} = \mathbf{A} \, \mathbf{x} + \mathbf{B} \, \mathbf{u} \qquad \qquad \mathbf{y} = \mathbf{C} \, \mathbf{x} + \mathbf{E} \, \mathbf{u} \tag{27}$$

$$A = \begin{bmatrix} \frac{-DR_{P}}{L_{P}} - D \cdot \begin{bmatrix} \frac{R_{S} + (R_{C}//R_{L})}{L_{S}} \end{bmatrix} & \frac{-D \cdot (R_{C}//R_{L})}{N_{S}R_{C}} \\ & \frac{D \cdot (R_{C}//R_{L})}{R_{C}L_{S}C} & \frac{-D}{(R_{C}+R_{L})C} - \frac{D \cdot (R_{C}+R_{L})C}{(R_{C}+R_{L})C} \end{bmatrix}$$

$$B = \begin{bmatrix} \frac{D}{N_{P}} & \frac{-D!}{N_{S}} \cdot (R_{C}//R_{L}) \\ \frac{D(R_{C}//R_{L})}{R_{C}C} + \frac{D!(R_{C}//R_{L})}{R_{C}C} \end{bmatrix}$$

$$C = \begin{bmatrix} \frac{D'N_S(R_C//R_L)}{L_S} & \frac{D(R_C//R_L)}{R_C} + \frac{D'(R_C//R_L)}{R_C} \\ \frac{DN_P}{L_P} & 0 \end{bmatrix}$$

$$E = \begin{bmatrix} 0 & (R_C//R_L) \\ 0 & 0 \end{bmatrix}$$

where D is the steady-state duty cycle and D' = 1 - D.

To simplify our matrix expressions, assume

(1)

$$R_C \ll R_L$$

so that  $R_C / / R_L = R_C$   $R_C + R_L = R_L$

(2)

$$R_{P} = R_{S}$$

$L_{P} = L_{S}$

Also by definition the following conditions are used.

$$L_e = \frac{L_S}{D^{1/2}}$$

$$R_e = \frac{R_S}{D^{1/2}}$$

$$w_0^2 = \frac{1}{L_e C}$$

$D = T_{on} / T_p$

where  $T_{p}$  is the switching period.

$$\zeta = (w_O/2) [(L_e/R_L) + (R_e + R_C/D') C]$$

(28)

Applying these simplifications the average model equations become:

$$A = \begin{bmatrix} -R_{S} - D'R_{C} & & & & \\ & L_{e}(D')^{2} & -\frac{D'}{N_{S}} & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & &$$

$$C = \begin{bmatrix} \frac{N_S R_C}{L_e D^{\dagger}} & 1 \\ \frac{DN_P}{L_P} & 0 \end{bmatrix} \quad E = \begin{bmatrix} 0 & R_C \\ 0 & 0 \end{bmatrix}$$

## 2.3.2 Linearized Power Stage Model

The line voltage variation,  $\tilde{v}_i$ , duty cycle variation,  $\tilde{d}$ , and output current source disturbance,  $\tilde{i}_0$ , are introduced into the circuit such that

$$v_{i} = v_{i} + v_{i}$$

$d = D + d$

$i_{0} = 0 + i_{0}$   $d' = D' - d$

where  $V_{i}$  is the DC input voltage, and D and D' are the steady-state on-time and off-time duty cycle.

Employing the small-signal approximations as described previously, a linear system of equations is obtained as follows:

Steady-state (dc) model equation:

$$\underline{Y} = [V_{O} \quad I_{P}]^{T} = (E - CA^{B}) \underline{U}$$

$$= \begin{bmatrix} DN_{S} & D^{2}L_{e} \\ ---- & ---- \\ D'N_{P} & L_{P}R_{L} \end{bmatrix}^{T} \cdot V_{i}$$

(29)

The input/output transfer function: (assuming the duty cycle variation is zero.)

$$\underline{\underline{y}}(s) = [v_0(s) \ i_p(s)]^T = [C (sI-A) B + E] \underline{\underline{u}}(s)$$

(30)

$$= \frac{\begin{bmatrix} \frac{N_S w_o^2 D}{D'N_p} & (sR_C C + 1) & R_C (s^2 + z_1 s + w_o^2 z_2) \end{bmatrix} \begin{bmatrix} v_i(s) \\ \frac{D^2}{L_p} & (s + \frac{1}{R_L C}) & \frac{-DD'N_p}{L_p N_S C} & (sR_C C + 1) \end{bmatrix} \begin{bmatrix} i_o(s) \end{bmatrix}}{s^2 + 2\zeta w_o s + w_o^2}$$

where  $z_1$  = 2  $w_0$  + 1/( $R_C$  C) - ( $R_C/L_e$ ),  $z_2$  = ( $R_e/R_C$ )+(D/D') Duty cycle/output transfer function: (assuming the input variation is zero.)

$$\frac{z}{y(s)/d(s)} = C(sI-A)^{-1} [(A1-A2)\underline{x} + (B1-B2)\underline{U}] + [(C1-C2)\underline{x} + (E1-E2)\underline{U}]$$

(31)

$$V_{o} = \frac{\left[ \frac{w_{o}^{2}}{DD^{T}} (sR_{C}C+1) \cdot \left\{ 1 - \frac{D}{R_{L}(sR_{C}C+1)} \cdot \left[ \frac{R_{C}}{w_{o}^{2}} s^{2} + \left( \frac{2R_{C}\zeta}{w_{o}} + L_{e} \right) s + \left( R_{e} + \frac{R_{C}}{D^{T}} \right) \right] \right]}{\frac{N_{S}}{N_{p}R_{L}} \left\{ \frac{1}{CL_{S}} (sR_{L}C + 1 + D) + \frac{1}{D^{T}} (s^{2} + 2\zeta w_{o}s + w_{o}^{2}) \right\}}$$

For detailed derivations of the transfer functions, refer to Appendix B.

Further simplifications are made by letting  $\Delta = s^2 + 2\zeta w_0 s + w_0^2$  and then forming the gain expressions. For the input/output transfer functions, the gain block in matrix form is given below:

$$\frac{\tilde{y}}{\tilde{y}}(s) = -\frac{1}{\Delta} \begin{bmatrix} F_{U11} & F_{U12} \\ F_{U21} & F_{U22} \end{bmatrix} \begin{bmatrix} \tilde{v}_{i}(s) \\ \tilde{i}_{o}(s) \end{bmatrix}$$

(32)

For the duty cycle/output transfer function, the matrix simplification expression is given below:

$$\frac{\tilde{Y}(s)}{\tilde{Y}(s)} = -\frac{1}{\Delta} \begin{bmatrix} F_{D1} \\ F_{D2} \end{bmatrix} \tilde{d}(s)$$

(33)

The block diagram for the small-signal model of the fly-back power stage is shown in Figure 10.

Figure 10. Block Diagram of Fly-back Power Stage

#### CHAPTER 3

## ERROR PROCESSOR MODEL

#### 3.1 Introduction

The error processor, EP, is a feedback compensation network. It processes multiple input control signals derived from the power stage, and delivers the required analog information to the pulse-width modulator. The analog signal error processor employed in the present analysis is shown in Figure 11. From a small-signal viewpoint, the error processor is a linear network consisting of two control loops. The signals sensed in these two loops are the converter output voltage,  $v_{\rm O}$ , and the primary winding current of inductor,  $i_{\rm D}$ .

The sensed  $v_0$  is processed by an error amplifier with reference,  $E_r$ , to generate a voltage error signal,  $v_x$ . The voltage error signal, after processing through an integral-plus-lead/lag compensation network, establishes the threshold level for the switching current signal derived from the current sensing loop [5]. The integral-plus-lead/lag compensation network is employed to shape the frequency response to improve the system stability and dynamic response.

The current loop which senses the drain current of the power MOSFET serves two functions. The first function is to transform the primary winding current into a proportional voltage signal. Then, this signal,  $v_{\text{SW}}$ , is

Figure 11. Error Processor

compared with  $\mathbf{v_x}$  and results in a control that turns off the power switch when  $\mathbf{v_{sw}}$  equals to  $\mathbf{v_{x^*}}$ . The second function of the current loop is to derive the low frequency modulation signal or error signal for additional loop compensation.

# 3.2 Voltage and Current Loop Gains

As stated earlier, the current loop contains two types of information. One is the large amplitude switching

current waveform which is used to implement the analog to digital conversion. Such a function is considered a part of the pulse width modulator instead of the error processor. The second type of information contained in the current loop is the small amplitude low-frequency modulation signal, similar to the modulation signal sensed by the voltage loop. This information is brought together with the error signal from the voltage loop and compensation network to provide the total state feedback compensation for improved stability and dynamic response. For the purpose of modeling of the error processor, the large amplitude switching current information should be extracted from the current loop and be incorporated into the pulse width modulator.

In order to model the whole power supply by the three functional blocks: power stage, error processor, and pulse width modulator, the pulse width modulator should take the combined error signal from the error processor output and convert it into duty cycle signal. Furthermore, to implement such a "single-input single-output" pulse width modulator model, various error signals derived from the multiple feedback paths should be combined to form a composite error signal containing error information from voltage, current, and compensation loops.

For reasons mentioned above, the original error processor circuit is modified to that of Figure 12. Figure 12 is a functional equivalent to the original circuit shown in Figure 11. In Figure 12, the noninverting input,  $v_{t}$ , of

the threshold detector contains error signals from all feedback loops. The error voltage,  $v_{\mathsf{t}}$ , is the output of the multiple loop error processor and also serves as the input to the pulse width modulator.

In performing the small-signal analysis of the network shown in Figure 12, the reference  $\mathbf{E}_{\mathbf{r}}$  is replaced by

Figure 12. Equivalent Analytical Circuit of an Error Processor

a short-circuit. Applying KCL at node A yields the following equation:

$$v_a [ (1/R_1) + (1/R_2) + (1/R_3) ] = (v_o/R_1) + (v_b/R_3)$$

(34)

where  $v_a$  is the voltage across  $\text{R}_2$  ,  $v_b$  is the differential input voltage of the operational amplifier, and  $v_o$  is the output voltage.

Applying KCL at node B yields the following equation:

$$v_b[(1/Z_X)+(1/R_3)+sC_3+(1/Z_Y)] = v_x(sC_3+1/Z_X) + (v_a/R_3) + (v_o/Z_Y)$$

(35)

where  $Z_X = R_4 + (1/sC_1)$ , and  $Z_Y = R_5 + (1/sC_2)$ .

The open-loop response of the operational amplifier is A(s), then

$$v_{x} = -A(s) v_{b}$$

(36)

where A(s) =  $-K/[1+(s/w_n)]$

Substituting the above equation into the KCL equations at node A and node B results in the following set of equations:

$$v_a[(1/R_1)+(1/R_2)+(1/R_3)] = (v_o/R_1) - v_x[1/(A(s)R_3)]$$

(37)

$$-v_{x}[(1/A(s))(1/Z_{X} + 1/R_{3} + sC_{3} + 1/Z_{Y}) + (1/Z_{X} + sC_{3})]$$

$$= (v_{a}/R_{3}) + (v_{o}/Z_{Y})$$

(38)

Eliminate the node voltages,  $v_a$  and  $v_b$ , by simultaneously solving the above two equations for  $v_o$  and  $v_x$ . The single expression generated in terms of  $v_o$  and  $v_x$  yields:

$$-v_{x}[(1/A(s)) (1/Z_{X} + 1/R_{3} + sC_{3} + 1/Z_{Y}) + (sC_{3} + 1/Z_{X})]$$

$$= (v_{o}/R_{1}R_{3})(1/R_{X}) - [v_{x}/(A(s)R_{3}^{2}R_{X})] + (v_{o}/Z_{Y})$$

where  $R_{X} = 1/R_{1} + 1/R_{2} + 1/R_{3}$ . Then, (39)

$$-v_{x}\{[(1/A(s))(1/Z_{x} + 1/R_{3} + sC_{3} + 1/Z_{y})] -$$

$$[1/(R_1R_3R_X)] = v_0 \{[1/(R_1R_3R_X)] + (1/Z_Y)\}$$

(40)

Since the expressions for voltage and current loops are low frequency models, the operational amplifier gain is A(s) = -K. With a very large K, the above equation can be simplified to the following form:

$$v_{x} = -v_{0} \{ [1/(R_{1}R_{3}R_{X})] + (1/Z_{Y}) \} / (sC_{3} + 1/Z_{X})$$

(41)

The current loop is described by the following:

$$i_{SW} = i_p/n \tag{42}$$

where n is the turns ratio of the current transformer.

$$v_{SW} = i_{SW} R_{SW} = i_p (R_{SW}/n)$$

(43)

From Figure 12 the following equation is derived:

$$v_t = v_x - v_{sw}$$

Then,

The voltage loop gain for the error processor is defined by the following:

$$F_V = -\tilde{v}_t / \tilde{v}_0 | \tilde{i}_p = 0$$

$$= \frac{1}{s(C_1+C_3)} \cdot \left[ \frac{1+sR_4C_1}{1+sR_4(\frac{C_1C_3}{C_1+C_3})} \right] \cdot \left[ \frac{1+sC_2(\frac{R_5 GQ + 1}{GQ})}{(1+sR_5C_2)} \right] \cdot GQ$$

where  $GQ = 1/\{ [1 + (R_3/R_1) + (R_3/R_2)] R_1 \}$  (45)

The current loop gain is given by the following:

$$F_{C} = -v_{t} / i_{p} / v_{o} = 0$$

$$= R_{SW}/n$$

(46)

Figure 13 illustrates the error processor block diagram.

Figure 13. Error Processor Block Diagram

#### CHAPTER 4

### PULSE WIDTH MODULATOR

# 4.1 Pulse Width Modulator Description

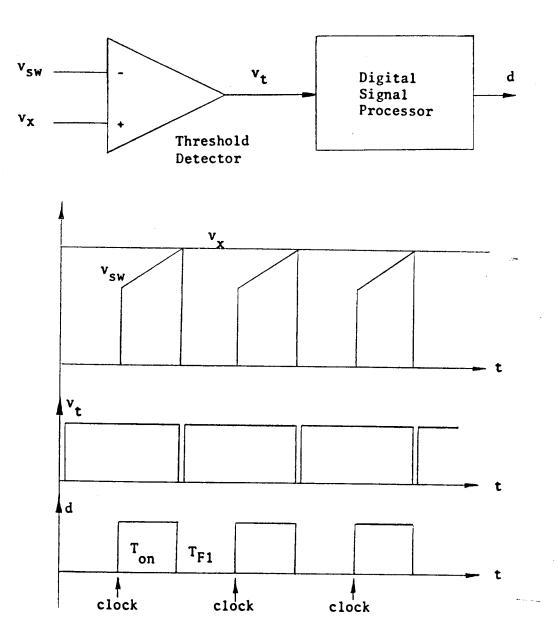

The pulse width modulator converts the analog error signal from the output of the error processor into a modulated pulse train in order to provide proper duty cycle control of the power switch. The pulse width modulator analyzed in this chapter utilizes a constant frequency duty cycle control.

A simplified block diagram of the pulse width modulator is shown in Figure 14. This pulse width modulator is compounded by the unconventional circuit implementation of the threshold detector. In the conventional design, the threshold detector is implemented with a fixed threshold voltage input and the other containing the error information. In this pulse width modulator, both inputs to the threshold detector contain error signals or modulation signals. The two inputs of the threshold detector are  $v_{\rm X}$  and  $v_{\rm SW}$ . The  $v_{\rm X}$  is a floating threshold level proportional to the difference between the desired output and the measured quantity.

Using the constant frequency duty cycle control shown in Figure 14, the clock initiates the on-time and the intersection of  $v_{sw}$  and  $v_x$  marks the termination of the  $T_{on}$  interval. During the on-time interval, the slope of  $v_{sw}$  rises almost linearly with a slope  $S_N$ . The length of the

subsequent off time is determined by the next clock signal of the predetermined interval  $(T_{\mbox{on}}\ +\ T_{\mbox{F1}}).$

## 4.2 Small-Signal Model

To investigate the small signal behavior of the pulse width modulator, an analytical model is developed by using the describing function technique.

Figure 14. Pulse Width Modulator Without Disturbance

Figure 15 shows the block diagram of the analytical model at steady-state without a low frequency disturbance. When  $v_{sw}$  is greater than  $v_x$ ,  $T_{F1}$  commence.  $S_N$  is the rising slope of the switching current signal  $v_{sw}$  during the  $T_{on}$  interval.  $S_F$  is the falling slope determined by the secondary current of the two winding inductor reflected back to the primary during the  $T_{F1}$  interval.

The slopes  $\mathbf{S}_{N}$  and  $\mathbf{S}_{F}$  can be defined by the parameters of the power stage and current sensing loop. During  $\mathbf{T}_{ON}$  interval,

$$V_i = i_p R_p + L_p(di_p/dt)$$

(47)

then,

$$(di_p/dt) = (V_i - i_p R_p)/L_p$$

(48)

The magnitude of  $i_p R_p$  is much less than  $V_{\text{i}}$ , hence

$$(di_p/dt) = V_i/L_p$$

(49)

The current transformer used to sense the switching current reduces the sensing current by a 1:n of the turns ratio in the following expression:

$$(di_{sw}/dt) = V_i/(n L_P)$$

(50)

The signal  $v_{\text{SW}}$  to the threshold detector is a voltage proportional to the current passing through  $R_{\text{SW}}$ ; therefore,

$$S_{N} = (di_{SW}/dt) R_{SW} = (V_{i} R_{SW})/(n L_{p})$$

(51)

Because of the steady state, the initial and final values of the inductor current for each switching cycle must be equal. Integrating the inductor voltage with time over one switching period should be zero. In other words,  $\rm\,S_{N}\,\,T_{ON}$

Figure 15. Unperturbed Analytical Pulse Width Modulator Waveforms

equals  $-S_FT_{F1}$ . This relationship is so-called volt-second balance on the inductor [6]. Thus,

$$- S_F = (T_{on} S_N) / T_{F1} = (T_{on} / T_{F1}) (V_i R_{SW}) / (n L_P)$$

(52)

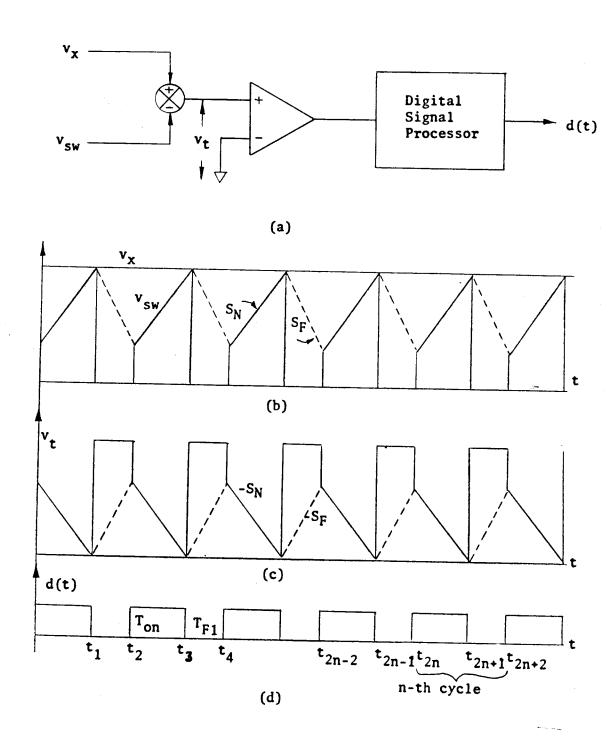

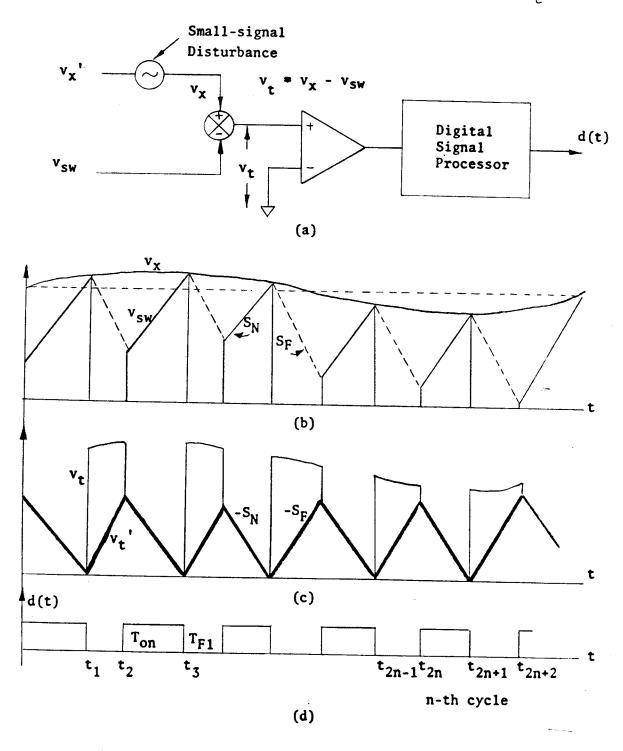

Figure 16 shows the equivalent circuit waveforms for the perturbed case. The small signal disturbance is represented by an ac generator placed in the voltage loop as shown in Figure 16(a). For the perturbed case, the magnitude of the low frequency ac signal is assumed to be sufficiently small and  $S_{\rm N}$  and  $S_{\rm F}$  are considered constant and unaffected by the disturbance.

The development of Figure 16(b) is as follows: given a slope  $S_N$  determined by parameters of power stage and current sensing loop and an initial starting value with a dc value large enough to guarantee continuous operation mode. From the starting point, a line is drawn with the slope  $S_N$ . At the intersection of the perturbed  $v_X$  and the switching current information  $v_{SW}$ ,  $T_{F1}$  begins. The next  $T_{ON}$  will be initiated when the next clock comes, and the switching cycle repeats. The initial point for the next cycle is determined by subtracting the magnitude  $S_FT_{F1}$  from  $v_X$  at that particular point in time. From the new initial values, the above process is repeated.

Figure 16(c) shows the input  $v_t$  to the analytical threshold detector. Using the relation  $v_t = v_x - v_{sw}$ , the waveforms in Figure 16(d) are developed and illustrated for the perturbed duty cycle.

A set of equations are developed for the darkened

trajectory  $v_t$ ' of Figure 16(c).  $v_t$ ' is used because the trajectory describes the low frequency modulation affecting the modulator gain. The additional information in  $v_t$  that

Figure 16. Perturbed Analytical Pulse Width Modulator Waveforms

deals with the dc component of the switching waveform of the converter is not relevant in the modulation of the duty cycle signal; therefore, it has no contribution to the modulator small-signal gain.

# 4.3 Transfer Function of Pulse Width Modulator

The output of the pulse width modulator, which contains a series of pulses of equal amplitude but sinusoidally-varying pulse widths, will have a low frequency content corresponding to the small-signal disturbance frequency. The output of the pulse width modulator can be expressed in a Fourier series in the form:

$$d(t) = D + a_1 \sin wt + b_1 \cos wt + \dots$$

(53)

The input of the pulse width modulator can also be expressed in a Fourier series in the form:

$$v_t'(t) = V + c_1 \sin wt + d_1 \cos wt + ...$$

(54)

Because the low frequency contents of  $v_t$ '(t) and d(t) are of concern, the describing function  $F_M$  of the pulse width modulator is defined as:

$$F_{M} = -\frac{\overset{\sim}{d(t)}}{\overset{\sim}{v_{t}'(t)}} = \frac{(a_{1}^{2} + b_{1}^{2})^{1/2}}{(c_{1}^{2} + d_{1}^{2})^{1/2}} = \frac{\sin \left[wt + (\tan^{-1} b_{1}/a_{1})\right]}{\sin \left[wt + (\tan^{-1} d_{1}/c_{1})\right]}$$

(55)

The resultant waveform  $v_t$  is a function of  $S_N$  and  $S_F$  and the sinusoidal disturbance A sin wt. During the interval  $T_{\text{on}}$  at the n-th cycle {  $t_{2n}$ ,  $t_{2n+2}$  },  $v_t$ ' yields the

following equation:

$$v_{t}'(t) = |S_{N}| (t_{2n+1}-t) + A \sin wt - A \sin wt_{2n+1}$$

During the interval  $T_{F1}$  at the n-1 cycle,  $v_{t}$ ' results in the following:

$$v_{t}'(t) = |S_{F}| (t-t_{2n-1}) + A \sin wt - A \sin wt_{2n-1}$$

The switching period,  $T_p$ , can be found from the following development. Evaluating the above equations,  $v'_t(t)$ , at  $t = t_{2n}$  gives the following:

$$v'_t(t_{2n}) = |S_F|(t_{2n} - t_{2n-1}) + A \sin wt_{2n} - A \sin wt_{2n-1}$$

and (58)

$v'_{t}(t_{2n}) = |s_{N}|(t_{2n+1} - t_{2n}) + A \sin wt_{2n} - A \sin wt_{2n+1}$ Then, (59)

$$|S_F|T_{F1} + A \sin wt_{2n} - A \sin wt_{2n-1} = |S_N|(T_p - T_{F1}) + A \sin wt_{2n} - A \sin wt_{2n+1}$$

(60)

where  $T_{F1} = t_{2n} - t_{2n-1}$ ,  $T_p = t_{2n+1} - t_{2n-1}$ ,  $(t_{2n+1} - t_{2n}) = (T_p - T_{F1})$

Therefore,

$$(|S_F| + |S_N|) T_{F1} - |S_N| T_P = -2A \sin w(T_P/2) \cos w(t_{2n-1} + T_P/2)$$

Making use of the fact that  $\mathrm{wT}_\mathrm{p}$  is very small,

$$\sin w(T_p/2) = w(T_p/2) \tag{62}$$

$$\cos w(t_{2n-1} + T_p/2) = \cos wt_{2n-1}$$

(63)

Thus,

$$(|S_F| + |S_N|)T_{F1} = T_p(|S_N| - Aw \cos wt_{2n-1})$$

(64)

$$T_p = [(|S_F| + |S_N|)T_{F1}]/[|S_N| - Aw \cos wt_{2n-1}]$$

(65)

4.3.1 Derivation of Coefficients  $a_1$  and  $b_1$

The coefficient  $b_1$  can be derived as:

$$b_{1} = w/\pi \int_{0}^{2\pi} d(t) \cos wt dt$$

$$= w/\pi \int_{0}^{t_{1}} \cos wt dt + \int_{t_{2}}^{t_{3}} \cos wt dt + \dots)$$

$$= 1/\pi \left[ \sin wt_{1} + \sin wt_{3} - \sin wt_{2} + \dots + \sin wt_{2n+1} - \sin wt_{2n} + \dots \right]$$

$$= 1/\pi \sum_{n=0}^{N} B_{2n+1}$$

(66)

where

$$B_{2n+1} = \sin wt_{2n+1} - \sin wt_{2n}$$

$$= 2\cos \left[w(t_{2n+1} + t_{2n})/2\right] \sin \left[w(t_{2n+1} - t_{2n})/2\right]$$

$$= 2\cos \left[w(t_{2n-1} + (T_p + T_{F1})/2)\right] \sin \left[w(T_p - T_{F1})/2\right]$$

$$(67)$$

Making use of the fact that  $wT_p$  is very small,

$$\sin [w(T_p - T_{F1})/2] = w(T_p - T_{F1})/2$$

(68)

$$\cos [w(t_{2n-1} + (T_p + T_{F1})/2)] = \cos wt_{2n-1}$$

(69)

Thus,

$$B_{2n+1} = w(T_p - T_{F1}) \cos wt_{2n-1}$$

$$= w/T_p [(T_p - T_{F1}) \cos wt_{2n-1}] T_p$$

(70)

Therefore,

$$b_1 = 1/\pi \left\{ \sum_{n=0}^{N} w/T_p \left[ (T_p - T_{F1}) \cos wt_{2n-1} \right] T_p \right\}$$

(71)

With  $T_p$  small compared to the modulation period,  $2\pi/w$ ,  $b_1$  can be expressed as follows:

$$b_1 = 1/\pi \int_0^{2\pi/w} w \left[1 - (T_{F1}/T_p)\right] \cos wt dt$$

(72)

Since  $T_p = [(|S_F| + |S_N|)T_{F1}]/[|S_N| - Aw \cos wt_{2n-1}]$ , hence

$$b_1 = 1/\pi \int_0^{2\pi/w} w \left[ 1 - \frac{T_{F1}[|S_N| - Aw \cos wt]}{[(|S_F| + |S_N|) T_{F1}]} \right] \cos wt dt$$

$$= w/\pi \int_0^{2\pi/w} \{[A w (\cos wt)^2]/[|S_F| + |S_N|]\} dt$$

$$= \{(A w^2)/[2 (|S_F| + |S_N|)]\} \int_0^{2\pi/w} (\cos 2wt + 1) dt$$

$$= (A w)/(|S_F| + |S_N|)$$

(73)

The coefficient a<sub>1</sub> can be derived as:

$$a_{1} = w/\pi \int_{0}^{2\pi} d(t) \sin wt dt$$

$$= w/\pi \left( \int_{0}^{t_{1}} \sin wt dt + \int_{t_{2}}^{t_{3}} \sin wt dt + \dots \right)$$

$$= 1/\pi \left[ 1 - \cos wt_{1} + \cos wt_{2} - \cos wt_{3} + \dots \right]$$

$$= 1/\pi \sum_{n=0}^{N} A_{2n+1}$$

(74)

where

$$\begin{split} \mathbf{A}_{2n+1} &= \cos \ \mathbf{wt}_{2n} - \cos \ \mathbf{wt}_{2n+1} \\ &= 2 \sin \left[ \mathbf{w}(\mathbf{t}_{2n} + \mathbf{t}_{2n+1})/2 \right] \sin \left[ \mathbf{w}(\mathbf{t}_{2n+1} - \mathbf{t}_{2n})/2 \right] \\ &= 2 \sin \left[ \mathbf{w}(\mathbf{t}_{2n-1} + (\mathbf{T}_p + \mathbf{T}_{F1})/2) \right] \sin \left[ \mathbf{w}(\mathbf{T}_p - \mathbf{T}_{F1})/2 \right] \\ &= (75) \end{split}$$

Making use of the fact that  $wT_p$  is very small,

$$\sin [w(T_p - T_{F1})/2] = w(T_p - T_{F1})/2$$

(76)

$$\sin [w(t_{2n-1} + (T_p + T_{F1})/2] = \sin wt_{2n-1}$$

(77)

Thus,

$$A_{2n+1} = w (T_p - T_{F1}) \sin wt_{2n-1}$$

=

$$(w/T_p)$$

[ $(T_p - T_{F1})$  sin  $wt_{2n-1}$ ]  $T_p$  (78)

Therefore,

$$a_1 = 1/\pi \sum_{n=0}^{N} \{ (w/T_p) [ (T_p - T_{F1}) \sin wt_{2n-1}] T_p \}$$

(79)

With  $T_p$  small compared to the modulation period,  $2\pi/w$ ,  $a_1$  can be expressed as follows:

$$a_1 = 1/\pi \int_0^{2\pi/w} w[1 - (T_{F1}/T_p)] \sin wt dt$$

(80)

Since  $T_p = [(|S_F| + |S_N|)T_{F1}]/[|S_N| - Aw \cos wt_{2n-1}]$ , hence

$$a_1 = 1/\pi \int_0^{2\pi/w} \left[ 1 - \frac{T_{F1}[|S_N| - A \text{ w cos wt}]}{(|S_F| + |S_N|)T_{F1}} \right] \sin \text{wt dt}$$

$$= w/\pi \int_{0}^{2\pi/w} [(A \ w)/(|S_{F}| + |S_{N}|)] \cos wt \sin wt dt$$

$$= 0$$

(81)

# 4.3.2 Derivation of Coefficient $c_1$ and $d_1$

From Figure 16, one has  $v_t$  at  $t = t_{2n}$  as:

$$v_t'(t_{2n}) = |S_F| T_{F1} - A \sin wt_{2n-1} + A \sin wt_{2n}$$

$$= |S_F|T_{F1} + 2A \cos [w(t_{2n} + t_{2n-1})/2] \sin wT_{F1}/2$$

Since wT /2 is were are 11

Since  $wT_{F1}/2$  is very small,

$$\sin wT_{F1}/2 = wT_{F1}/2$$

(83)

Thus,

$$v_t' = |S_F|T_{F1} + A w T_{F1} \cos w[t_{2n-1} + (T_{F1}/2)]$$

From the above equation, the fundamental of the small-signal average of  $v_t$ ' can be taken.

$$v_{t}' = 1/2 \text{ A w } T_{F1} \cos \left[w \left(t + T_{F1}/2\right)\right]$$

(85)

The describing function  $F_{M}$  for the pulse width modulator is:

$$F_{M} = -\frac{\tilde{d}(t)}{\tilde{v}_{t}'} = \frac{(a_{1}^{2} + b_{1}^{2})^{1/2}}{\tilde{v}_{t}'} = \sin \{wt + [tan^{-1}(b_{1}/a_{1})]\}$$

(86)

Substituting for  $a_1$ ,  $b_1$  and  $\tilde{v}_t$  into the equation  $F_M$ , the gain of the pulse width modulator is:

$$F_{M} = \frac{2}{(|S_{N}| + |S_{F}|)T_{F1}} \frac{\sin [wt + \pi/2]}{\cos [w(t + T_{F1}/2)]}$$

Since w is the angluar frequency of the low-frequency modulation and  $T_{\rm F1}$  is the off-time period of the switch, thus

$$wT_{F1}/2 << 1$$

and

$$\sin [wt + \pi/2]$$

$\cos wt$   $\cos [w (t + T_{F1})]$   $\cos [w (t + T_{F1})]$  (88)

$$F_{M} = 2/[(|S_{N}| + |S_{F}|) T_{F1}]$$

(89)

Because

$$|S_{N}| = \frac{V_{i}R_{SW}}{n L_{P}}$$

(90)

$$|S_{F}| = \frac{T_{ON} V_{i}^{R}SW}{T_{F1} N L_{P}}$$

(91)

Therefore,

$$F_{M} = \frac{2 \text{ n } L_{p}}{V_{i} R_{SW} T_{p}}$$

$$(92)$$

Figure 17 is the block diagram for the small-signal gain from the composite error signal,  $\tilde{v}_t$ , to the pulse width modulator output,  $\tilde{d}$ .

Figure 17. Pulse Width Modulator Block

#### CHAPTER 5

#### SIMULATION

#### 5.1 Introduction

Simulation of a physical system is a standard analysis tool used in the evalution of hardware design prior to actual construction. Even though the small-signal model or a mathematic model of a system is developed, examining the performance characteristics of that system without a computer becomes a tedious and time consuming task. In the case of the complicated model, calculations by hand are impossible.

Because the small-signal model of this fly-back switching power supply is derived by using s-plane or Laplace transform techniques, this model can be expressed by a set of linear transfer functions or linear equations. Many computer program packages designed to solve any linear equations and transfer functions are available now. Among those packages for solving such a problem is "LISA 360 A Program for Linear System Analysis (LISA 360)", a well-known computer program package developed by IBM. The LISA 360 program package can be used to compute the following solutions:

- (a) Pole and zero locations

- (b) Time response to a step or sinusoidal inputs

- (c) Bode response over a range of frequencies

- (d) Sensitivity of a function to component variations

at a given frequency

A LISA 360 program has been coded to examine the following performance characteristics of this power supply model:

- (1) The audio-susceptibility characteristics  $G_A = v_o/v_i$

- (2) The output impedance characteristics  $Z_0 = \tilde{v}_0/\tilde{i}_0$

- (3) The system loop gain characteristics [7]

$$T = \frac{1}{\Delta} - F_{M} (F_{V}F_{D1} + F_{C}F_{D2})$$

(93)

The system loop gain characteristics T are used to examine the relative stability of the system.

# 5.2 Simulations of Audio-Susceptibility and Output Impedance

Audio-susceptibility [8] is the closed-loop, input/ output response for the switching power supply. The audiosusceptibility characteristic is used to evaluate the rejection ratio of the propagation of a sinusoidal disturbance from the input voltage to the output voltage. The audio-susceptibility is defined as:

$$G_{A} = \tilde{v}_{O}/\tilde{v}_{i} \tag{94}$$

The output impedance is employed to measure the dynamic performance of a switching power supply subjected to sinusoidal load disturbance. A switching power supply with zero output impedance represents an ideal voltage source. The output impedance of the switching power supply is defined as:

$$Z_{O} = \tilde{v}_{O}/\tilde{i}_{O} \tag{95}$$

In linear systems, the output impedance is often used to analyze transient response. When a switching power supply is subjected to a small step-change of the load, the output voltage normally only varies slightly.

## 5.2.1 Equation Formulations

Many methods can be used to set up the describing equations of the small-signal model of this switching power supply. One of the equation formulations, which LISA 360 program package uses, is the "matrix" option. According to the input language of LISA 360, the system equations should be written in the following form if the "matrix" option is used.

$$W(s) \quad Y(s) = U(s) \tag{96}$$

where W(s) is the nodal admittance matrix or the system dynamics, Y(s) is the unknown node-voltage or output vector, and U(s) is the vector of sources plus initial conditions.

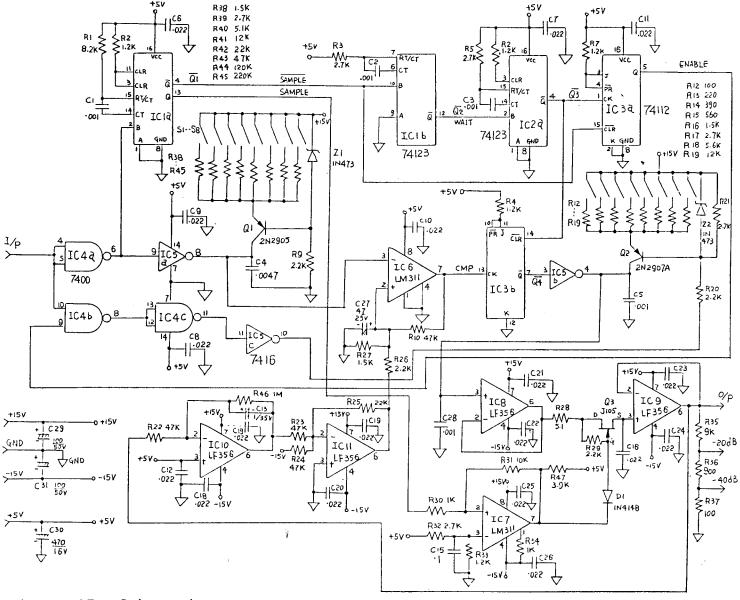

From the previous chapters, the fly-back power stage, error processor, and pulse width modulator small-signal model can be incorporated into a closed-loop block diagram as shown in Figure 18. The input-output equations are derived as follows:

$$\tilde{\mathbf{y}}(\mathbf{s}) = \left\{ \begin{bmatrix} \mathbf{F}_{U11} & \mathbf{F}_{U12} \\ \mathbf{F}_{U21} & \mathbf{F}_{U22} \end{bmatrix} \begin{bmatrix} \tilde{\mathbf{v}}_{\mathbf{i}}(\mathbf{s}) \\ \tilde{\mathbf{i}}_{\mathbf{o}}(\mathbf{s}) \end{bmatrix} + \begin{bmatrix} \mathbf{F}_{D1} \\ \mathbf{F}_{D2} \end{bmatrix} \tilde{\mathbf{d}}(\mathbf{s}) \right\} \frac{1}{\Delta} = \begin{bmatrix} \tilde{\mathbf{v}}_{\mathbf{o}}(\mathbf{s}) \\ \tilde{\mathbf{i}}_{\mathbf{p}}(\mathbf{s}) \end{bmatrix}$$

(97)

Figure 18. Small-signal Block Diagram of a Fly-back Switching Mode Power Supply

$$\Delta \tilde{\mathbf{y}}(\mathbf{s}) = \begin{bmatrix} \mathbf{F}_{U11} & \mathbf{F}_{U12} \\ \mathbf{F}_{U21} & \mathbf{F}_{U22} \end{bmatrix} \begin{bmatrix} \tilde{\mathbf{v}}_{\mathbf{i}}(\mathbf{s}) \\ \tilde{\mathbf{i}}_{O}(\mathbf{s}) \end{bmatrix} - \begin{bmatrix} \mathbf{F}_{D1} \\ \mathbf{F}_{D2} \end{bmatrix} \mathbf{F}_{\mathbf{M}} \begin{bmatrix} \mathbf{F}_{\mathbf{V}} & \mathbf{F}_{\mathbf{C}} \end{bmatrix} \tilde{\mathbf{y}}(\mathbf{s})$$

$$\left\{ \Delta \mathbf{I} + \begin{bmatrix} \mathbf{F}_{D1} \\ \mathbf{F}_{D2} \end{bmatrix} \mathbf{F}_{\mathbf{M}} \begin{bmatrix} \mathbf{F}_{\mathbf{V}} & \mathbf{F}_{\mathbf{C}} \end{bmatrix} \right\} \tilde{\mathbf{y}}(\mathbf{s}) = \begin{bmatrix} \mathbf{F}_{U11} & \mathbf{F}_{U12} \\ \mathbf{F}_{U21} & \mathbf{F}_{U22} \end{bmatrix} \begin{bmatrix} \tilde{\mathbf{v}}_{\mathbf{i}}(\mathbf{s}) \\ \tilde{\mathbf{i}}_{O}(\mathbf{s}) \end{bmatrix}$$

$$(99)$$

Therefore,

$$\begin{bmatrix} \Delta + F_{D1}F_{V}F_{M} & F_{D1}F_{C}F_{M} \\ F_{D2}F_{V}F_{M} & \Delta + F_{D2}F_{C}F_{M} \end{bmatrix} \begin{bmatrix} \tilde{v}_{O}(s) \\ \tilde{i}_{D}(s) \end{bmatrix} = \begin{bmatrix} F_{U11} & F_{U12} \\ F_{U21} & F_{U22} \end{bmatrix} \begin{bmatrix} \tilde{v}_{i}(s) \\ \tilde{i}_{O}(s) \end{bmatrix}$$

Note that the negative power of s is not allowed in LISA 360, so the equations must be rationalized. Thus,

$$\begin{bmatrix} D(s) \left[ \Delta + F_{D1}F_{V}F_{M} \right] & D(s) \left[ F_{D1}F_{C}F_{M} \right] \\ D(s) \left[ F_{D2}F_{V}F_{M} \right] & D(s) \left[ \Delta + F_{D2}F_{C}F_{M} \right] \end{bmatrix} \begin{bmatrix} \tilde{v}_{O}(s) \\ \tilde{i}_{D}(s) \end{bmatrix} = \begin{bmatrix} D(s)F_{U11} \\ D(s)F_{U21} \end{bmatrix} \tilde{v}_{i}(s)$$

assume that  $\tilde{i}_{O}(s) = 0$ . (101)

$$\begin{bmatrix} D(s) \left[\Delta + F_{D1}F_{V}F_{M}\right] & D(s) \left[F_{D1}F_{C}F_{M}\right] \\ D(s) \left[F_{D2}F_{V}F_{M}\right] & D(s) \left[\Delta + F_{D2}F_{C}F_{M}\right] \end{bmatrix} \begin{bmatrix} \tilde{v}_{O}(s) \\ \tilde{i}_{D}(s) \end{bmatrix} = \begin{bmatrix} D(s)F_{U12} \\ D(s)F_{U22} \end{bmatrix} \tilde{i}_{O}(s)$$

assume that  $\tilde{v}_{i}(s) = 0$ . (102)

where

$$D(s)=s[1 + (sR_4C_1C_3)/(C_1 + C_3)] (1 + sR_5C_2)$$

The form of the above equations meets the input requirement of LISA 360 for the matrix option. Once the power supply parameters and operating conditions are given, each coefficient in the nonzero elements of the above matrices must be calculated. Then, following the command descriptions and directions, each nonzero element of the matrices should be coded into the LISA simulation program.

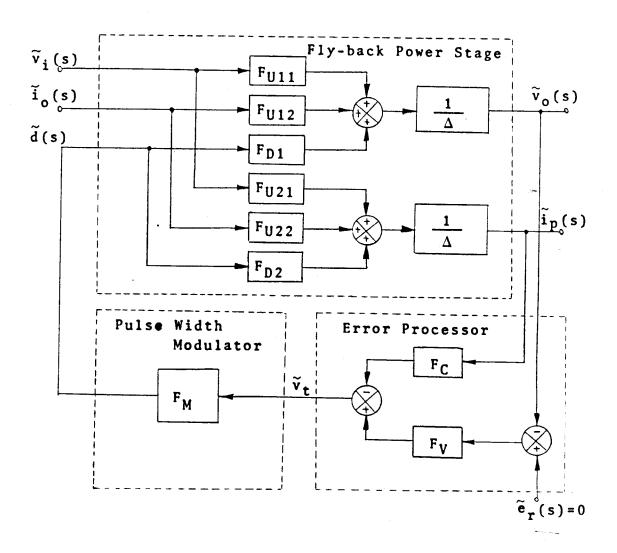

# 5.2.2 Simulation Results of Audio-susceptibility and Output Impedance

A Bode plot establishing the gain and phase of each particular transfer function is shown. The gain and phase plots for the audio-susceptibility and output impedance analysis employ the following power supply parameters and operating conditions. The simulation can be performed by substituting these parameters into equation (101) and (102).

| $V_i = 130V$                       | $C_1 = 0.06 \mu F$        |

|------------------------------------|---------------------------|

| $V_O = 6V$                         | $C_2 = 0$                 |

| $R_{\mathbf{P}} = 0.3 \text{ ohm}$ | $C_3 = 120pF$             |

| N <sub>P</sub> = 68 Turns          | $R_1 = 1 K \text{ ohm}$   |

| $N_S = 3 \text{ Turns}$            | $R_2 = 5K \text{ ohm}$    |

| $R_S = 0.01 \text{ ohm}$           | $R_3 = 4.7K \text{ ohm}$  |

| $R_C = 0.0175 \text{ ohm}$         | $R_4 = 22K \text{ ohm}$   |

| C = 1880µF                         | $R_5 = 0$                 |

| $R_{L} = 0.75 \text{ ohm}$         | R <sub>SW</sub> = 250 ohm |

| $T_P = 16.67 \mu S$                | n = 120 Turns             |

| $L_P = 2.929mH$                    | D = 0.5                   |

| $L_S = 6.239 \mu H$                | D' = 0.5                  |

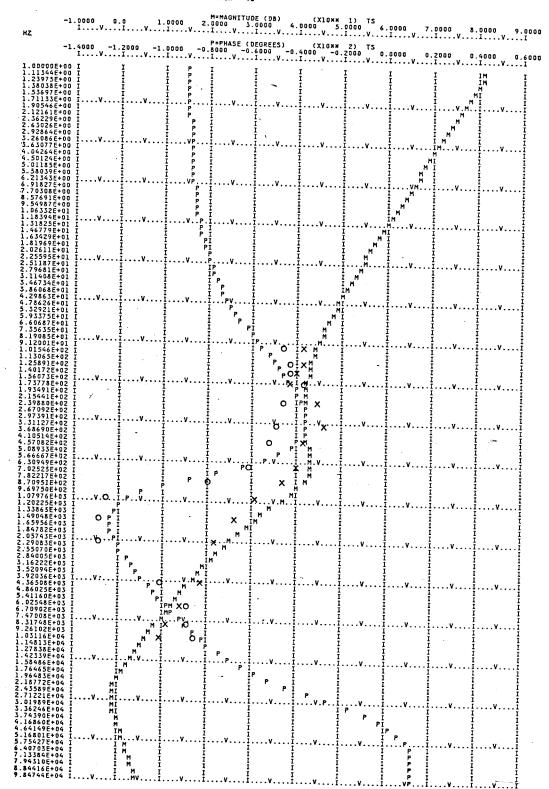

Figure 19 illustrates the Bode plot for audio-susceptibility, and Figure 20 illustrates the Bode plot for output impedance. Moreover, the detailed expressions for calculation of coefficients in each element of matrices, a FORTRAN program designed to accept the circuit parameters and then to calculate those coefficients, and the LISA

Figure 19. Bode Plot for Audio-susceptibility

Figure 20. Bode Plot for Output Impedance Note that  $Z_{O}$  ( $\Omega$ ) = Anti-log [ M (DB) /20]

simulation program are presented in Appendix C.

# 5.3 The System Loop Gain Characteristics

The system loop gain characterizes the power supply's stablity. Because of the multiple feedback paths of this power supply, the loop gain that is defined at the pulse width modulator, which is the common part to all the feedback paths, is a unique loop. Figure 21 shows the block diagram for the system loop gain, and the equation of the system loop gain can be derived. The resultant equation is given below:

$$T = \frac{1}{\Delta} - F_{M}(F_{V}F_{D1} + F_{C}F_{D2})$$

(103)

Substituting the circuit parameters and operating conditions of power supply into the above equation, each coefficient in the numerator and the denominator of the system loop gain, T, can be obtained. Then, according to the command description and direction of "READ function name" in LISA 360, those coefficients are coded into the LISA simulation program. The detailed expression and LISA program are shown in Appendix C.

After simulation, the pole and zero locations of the system loop gain are given below:

Zeros:

-7.311477E2 -9.394725E4 + j1.356394E5 -1.578442E4 -9.394725E4 - j1.356394E5 Poles:

0.0 -1.857252E3 + j4.226668E3 -3.795455E5 -1.857252E3 - j4.226668E3

Total multiplier = 1.90810

Figure 21. Block Diagram for The System Loop Gain

Figure 22 shows the Bode plot of the system loop gain. From this plot, it is interesting to point out that high gain, wide-bandwidth, and stable operation could be accomplished simultaneously. This characteristic has made the multiple

loop control unique in comparison with the single loop control in switching mode power supply.

Figure 22. Bode Plot for The System Loop Gain

#### CHAPTER 6

#### **MEASUREMENT**

6.1 Loop Gain Measurement And Analog Modulation Technique[9]

To analyze the dymanics of a switching mode power supply, the system loop gain method has been widely used because the system loop gain can directly compute the characteristic roots of the system. It is easy to derive the loop gain of a system from a system block diagram or an equivalent circuit model, and the loop gain can provide physical insight into the closed loop system. The stability can be determined by applying the Nyquist criterion, and it is easy to shape the Bode Plots of the loop gain for design purposes to achieve better stability and dymanics of a system.

Even though the most attractive feature is that the loop gain can be measured accurately and quickly in laboratory, the conventional measuring method still has some difficulties to perform within a switching mode power supply employing multi-loop control. For this power supply, loop gains become rather complicated functions, and each loop gain is not uniquely defined. Therefore, the adequacy and accuracy of the loop gain measurement become a very important concern.

The conventional loop gain measurement technique, analog modulation scheme, has been widely used in various types of linear feedback system. In the analog modulation

scheme, a sinusoidal disturbance signal, Vz, is inserted in the feedback loop and the forward and returned signals, Vx and Vy respectively, are measured as shown in Figure 23. The loop gain is then determined by the ratio of the forward and returned signals at the frequency of the inserted signal.

Figure 23. Conventional Analog Modulation Scheme

Because the analog modulation technique inserts and measures the analog signal, its application is limited to the case for which the waveform of the disturbance is smooth and well behaved. In the switching mode power supply, the waveform of the disturbance is of a discontinuous nature and is pulse width modulated. In this case, an analog disturbance signal cannot be inserted into the digital signal for loop gain measurement. In addition, when a PWM ripple component from the ESR of the output filter capacitors is superimposed on the inserted sinusoidal disturbance, the analog modulation scheme gives inaccurate results.

# 6.2 Consideration of Loop Gain Measurement in Switching Power Supply

In the switching power supply employing multiple loop control, not only the derivations of the loop gain are complex, but also the interpretations of the loop gain are not obvious as for a single loop system. However, switching power supply feedback systems are unique in that because the duty cycle is the only control input, all the feedback loops must meet at one point, the duty cycle modulator. The loop gain that is defined at the duty cycle modulator is a unique loop in this multiple loop switching power supply.

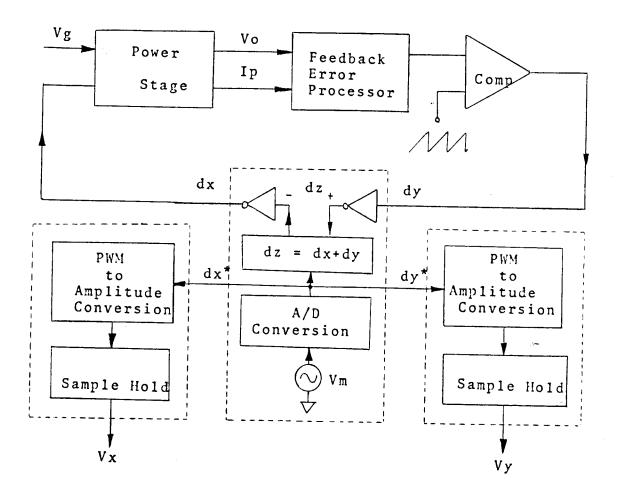

## 6.3 Digital Modulation Technique

The conventional analog modulation scheme has some limitations when a sinusoidal distrubance is inserted into the feedback loop at the point where the waveform is not smooth and well behaved. These limitations can be overcome by inserting, instead, a digital modulation signal that directly modulates the switching power supply's duty cycle. Similar to the analog modulation technique in which a disturbance signal is inserted in the feedback path to generate the forward and returned signals, the digital modulator inserts a digitally modulated disturbance, dz, into the digital signal feedback path while maintaining the loop closed, as shown in Figure 24. Then the KVL satisfies

$$dz = dx + dy (104)$$

and the loop gain is given by: T = dy / dx

Figure 24. Digital Modulation Scheme

## 6.3.1 The Digital Modulator

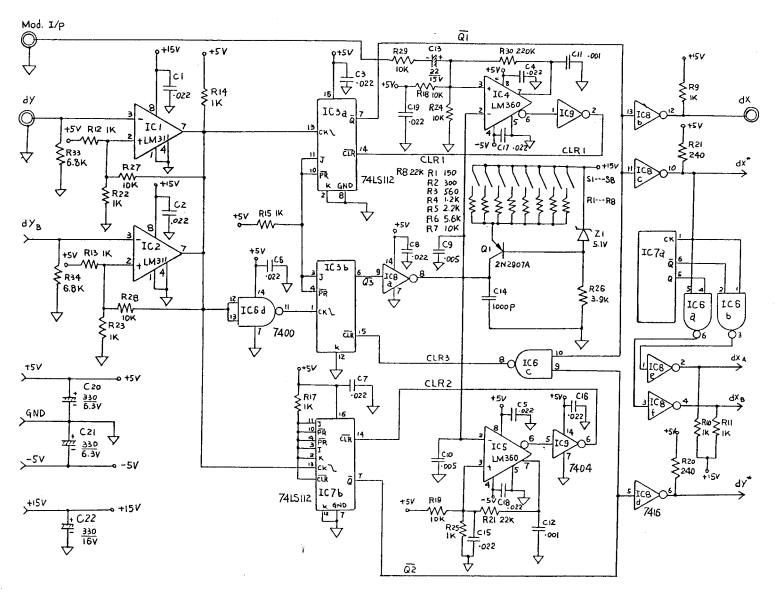

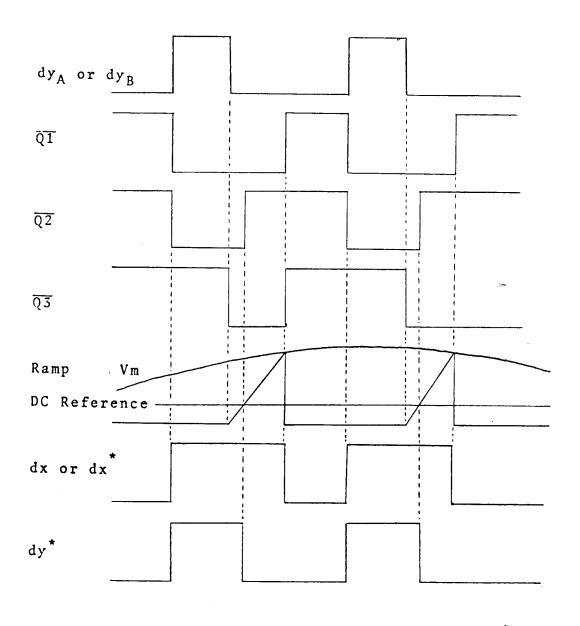

The schematic for the digital modulator is shown in Figure 25. The functional description with the important waveforms in Figure 26 is given as follows.

The modulator accepts one or two inputs,  $\mathrm{d}y_A$  and  $\mathrm{d}y_B$ , depending on whether the duty cycle modulator under test is single-ended or push-pull. These signals are buffered by comparators  $\mathrm{IC}_1$  and  $\mathrm{IC}_2$  which invert and wire-or the inputs. When either of the inputs go high, JK flip-flop  $\mathrm{IC}_{3a}$  and  $\mathrm{IC}_{7b}$  are clocked and set. The inverted output of these flip-flops are the input to the open collector

Figure 25. Schematic of The Digital Modulator

inverters  $IC_{8b}$ ,  $IC_{8c}$ , and  $IC_{8d}$ . The outputs of these inverters supply the drive signal, dx, of the power stage in switching mode power supply and provide the two measurement signals,  $dx^*$  and  $dy^*$ .

Figure 26. Waveforms in The Circuit Schematic of Figure 25